## LDMOS の信頼性モデリングにおける HiSIM-HV モデルを

# 用いたオン抵抗の劣化モデルの開発

戸塚 拓也\* 青木 均 築地 伸和 香積 正基 東野 将史 澁谷 将平 栗原 圭汰 小林 春夫 (群馬大学) キーワード: LDMOS, トランジスタ, モデリング, ホットエレクトロン, 劣化, HiSIM·HV (LDMOS, Transistor, Modeling, Hot Electron, Degradation, HiSIM·HV)

### 1. 研究背景

現在、パワーデバイスは車載用やアンプといった様々な用途で使用されている。その中で、高耐圧であり高温、高電圧、高電流下で使用できる Laterally Diffused MOS (LDMOS)は注目されている。LDMOS とは、ドレイン領域を横方向に拡張することによりドレインとゲート間の電界強度を緩和する構造をした MOS トランジスタであり、オン抵抗が低いことが特徴である。しかし、高電圧、高電流化で長時間使用するとオン抵抗の増加し、低電流下で使用している Metal Oxide Semiconductor MOS(MOSFET)より経時・温度劣化が顕著に見ることができる。これらの劣化を予測し、シミュレーションを用いて表すことで信頼性を高めることができる。[1]

n チャネル MOSFET の経時,温度劣化には,飽和領域の高ドレイン電流において起こる,Hot Carrier Injection (HCI)や正の電圧ストレスを長時間かけることで発生するPositive Bias Temperature Instability (PBTI)現象がある.LDMOS においても,同じ現象で劣化が起こると考えられ,より支配的であるHCI 現象に着目し本研究を進めている.

本発表では、DC バイアスによる HCI 劣化現象を回路シミュレータ SPICE で回路設計者がシミュレートし、劣化前、劣化後の直流電圧・電流特性を事前に予想できるよう、劣化要因の解析を行い既存のモデルに劣化要因を組み込むことで表現できるように研究を進めている。本研究では、米国CMC 推奨モデルの HiSIM・HV を用い、オン抵抗モデルパラメータに方程式を埋め込み経時劣化をシミュレートした結

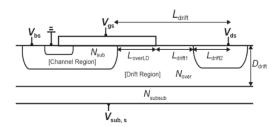

図 1 LDMOS の構造 [2] Fig.1 Schematic of a LDMOS

果を報告する.

## 2. LDMOS の基本構造と HiSIM-HV モデル

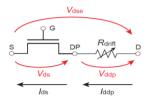

図 1 に LDMOS の基本構造,図 2 に HiSIM・HV モデルにおける LDMOS モデルのコンセプトを示す.LDMOS の最も重要な特徴は高耐圧を実現するために導入されたドリフト領域にある.LDMOS におけるキャリアはソースから供給され,チャネル領域の反転層を通じて拡散した後,ドリフト領域からドリフトによってドレインへ到達する.このときドレイン・ソース間に印加される電圧の大部分はドリフト領域で電圧降下する.図 2 のように HiSIM・HV モデルでは LDMOS のドリフト領域を抵抗としてモデル化している.HiSIM・HV モデルにおけるドリフト領域の抵抗  $R_{drift}$  は式 (1)~(3)のように定義されている[2].ここで,ボールドフォントで示した変数はモデルパラメータである.

$$R_{drift} = (R_{\rm d} + V_{\rm ds} + R_{\rm DVD}) \left( 1 + \text{RDVG11} - \frac{\text{RDVG11}}{\text{RDVG12}} \cdot V_{\rm gs} \right) \cdot (1 - V_{\rm bs} \cdot \text{RDVB}) \cdot \left( \frac{\text{LDRIFT1} + \text{LDRIFT2}}{\text{DDRIFT} - W_{\rm den}} \right) \tag{1}$$

$$R_d = \frac{R_{\text{d0}}}{W_{\text{eff,LD}} \cdot \text{NF}} \left( 1 + \frac{\text{RDS}}{(W_{\text{gate}} \cdot 10^6 \cdot L_{\text{gated0}} \cdot 10^6)^{\text{RDSP}}} \right)$$

(2)

$$R_{d0} = (\mathbf{RD} + R_{d0,\text{temp}}) f_1 \cdot f_2 \tag{3}$$

図 2 LDMOS モデルのコンセプト [2]

Fig.2 LDMOS Model concept in HiSIM-HV

#### 3. LDMOS の劣化

現在, Hot Carrier Injection によるオン抵抗劣化が劣化の 主な原因と考えられている. HCI 現象は Luck Electron Model (LEM) に基づき [3], カリフォルニア大学バークレイ 校 (UCB) の Hu 教授によって最初に導入された[4]. 一般的 ゲート電圧により, 反転層が形成されてキャリアが移動し, ピンチオフした飽和領域においてドレイン電界により加速 されたキャリアは、高いエネルギーを持ったホットキャリア となる. 加速されたホットキャリアは、反転層のイオンと衝 突し,電離衝突が起こる.これにより電子・正孔対が発生す る. 発生したホットキャリアの一部は、酸化膜にトラップさ れ、酸化膜の劣化を引き起こす. キャリアがトラップされる ことによって、キャリアが減少しオン抵抗が増加する. これ により、移動度の減少によるドレイン電流 Loの低下や、しき い値電圧 VTHの増加を引き起こす. 後に発表された HCI モデ ルは、Hu 教授と同じ理論に基づいているが、異なる分析方法 を考察し、より高度な CMOS 技術にモデルを適用することを 意図している.LDMOS の HCI 劣化現象に関する文献[5]による と, n チャネル LDMOS における "HCI による劣化現象は, ド リフト層のキャリア減少からのオン抵抗増加による"と報 告されており、文献[6]、[7]などでオン抵抗の HCI 劣化モデ ルが報告されている.

報告されている論文によるとHCIによるオン抵抗劣化は 以下のように表すことができる[6].

$$\frac{\Delta R_{on}}{R_{on}} = A_1 \ln \left( 1 + \frac{t}{\tau} \right) + A_2 * \ln \left( 1 + \frac{1}{\gamma * \tau} \right) \tag{4}$$

この式は経験的なものである.  $A_1$ ,  $A_2$ ,  $\gamma$ はフィッテングパラメータとなっている. tはストレス時間である.  $\tau$ は特性時間でありバイアスと形状に依存するパラメータであり式(5)で表される.

$$\tau = \frac{\alpha \cdot W}{I_D} \cdot \frac{\phi_b}{E_{m*\lambda}} \cdot e^{\frac{\phi_b}{E_{m'\lambda}}} \tag{5}$$

$\alpha$ はデバイス固有の経験的なフィッテングパラメータである. Wはデバイスの幅,  $E_m$ はピーク電界の大きさである.  $\phi_b$ は  $S_{i}$ ・ $O_2$  のエネルギー障壁を乗り越えるために必要なエネルギーである.  $\lambda$ はキャリアが散乱しエネルギーを失う前に電場に届く平均を表し式(6)で表している.

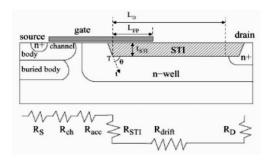

図3 STIを用いた LDMOS の構造[5]

Fig.3 Schematic of a LDMOS using the STI [5]

$$\lambda = \lambda_0 \cdot \tanh\left(\frac{E_p}{2 \cdot k_B \cdot T_i}\right) \tag{6}$$

$E_p$ は Si 中の光学フォノンエネルギーである(0.063 eV).  $k_B$ はボルツマン定数であり(8.62\*10E-5 eV/K), $T_j$ は接合温度である.  $\lambda_0$ は K=0 でのホットキャリアの平均移動速度である. 式(4)~(6)よりオン抵抗の劣化が  $E_m$ に関係いていることから関係性を述べた論文も報告されている. [8]

しかし、我々の検証と調査により Si-H excitation (m)が起こったときに、上記関係が崩れることがあるため、以下のように自由度を持たせた方程式を用いる.

$$\tau = \left(\frac{\alpha * W}{I_D}\right)^m * \frac{\phi_b}{E_m * \lambda} * e^{\frac{\phi_b}{E_m * \lambda}}$$

(7)

## 4. 劣化モデルの開発

我々は、既存のコンパクトモデルであるHiSIM-HVに劣化を 組み込むことを目標としている。そこで、オン抵抗とHiSIM-HVのドリフト関数を対応させ、劣化を表現する。

ここでは HiSIM-HV モデルで対象としている構造とは多少異なり、STI を用いて電流を深い層に流し耐圧を上げた構造である図 3 を用いて、オン抵抗と HiSIM-HV のドリフト関数を対応させる[5]. STI とは、Shallow Trench Isolation のことでありより耐圧を上げるためのものである。オン抵抗は式(8)のように二つの項に分けることができる。

$$R_{drift} = R_{drift,1} + R_{drift,2} \tag{8}$$

$R_{drift,1}$ は、ゲート下の蓄積領域を $R_{drift,2}$ は $R_{drift,1}$ 以降にあるドリフト領域及びドレイン端に対応している。 $R_{drift,1}$ では蓄積領域のオン抵抗とシート抵抗が並列接続されているため、式(9)のように表すことができる。

$$R_{drift.1} = \left(\frac{1}{R_{drift,acc}} + \frac{1}{R_{drift,sh}}\right)^{-1}$$

(9)

また、 $R_{drift,acc}$ は式(10)のように表される。

$$R_{drift,acc} = \frac{L_{FP,eff}}{\left(\mu_{eff}C_{STI}W(V_{GS} - V_{fb})\right)}$$

(10)

$C_{STI}$  は $^{\epsilon_{ox}}/_{t_{STI}}$ であり、 $t_{oSTI}$ は STI 酸化膜の厚さである.

$L_{FP,eff}$ は実行フィールドプレート( $L_{FP}$ )であり、 $V_{fb}$ はフィッテングパラメータである。シート抵抗は式(11)のように表すことができる。

$$R_{drift,sh} = \frac{L_{FP}}{\left(q\mu_n N_d W t_{eff}\right)} \tag{11}$$

$\mathbf{t}_{eff}$ は STI の実効的な深さである.  $R_{drift,2}$ は、式(12)のように表される.

$$R_{drift,2} = \frac{(L_D - L_{FP})}{(q\mu_n N_d W t_{eff})}$$

(12)

$L_D$ は実行ドリフト長である.

ここから、式(8)~(12)を用いて HiSIM-HV のドリフト式 である式(1) $\sim$ (3) $\sim$ の対応を論じる.  $R_{drift,1}$ において $R_{drift,sh}$ にはバイアスは存在しないが、 $R_{drift,acc}$ には $V_{GS}$ 項が存在す る. そのため、HiSIM-HV のドリフト関数、式(1)において VGS が依存する項と関係があることがわかる. RDVG11 また は RDVG12 を用いて, $R_{drift,1}$ を劣化させることができる.  $R_{drift,2}$ においては、 $V_{DS}$ ,  $V_{GS}$ といった項が存在しないが、ド リフト領域及びドレイン端での抵抗を示している. 文献[9]よ り、フィールドプレート下では強い電界が発生していること が判明している. その結果, 強電界の影響を受けHCI効果に よって劣化が生じる. これは、ホットキャリアとなったキャ リアがSTIにトラップし電流量が変化し、ドレインコンタク ト抵抗の劣化に繋がる.式(12)では移動度を表すunが劣化し、 HiSIM-HVではLDDのドレインチャネル抵抗とコンタクト 抵抗を表すRDに劣化が相当すると考えられる. これは、後述 する測定データを使用したモデリング結果とも合致してい る.以上から、オン抵抗劣化はHiSIM-HVにおける、 RD,RDVG11,RDVG12のパラメータを用いて表現すること ができると言える. RDVG11及びRDVG12は、RDにおける VGSの依存性を表している.

## 5. モデルパラメータ抽出及びシミュレーション

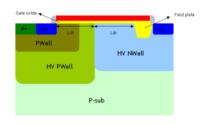

ここでは文献[10]で報告されている直流電流・電圧特性を数値化し、測定データとした。図4は測定に使用されたnチャネルLDMOSの断面図である。このnチャネルLDMOSはプロセス幅0.18umで作成され、ゲート長は20um、ゲート幅は0.4um、ゲート酸化膜圧は115Åである。

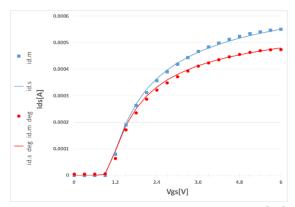

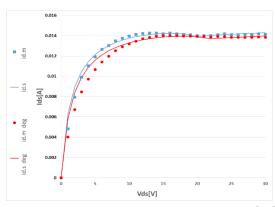

図5及び6は、文献[10]における $I_{ds}$ - $V_{gs}$ 特性と $I_{ds}$ - $V_{ds}$ 特性を数値化したものである。パラメータ抽出ソフトを用いて、測定値とシミュレーション結果の合わせこみを行なった。青色の四角点線が劣化前、赤色の丸点線劣化後の測定値を表している。青色の実線が劣化前、赤色の実線が劣化後のシミュレーション結果を表している。測定値との誤差は二乗平均平方根であるRMSエラー値を用いて表され、5[%]を切ることを目指している。 $V_{ds}$ が2.4 V(飽和領域の電圧)の $I_{ds}$ - $V_{gs}$ 特性での劣化前後を観ると、しきい値の変化は無くドレイン電流 $I_{ds}$ - $V_{ds}$ 特性での劣化前後の特性を観ると、飽和領域のドレイン電流は変化せずに、ピンチオフ領域のみ

変化していることが分かる. 劣化シミュレーションの合わせこみは、前述したようにオン抵抗とHiSIM-HVのドリフト関数を対応させる. そのために、RD、RDVG11、RDVG12のパラメータのみを使用して、劣化前のパラメータ抽出結果を用いて抽出を行った. 抽出結果、RD、RDVG12のみを使用して合わせこむことができた.

RDは1.076mから1.301mに増加、RDVG12は6.026から9.081に増加させ劣化抽出を行った.

図4 測定に用いた n チャネル LDMOS の断面図 [10] Fig.4 Schematic cross section of the n-type LDMOS transistor used in [10]

図 5 HCI 劣化前・劣化後の Ids vs Vgs 特性 [10]

Fig.5 Ids vs Vgs characteristics of an n-type LDMOS before and after hot-carrier induced degradation.

図 6 HCI 劣化前・劣化後の Ids vs Vds 特性 [10]

$\label{eq:fig.6} Fig. 6 \quad I_{ds} \ vs \ V_{ds} \ characteristics \ of \ an \ n\mbox{-type} \ LDMOS \\ before and after hot-carrier induced degradation.$

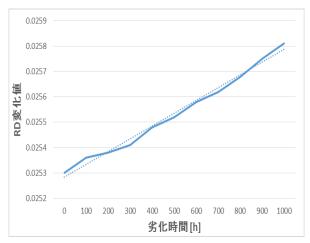

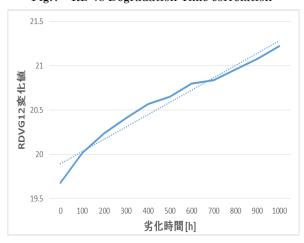

論文データからは、劣化した結果しか見ることができない。 そこで、論文に使用されているデバイスと同様の構造を持つ LDMOSを入手し、劣化測定を行い劣化時間とパラメータ変化の相互関係を検証した。使用したデバイスは、RENESAS社のNE5550779Aである。測定条件は、下記の通りである。  $I_{ds}$ - $V_{gs}$ 測定は、 $V_{gs}$ =0~5[V]かつ $V_{ds}$ =50~150[mV]であり50[mV]ステップである。  $I_{ds}$ - $V_{ds}$ 測定は、 $V_{gs}$ =2.1~2.5[V]であり0.1[V]ステップかつ $V_{ds}$ =0~5[V]である。 温度は室温である。 ストレスバイアスは $V_{gs}$ =2.4[V]、 $V_{ds}$ =2.4[V]で劣化時間は2[h]ごとに1000[h]まで測定を行った。 我々が測定したデータにおいても、 RDとRDVG12を使用することで劣化抽出を行うことができた。 RDは25.30mから25.81mに増加、RDVG12は19.68m0521.22に増加させ劣化抽出を行い、論文データと同じように二つのパラメータを増加させることで劣化抽出を行うことができた。 図7、図8は劣化時間と二つのパラメータの変化値の相関をグラフ化したものである。

図7 RDと劣化時間の相関関係

Fig.7 RD vs Degradation Time correlation

図8 RDVG12と劣化時間の相関関係

Fig.8 RDVG12 vs Degradation Time correlation 図7及び図8を観ると、各パラメータの変化値に対する近似線は、線形に変化していることが分かる。そのため、劣化は線形的にパラメータを変化させることで表現できると言える。そこで、RDをRD $_{\rm strss}$ 、RDVG12をRDVG12 $_{\rm stress}$ とし、式(13)と式(14)に置き換える。

$$RD_{stress} = A_1 * t_{deg} + RD_{fresh}$$

(13)

$RDVG12_{stress} = B_1 * t_{deg} + RDVG12_{fresh}$  (14)

$\mathbf{t}_{deg}$ は劣化時間である.  $RD_{fresh}$ 及び $RDVG12_{fresh}$ はパラメータの初期値である.  $A_1$ ,  $B_1$ はフィッテングパラメータである. 以上のように,我々はパラメータを式に置き換えることによって,パラメータを変数として扱い劣化を表現できるようにした

## 6. まとめ

本研究では、nチャネルLDMOSのHCI現象について回路シミュレータSPICEを用い、劣化を事前に予想するためのモデルを開発した。nチャネルLDMOSのデバイスモデルはHiSIM-HVを採用した。nチャネルLDMOSはオン抵抗が増加し劣化に繋がることから、nチャネルLDMOSの構造とオン抵抗の関係性を調べHiSIM-HVとの対応を論じ、劣化抽出するめのパラメータを予想した。論文データと測定データからパラメータ抽出を行い、予想したパラメータを増加させることで劣化抽出をした。劣化は、パラメータ変化を式化しパラメータと置き換えることで表現を可能にした。

今回作成したモデルは、ゲート・ソース、ドレイン・ソースのストレスバイアス電圧に対する依存については触れていない。このため、実際の回路シミュレーションで用いるには不十分である。現在、この点について実験研究中である。また、過渡特性のシミュレーションや、小信号ACシミュレーションにおいても検証し、さらに実用的な劣化モデルを開発していきたい。

#### 参考文献

- [1] 築地伸和,青木均,新井薫子,轟俊一郎,香積正基,戸塚拓也,東野将 史:"LDMOSの経時・温度劣化特性解析とモデル化に関する研究"第5回電 気学会東京支部栃木・群馬支所合同研究発表会.pp.7. (2015)

- [2] Hisim-HV 2.2.0 User's manual http://home.http://home.hiroshimau.ac.jp/usdl/HiSIM\_HV/C-Code/HiSIM\_HV\_C.htm

- [3] E. Maricau and G. Gielen, : "Analog IC Reliability in Nanometer CMOS", Springer Science+Business Media New York(2013)

- [4] C. Hu, et al, "Hot-electron induced MOSFET degradation model, monitor, and improvement," IEEE Trans. Electron Devices, 32(2), 375-385, 1985.

- [5] S. Regginani, et al,: "Physics-Based Analytical Model for HCS Degradation in STI-LDMOS Transistors", IEEE Transactions on Electron Devices, vol. 58, No. 9, pp.3072-3080, (2011).

- [6] P. Moens, et al,: "A Comprehensive Model For Hot Carrier Degradation in LDMOS Transistors", IEEE International Reliability physics symposium,pp.492-497, (2007).

- [7] Guido. T. Sasse, et al.; "An LDMOS hot carrier model for circuit reliability simulation", IEEE International Reliability physics symposium,pp.5D.5.1-5D.5.6, (2014).

- [8] Masashi Higashino, et al, "Study on Maximum Electric Field Modeling Used for HCI Induced Degradation Characteristic of LDMOS Transistors" IEEE 11th International Conference on ASIC, Chengdu, China Nov. 3-6, (2015).

- [9] Chao Xia and Xinhong Cheng, et al: "ON-Resistance Degradation Induced by Hot-Carrier Injection in SOI SJ-LDMOS" IEEE Transactions on Electron Devices, Vol. 60, No. 3, pp.1279-1281, (2013)

- [10] N. Soin. S. S. Shahabudin and K. K. Goh, et al,: "Measurement and Characterization of Hot Carrier Safe Operating Area (HCI-SOA) in 24V n-type Lateral DMOS Transistors",10th IEEE International Conference on Semiconductor Electronics, pp.659-663 (2012)