# 逐次比較時間デジタイザ回路の線形性自己校正技術

小澤祐喜、姜日晨、小林春夫、築地伸和(群馬大)、塩田良治(socionext)、畠山一実(群馬大)

群馬大学 理工学部 電子情報理工学科 小林研究室 学部4年 小澤 祐喜 t13304037@gunma-u.ac.jp

### 研究目的

- >逐次比較型時間デジタイザの線形性を自己校正

- ▶タイミングテストに応用可能

- ▶小型•高分解能

- ➤FPGA実装向き 全デジタル構成

これらを満たすアルゴリズムと回路を提案

# アウトライン

- ・ 時間デジタイザ回路の役割

- -時間デジタイザ回路の構成と動作

- -具体的な応用例

- -タイミングテストへの応用

- -有用性

- -技術課題

- 逐次比較型(SAR)TDCの構成と動作

- 校正メカニズム

- -ヒストグラム法による素子遅延値の推定

- -逆関数による校正

- 測定回路を組み込んだSAR TDC

- -回路構成

- -回路動作(ノーマルモード・テストモード)

- シミュレーションによる検証

- まとめと課題

# アウトライン

- 時間デジタイザ回路の役割

- -時間デジタイザ回路の構成と動作

- -具体的な応用例

- -タイミングテストへの応用

- -有用性

- -技術課題

- ・ 逐次比較型(SAR)TDCの構成と動作

- 校正メカニズム

- -ヒストグラム法による素子遅延値の推定

- -逆関数による校正

- 測定回路を組み込んだSAR TDC

- -回路構成

- -回路動作(ノーマルモード・テストモード)

- シミュレーションによる検証

- まとめと課題

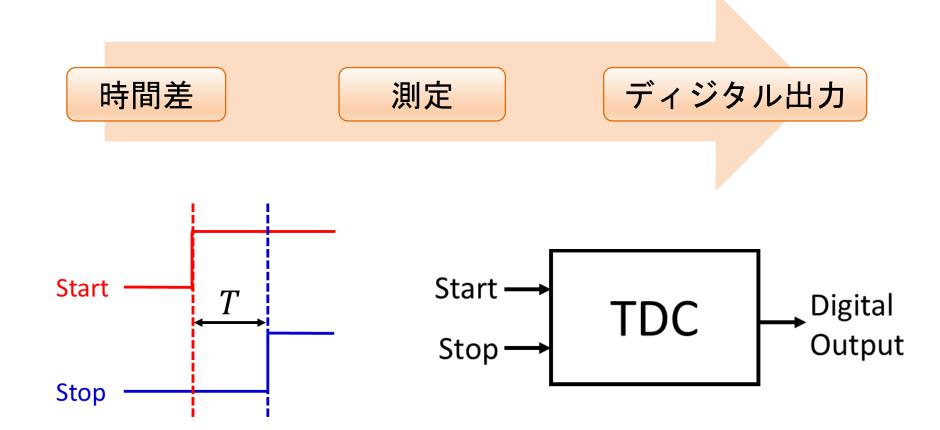

# 時間デジタイザ回路の役割

時間デジタイザ回路(Time-to-Digital Converter、TDC); タイミング信号の時間差を測定しデジタル出力

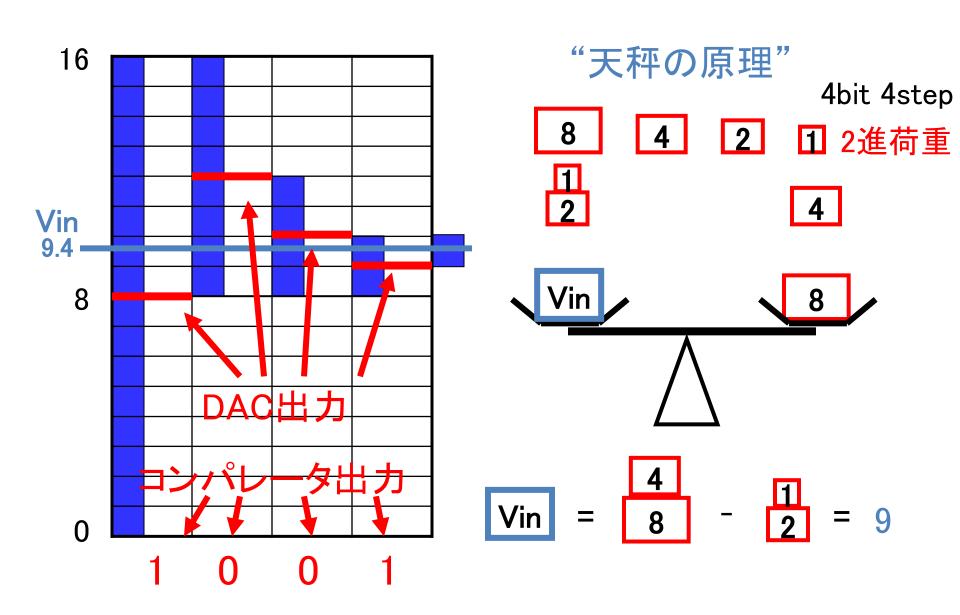

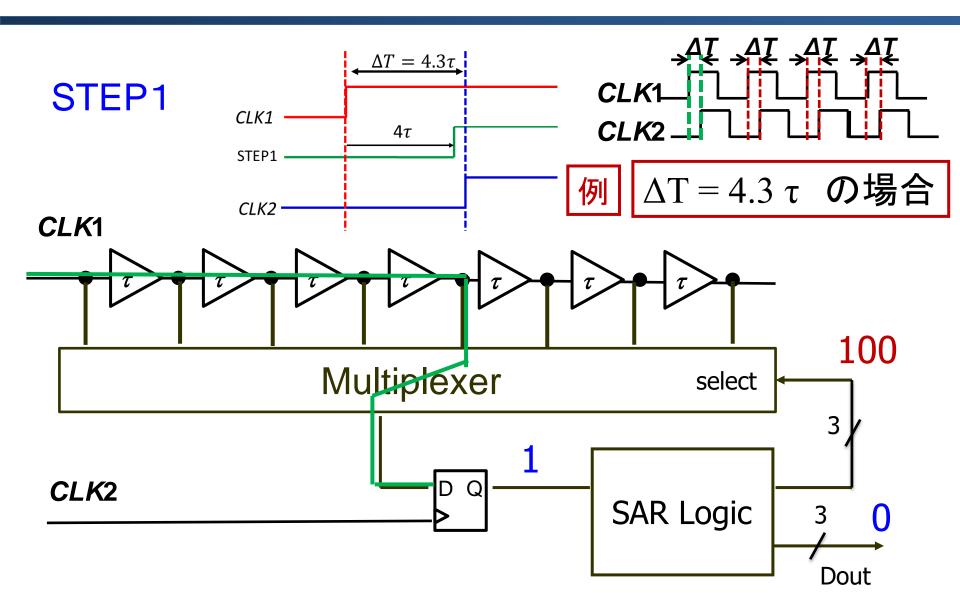

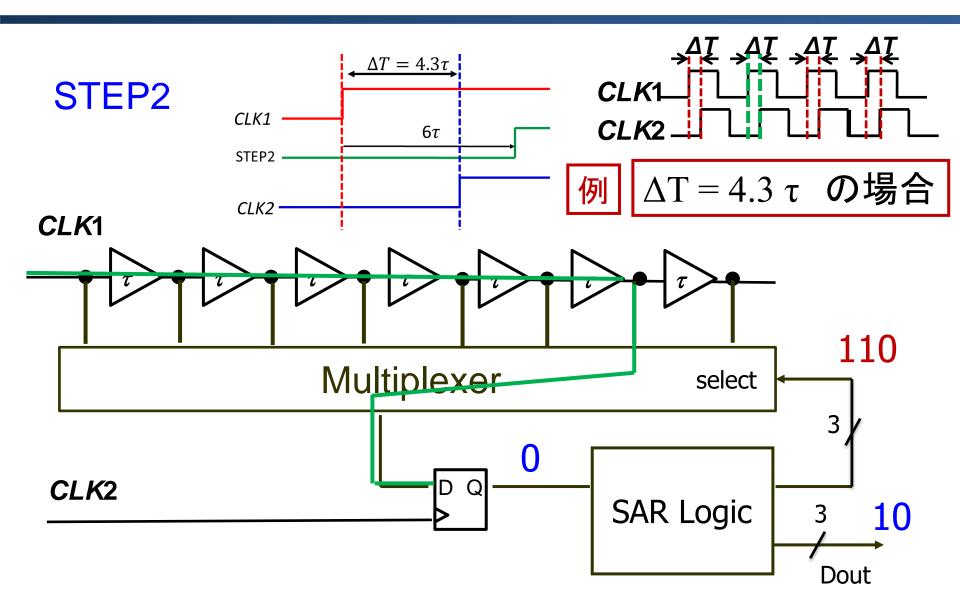

### 逐次比較の原理

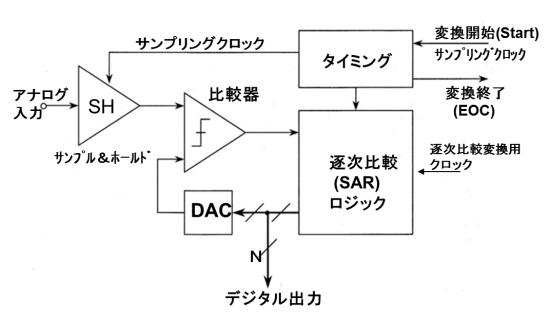

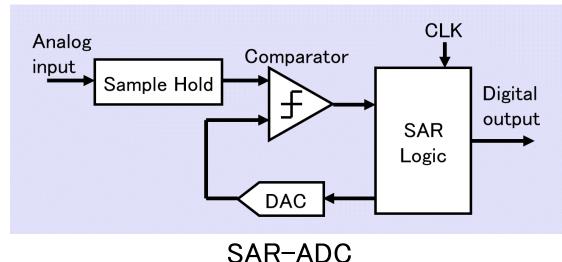

#### 例 逐次比較型ADC

速度と精度のバランスが良く、チップ面積が小さく汎用ADCに最も多く使用される方式

参考 Analog-Digital Conversion : Analog Devices

### 逐次比較:2進探索アルゴリズム

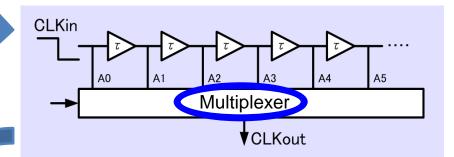

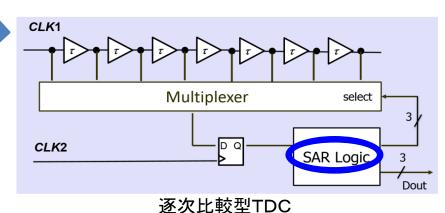

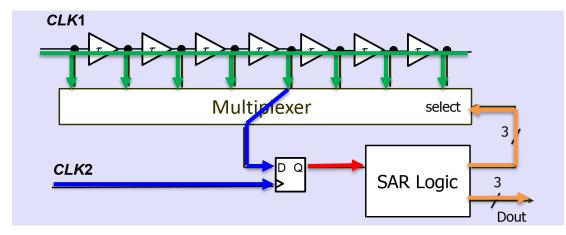

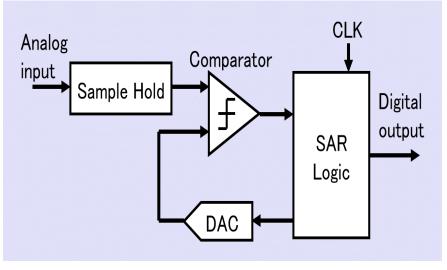

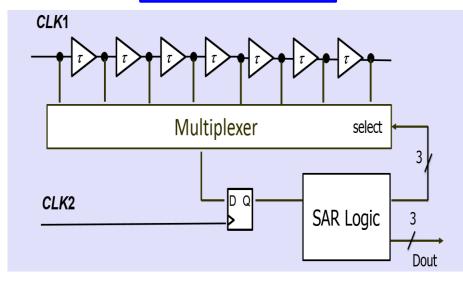

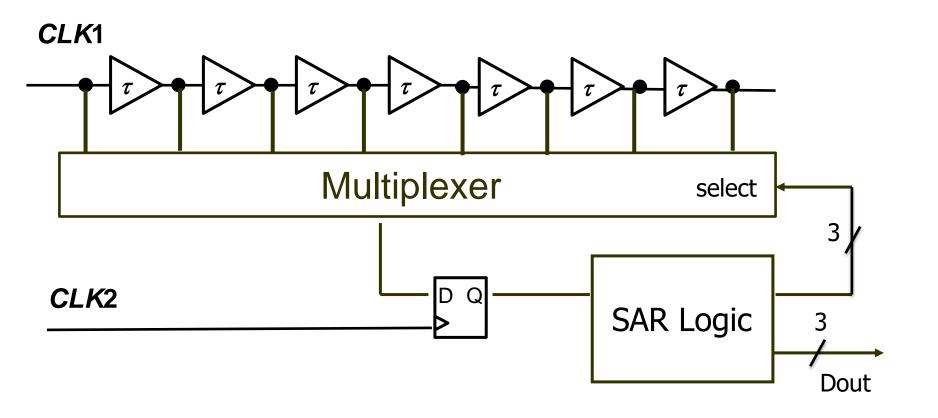

# 逐次比較型TDCの構成

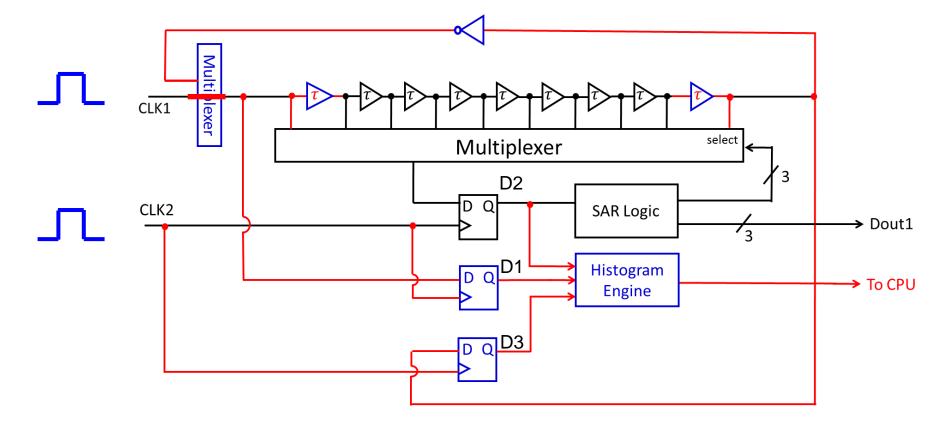

マルチプレクサを使用し Dフリップ-フロップ数を大幅削減

基本フラッシュ型TDC

逐次比較近似の原理を利用し 回路の動作ループを作る

ı

逐次比較型 SAR:Successive Approximation Register

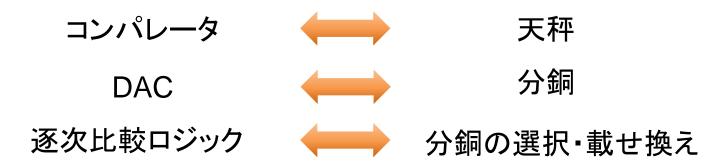

### SAR-ADCとSAR-TDCの比較

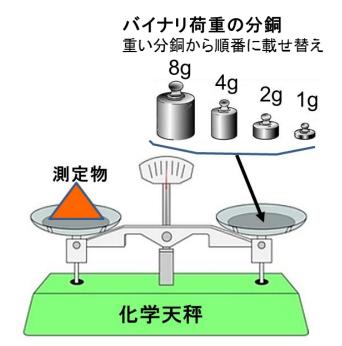

#### 天秤の原理で動作:

- 天秤がコンパレータ

- 分銅がDAC

#### SAK-ADU

#### 天秤の原理で動作:

- 天秤がD-FF

- 分銅が遅延素子

SAR-TDC

# 具体的な応用例

**SIEMENS** CO.,LTD.

放射線計測器 車間等の距離計測 イオン飛行時間分析 時間領域ADC 等

BMW AG CO.,LTD.

JAXA Digital Archives

# タイミングテストへの応用

● 2つの繰り返しクロック信号のタイミング テスト回路としてSAR-TDCを応用

CLK1

CLK2

T

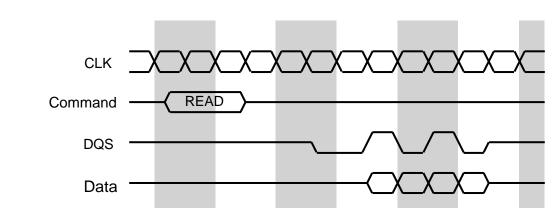

例 DDRメモリのクロック信号

- テスト時間の短縮

- 高い正確性

- 全デジタル設計が可能

小さい回路規模でBOST/BIST実装可能

BOST: Built-Out Self-Test

BIST: Built-In Self-Test

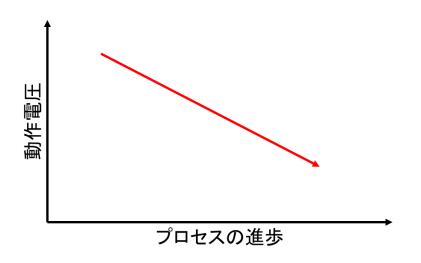

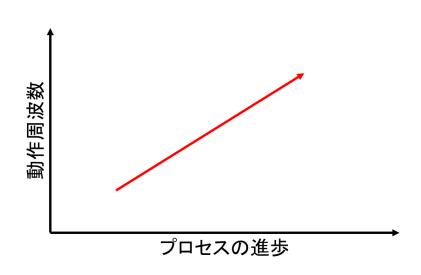

# CMOS微細化に伴う傾向

CMOSプロセス技術の微細化

### TDCの利点

### 利点①

微細化により時間分解能が上がる

### TDCの利点

### 利点②

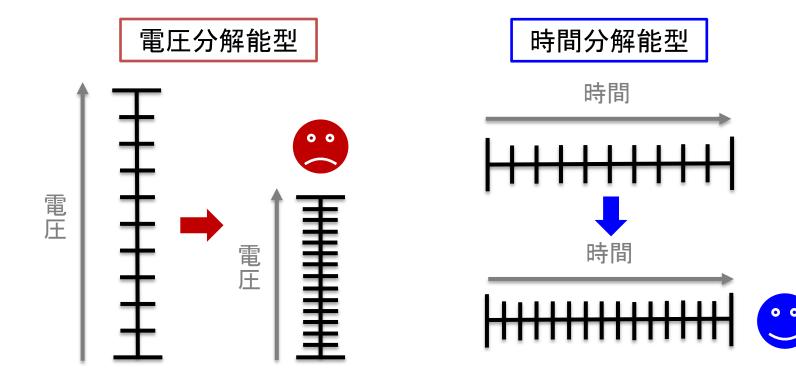

#### 電圧分解能型

SAR-ADC

#### 時間分解能型

**SAR-TDC**

全てデジタル回路で構成できる

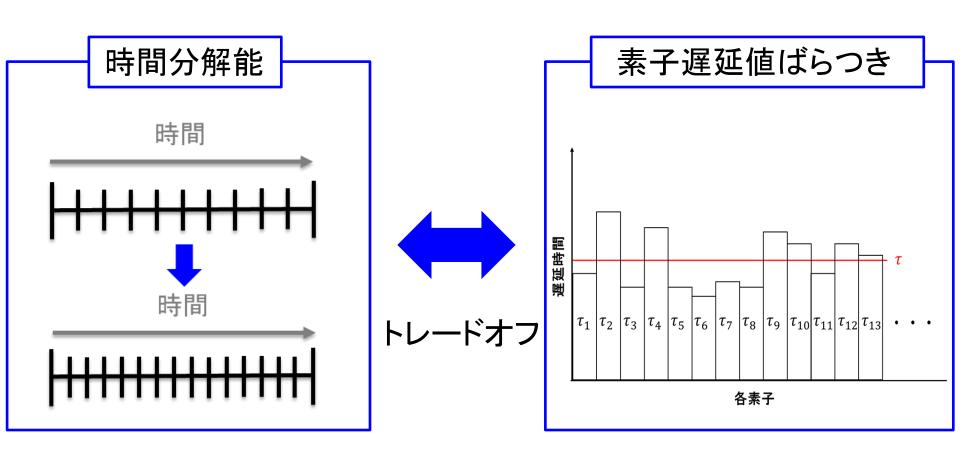

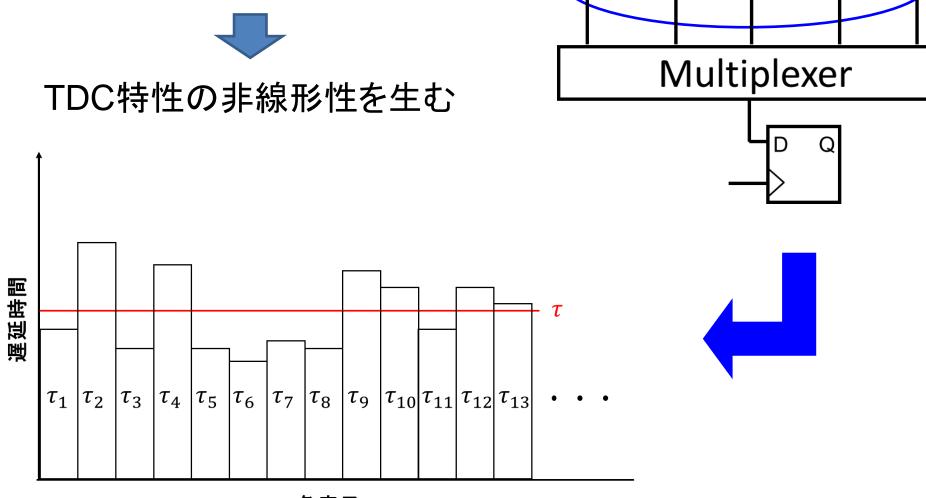

# 技術課題

# 技術課題

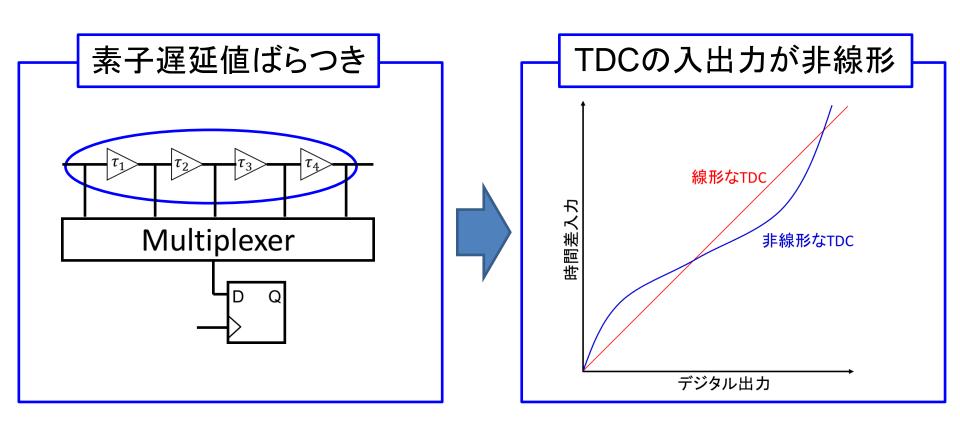

TDCの特性を線形に校正する技術が必要

# アウトライン

- ・ 時間デジタイザ回路の役割

- -時間デジタイザ回路の構成と動作

- -具体的な応用例

- -タイミングテストへの応用

- -有用性

- -技術課題

- 逐次比較型(SAR)TDCの構成と動作

- 校正メカニズム

- -ヒストグラム法による素子遅延値の推定

- -逆関数による校正

- 測定回路を組み込んだSAR TDC

- -回路構成

- -回路動作(ノーマルモード・テストモード)

- シミュレーションによる検証

- まとめと課題

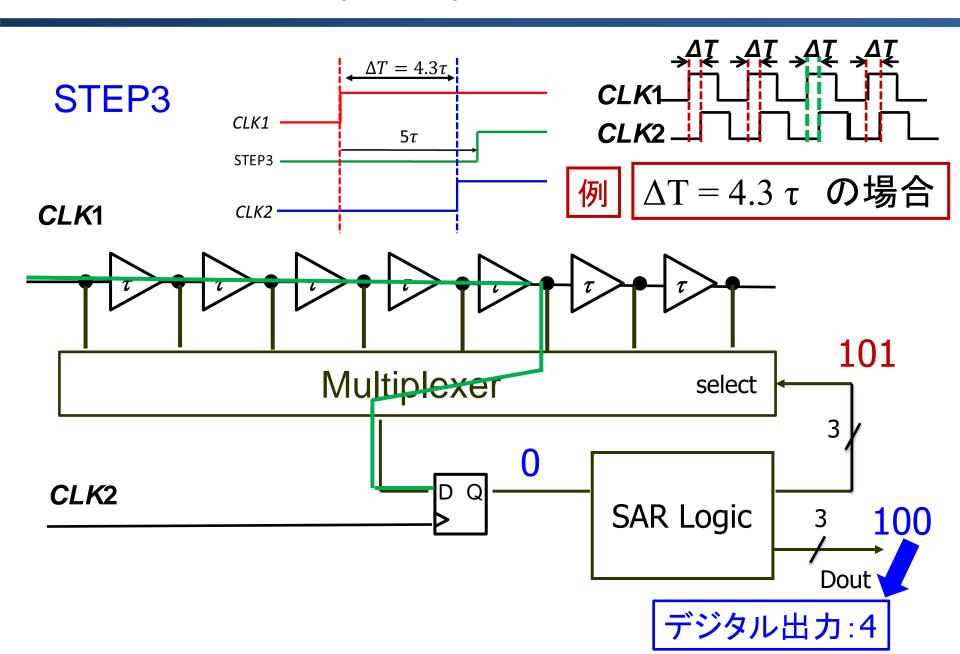

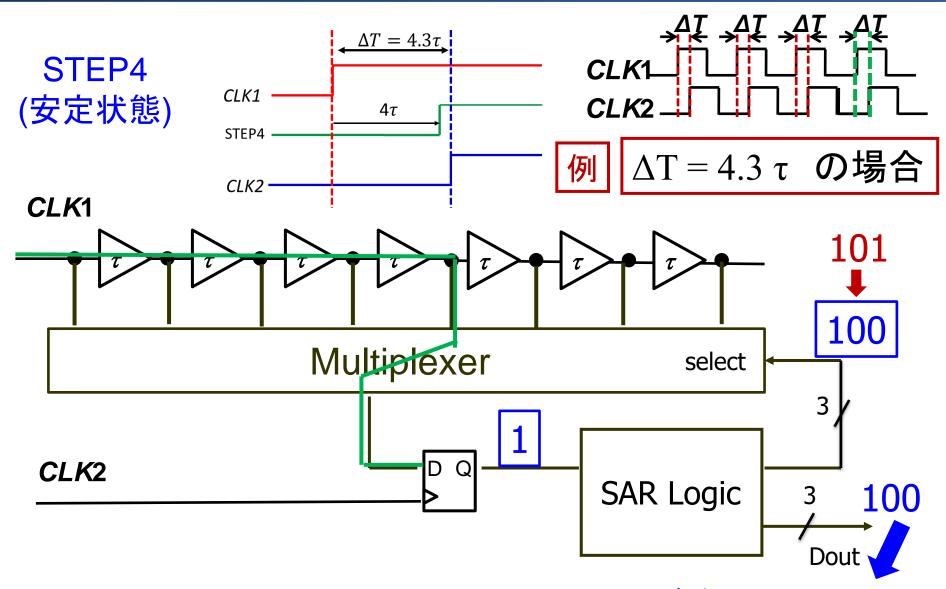

### 回路構成

デジタル出力:4

### アウトライン

- 時間デジタイザ回路の役割

- -時間デジタイザ回路の構成と動作

- -具体的な応用例

- -タイミングテストへの応用

- -有用性

- -技術課題

- ・ 逐次比較型(SAR)TDCの構成と動作

- 校正メカニズム

- -ヒストグラム法による素子遅延値の推定

- -逆関数による校正

- 測定回路を組み込んだSAR TDC

- -回路構成

- -回路動作(ノーマルモード・テストモード)

- シミュレーションによる検証

- まとめと課題

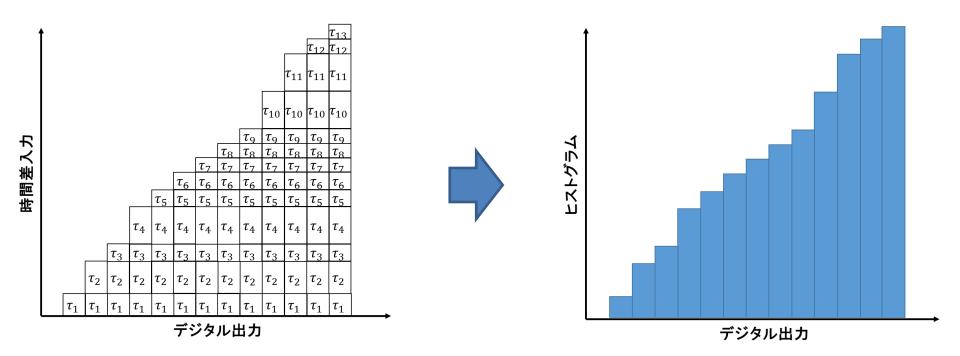

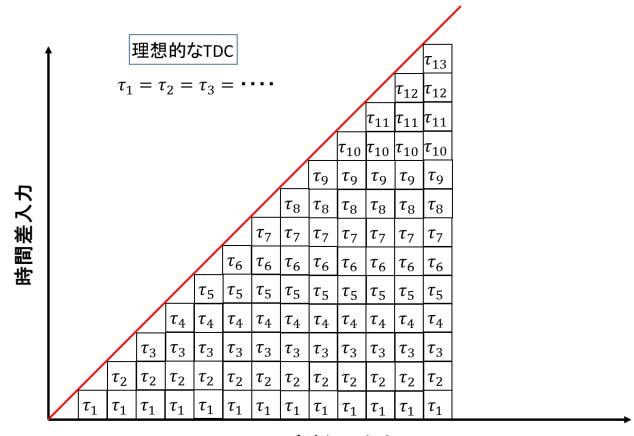

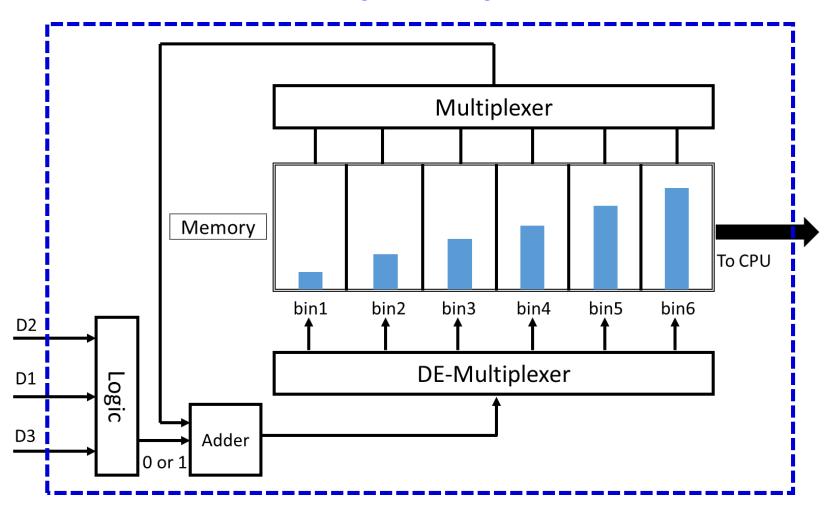

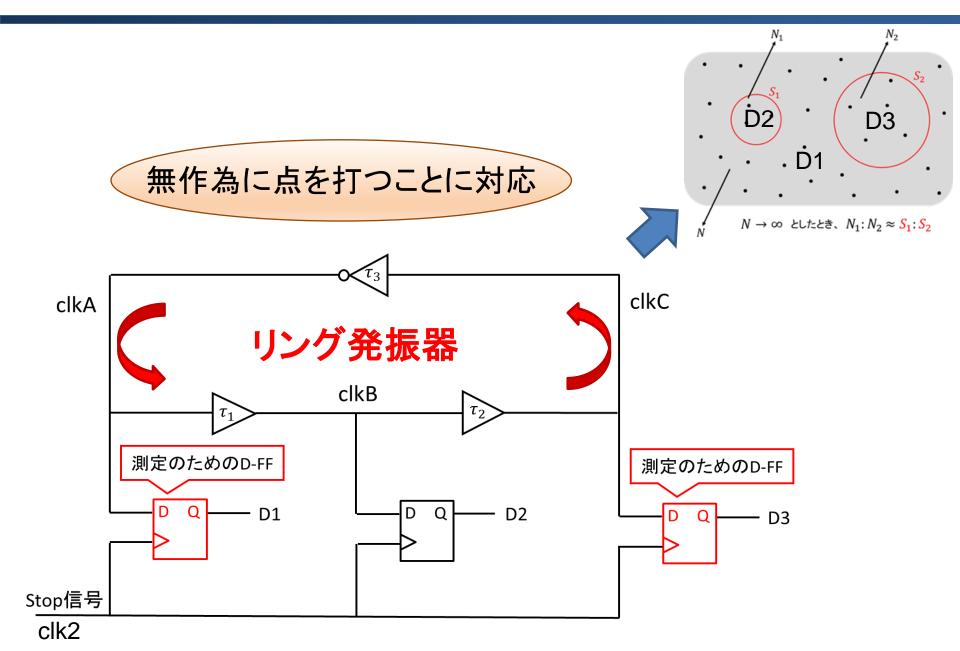

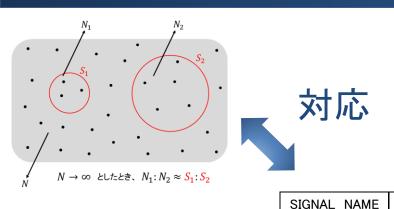

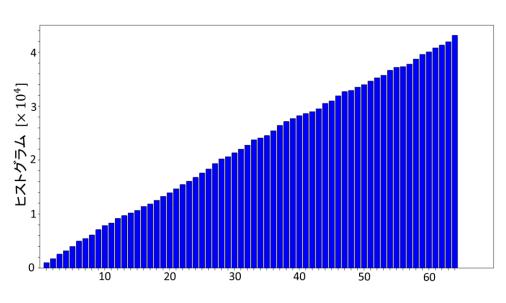

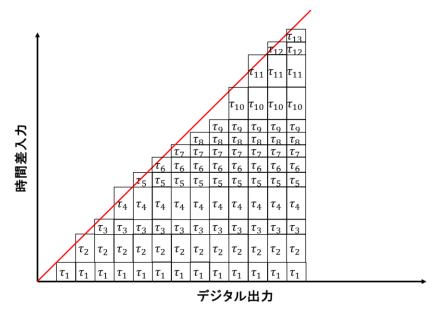

# ヒストグラム法による素子遅延値の推定

### ヒストグラム法

素子遅延値を間接的に知ることが可能

#### ヒストグラム・エンジンによる統計処理

# ヒストグラム法による遅延素子値の推定

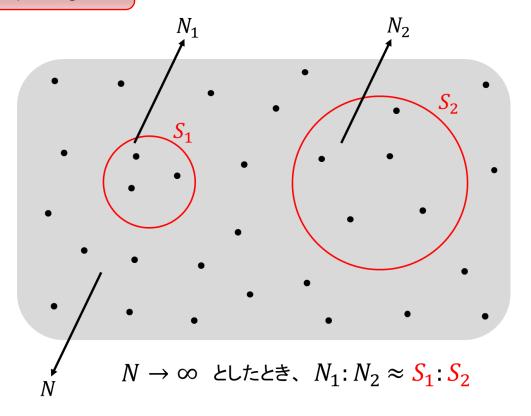

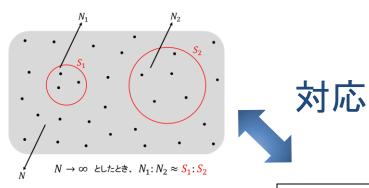

#### ヒストグラム法の原理

全体の面積に対して 無作為に点を打つ

それぞれの円の面積の比は それぞれの点数の比に近似できる

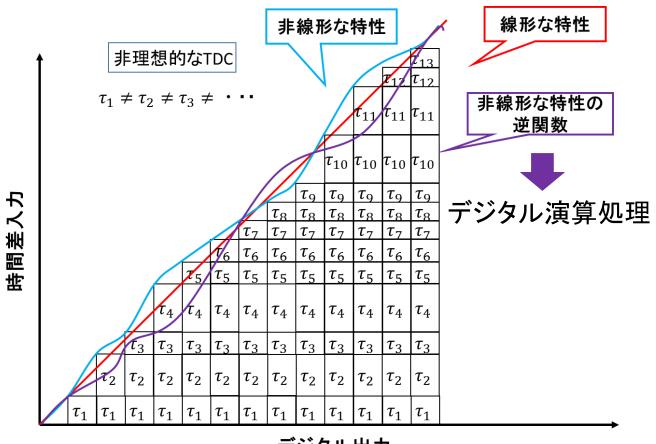

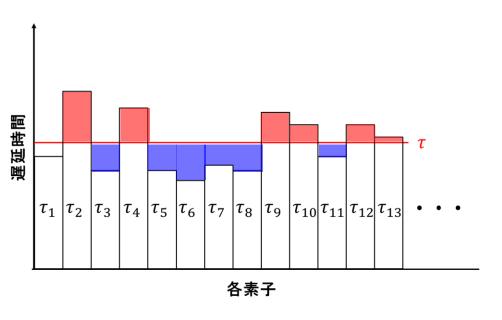

# TDCの線形性劣化

素子遅延値ばらつき

各素子

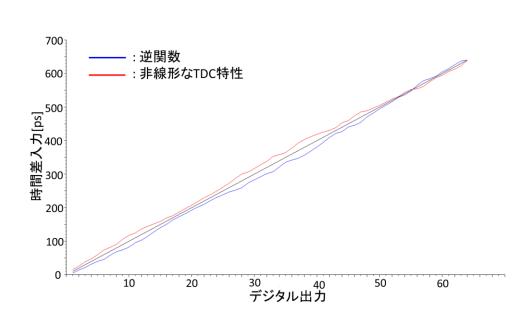

# 逆関数による校正

#### 非線形な特性の逆関数を用いて線形に校正

デジタル出力

# 逆関数による校正

#### 校正後のTDC特性

デジタル出力

# アウトライン

- 時間デジタイザ回路の役割

- -時間デジタイザ回路の構成と動作

- -具体的な応用例

- -タイミングテストへの応用

- -有用性

- -技術課題

- ・ 逐次比較型(SAR)TDCの構成と動作

- 校正メカニズム

- -ヒストグラム法による素子値の推定

- -逆関数による校正

- 測定回路を組み込んだSAR TDC

- -回路構成

- -回路動作(ノーマルモード・テストモード)

- シミュレーションによる検証

- まとめと課題

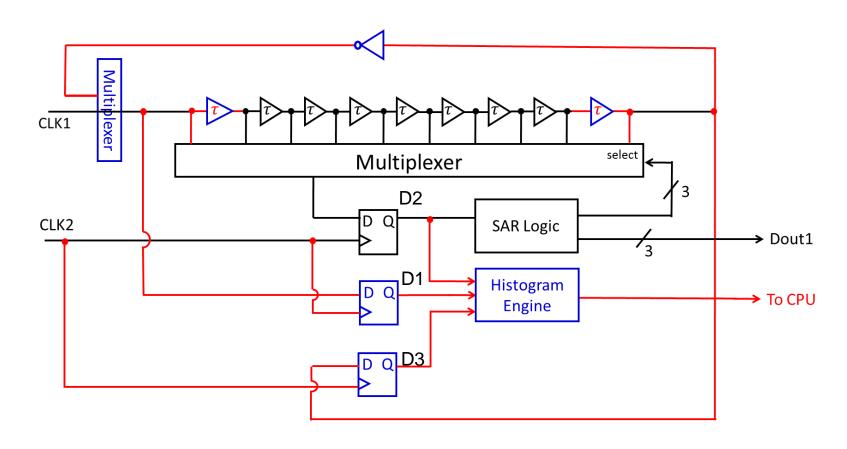

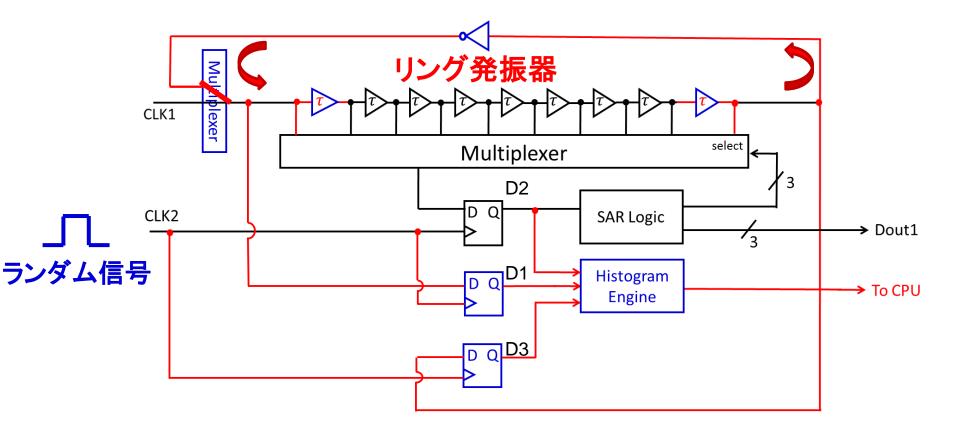

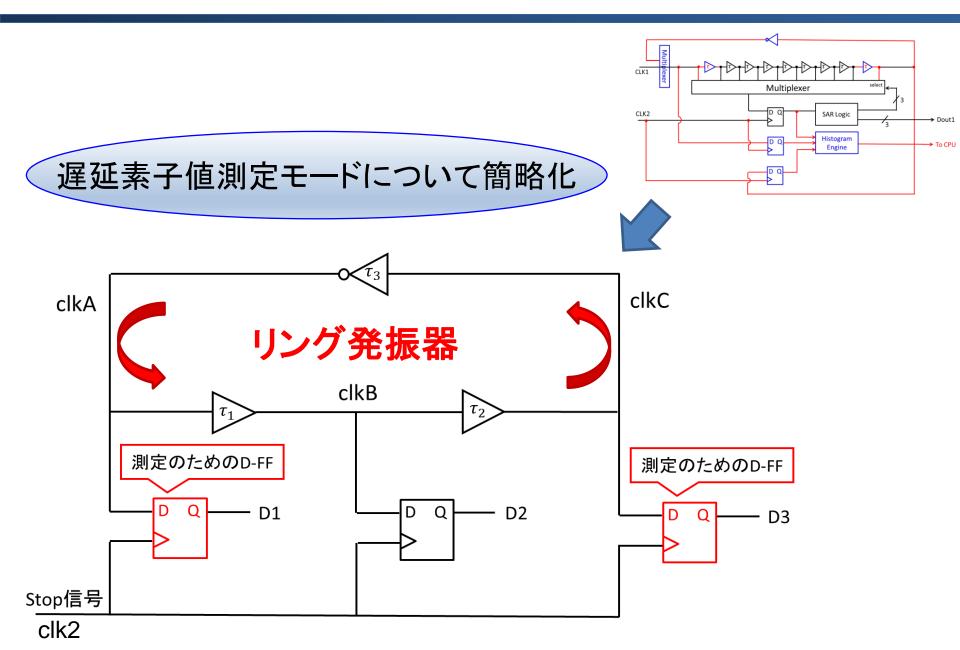

#### <u>回路構成</u>

SAR-TDCに測定回路(素子: 青 導線:赤)を付加

<u>回路動作</u>

### 通常動作モード

SAR-TDCに測定回路(素子: 青 導線:赤)を付加

<u>回路動作</u>

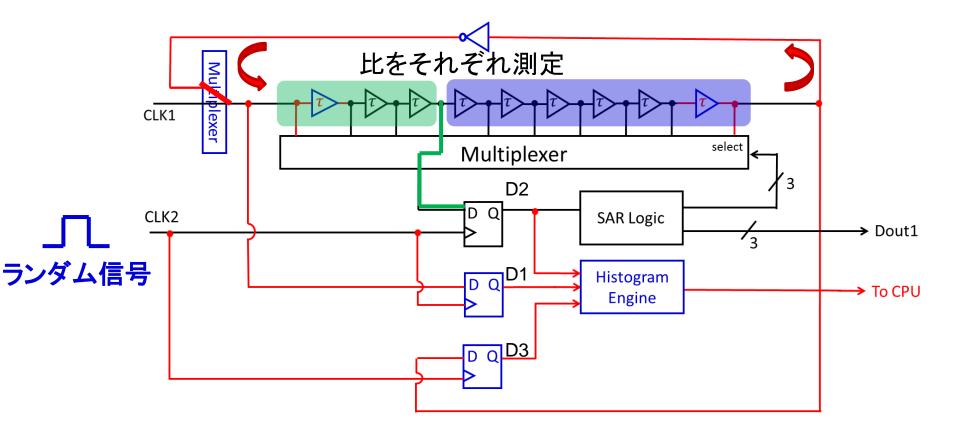

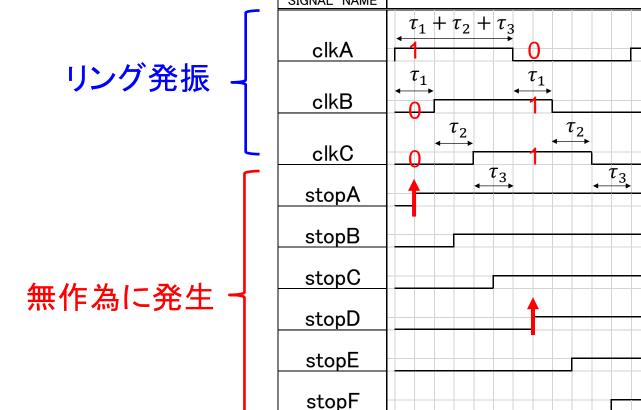

### 遅延素子値測定モード

リング発振器とランダム信号は独立

無作為に点を打つことに対応

<u>回路動作</u>

### 遅延素子値測定モード

素子遅延値の比をそれぞれ測定

フラッシュ型に比べ時間を要する

# Histogram-Engineのブロック図

#### Histogram-Engine

# 簡略化したテストモード回路の構成

# 簡略化したテストモード回路の構成

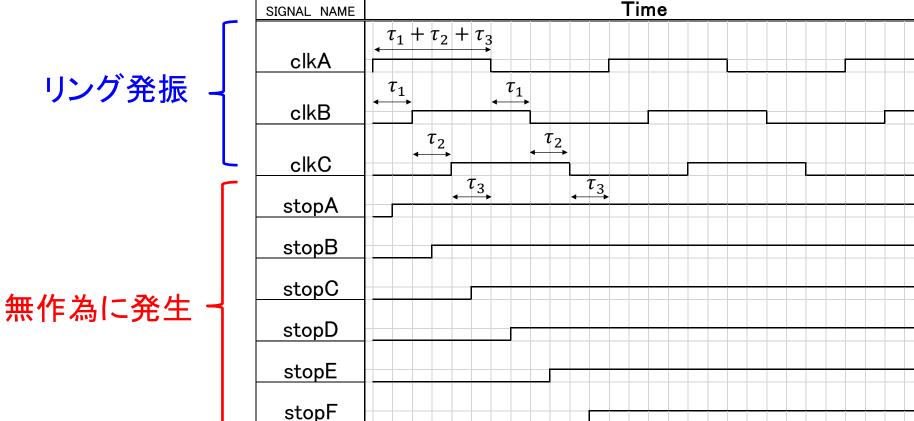

### 簡略化したテストモード回路の動作

### タイミングチャート

### 簡略化したテストモード回路の動作

### タイミングチャート

Time

### アウトライン

- ・ 時間デジタイザ回路の役割

- -時間デジタイザ回路の構成と動作

- -具体的な応用例

- -タイミングテストへの応用

- -有用性

- -技術課題

- ・ 逐次比較型(SAR)TDCの構成と動作

- 校正メカニズム

- -ヒストグラム法による素子値の推定

- -逆関数による校正

- 測定回路を組み込んだSAR TDC

- -回路構成

- -回路動作(ノーマルモード・テストモード)

- シミュレーションによる検証

- まとめと課題

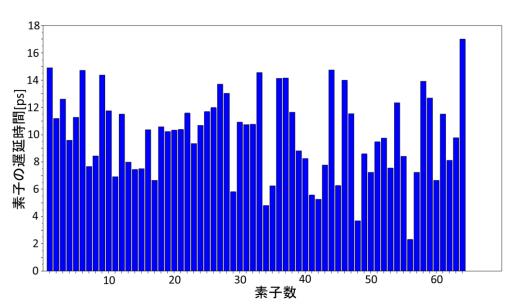

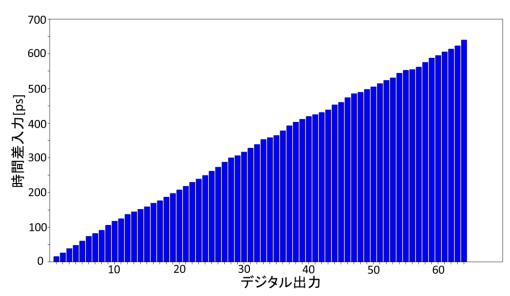

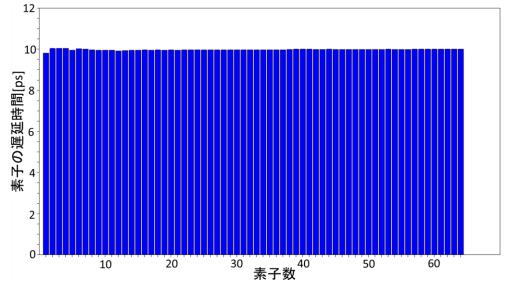

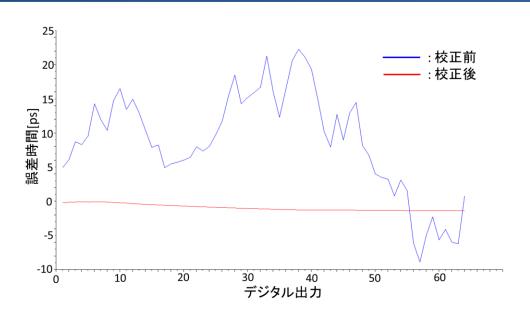

### シミュレーションによる検証

#### Scilab 5.4.1で検証:

逐次比較型TDCのヒストグラム法を用いた校正手法を下記の条件でシミュレーション

#### シミュレーション条件

- ▶素子数6bit(64個)

- > 遅延素子の仕様:

平均遅延時間 10ps (180nmプロセスを想定) 標準偏差 3ps (正規分布に従う)

➤ STOP信号の入力回数:

50000回(無作為に発生)

### 実際の値を生成

乱数を発生させ 素子遅延値のばらつきを生成

TDC特性が生成される

## ヒストグラム法の検証

ヒストグラム法により 統計的に処理

素子遅延値に変換すると 本来のTDCと似た特性が得られる

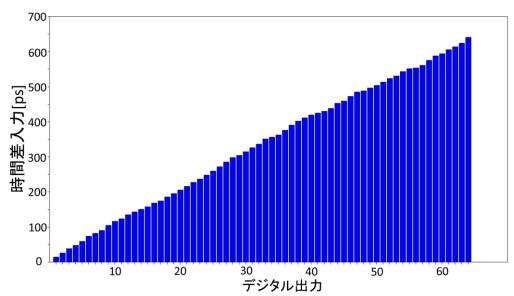

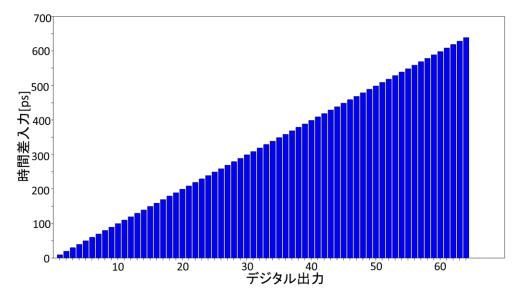

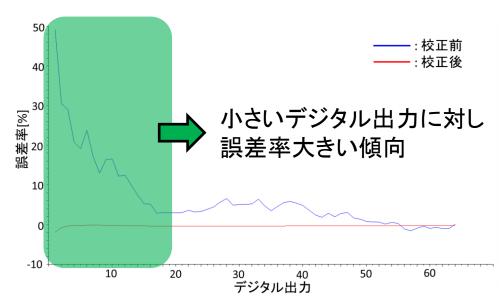

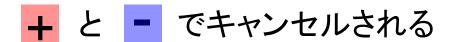

## 逆関数による校正の検証

非線形なTDC特性の 逆関数を用いてキャンセル

校正後のTDC特性

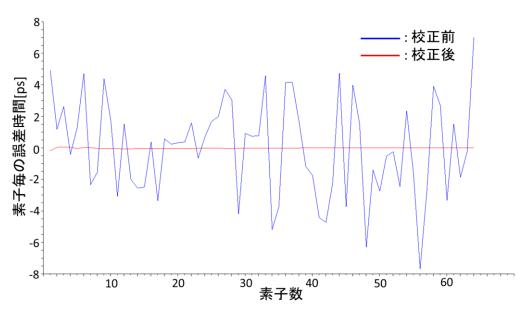

# 誤差について比較

校正後の素子毎の遅延時間

#### 校正前と校正後のTDC特性の誤差

最大誤差率 校正前 49.1% 校正後 1.9%

### 入出力の誤差傾向

特性誤差は小さいデジタル出力で顕著になる

### 誤差について比較

#### 校正前と校正後の特性誤差時間

最大誤差時間 校正前 22.2ps 校正後 1.3ps

# 校正前と校正後の素子毎の遅延時間の誤差

最大誤差時間 校正前 7.6ps 校正後 0.2ps

### アウトライン

- 時間デジタイザ回路の役割

- -時間デジタイザ回路の構成と動作

- -具体的な応用例

- -タイミングテストへの応用

- -有用性

- -技術課題

- ・ 逐次比較型(SAR)TDCの構成と動作

- 校正メカニズム

- -ヒストグラム法による素子値の推定

- -逆関数による校正

- 測定回路を組み込んだSAR TDC

- -回路構成

- -回路動作(ノーマルモード・テストモード)

- シミュレーションによる検証

- まとめと課題

## まとめと課題

- 逐次比較型TDCの非線形な特性を校正できる回路の考案

- ・ヒストグラム法を用いた、逆関数による校正メカニズム

- Scilabによるシミュレーション

今後の課題:

FPGA実装による検証

0 2636833 77 0 71 62 60 2

高速に過ぎゆく時间を測定

04

1 219 11 00

新しい付加価値の創出

69

869

31 1 83 2 7 6 98 56 5 59 4 4 0 62721 06 8 2 63517

1 16 8 41 0 4 65 69 8 08 9 8 2 0229407 28 1 1 93216

9 40 0 48 7 6 1 07 90 35 33 1 1 3 5875035 6 3 1 64838 9

### Q&A

- ・clk1、clk2はとても精度が良いことを前提にしているが、遅延素子が精度悪いのに、テストをするための信号の精度は良いという前提は無理があるのでは? (ルネサスシステムデザイン 松嶋さん)

- →そもそもクロックはそんなにバラつきはしない(小林先生)

- →ヒストグラムを分析することによって分散の値が分かる。そこからクロックの ズレも分かるのではないか。(築地さん)

- →前段に1つのクロック信号をコピーするトリガ回路を付加し、そのトリガ回路の クロック精度を保証することによって解決するのではないか。(小澤)

- ・無作為に入力する信号は、どの程度の試行回数でどの程度の信頼性になるのか(信頼度いくつになるか)?それを説明してくれたらよかった(ソシオネクスト 浜田さん)

- →今後の課題として取り組む(小澤)

### Q&A

- ・1つの遅延素子を使ってリング発振器を何段か使えばそもそもこの研究は不要なのではないか?

- →リング発振器の場合、10GHzが限界であるので有用性がない(聴衆)

- -MUXの校正は?

- →考慮していない(小澤)

- ・車間計測に応用されているというが、具体的にどのような回路でどのように実現されている のか?

- →具体的な回路はブラックボックス化していて調べる方法が無い。むしろ、応用の仕方を新しく教えて頂きたい。(小澤)

- ・遅延素子の誤差で0.2psという表記は量子化誤差があるので不可解に感じた。

- →今後、これを考慮した表記にしたい。(小澤)

- キャンセルするときの回路と演算メカニズムは?

- →以前、先輩が似たような研究をやっていたので、それを応用したい。(小澤)

## 今後

- ・ 点数いくつであれば、何パーセントの信頼性か?

- クロックがずれたときのこと

- →ヒストグラムによる解析、ジッタを計測できる

- •校正手順の逆関数による校正において 横方向の統計をとって最小二乗法をする 連続的な関数(9次)と仮定し、計算を行う。

- ・冗長アルゴリズムを使うと?