# 様々な時間ディジタイザ回路アーキテクチャのタイミングテスト応用への比較検討 小林 春夫

群馬大学大学院 理工学府 電子情報部門 〒376-8515 群馬県桐生市天神町 1-5-1 Phone: 0277-30-1788 Fax: 0277-30-1707 E-mail: koba@gunma-u.ac.jp

#### あらまし

タイミング信号測定・計測用 BIST/BOST 応用のための時間ディジタル回路について,筆者の研究室で研究を行ってきたアルリズム,原理,回路,特徴を比較検討する.

キーワード 時間ディジタル変換回路,時間領域アナログ回路,タイミング測定,BIST,BOST

# Time-to-Digital Converter Architectures for Timing Measurement

# Haruo KOBAYASHI

Division of Electronics and Informatics, Graduate School of Science and Technology, Gunma University

1-5-1 Tenjin-cho Kiryu-shi Gunma 376-8515 Japan

**Abstract:** This paper presents the research results of time-to-digital converters (TDCs) performed at the author's laboratory Their algorithms, principles, circuits and features as timing measurement built-in self-test (BIST) and/or built-out self-test (BOST) are shown.

**Keywords** Time-to-Digital Converter, Time Domain Analog Circuit, Timing Measurement, BIST, BOST

# 1. 時間領域アナログ回路

集積回路微細化に伴い、分解能を電圧振幅ではなく時間軸で得る回路技術が関心を集めている. [1] これは時間領域アナログ回路と呼ばれ、そのキーコンポーネントの一つが時間ディジタイザ回路(Time-to-Digital Converter: TDC)である. この TDC 回路は LSI テストの分野ではタイミング信号測定・テスト用の BIST/BOST として使うことができる. ここでは筆者の研究室で行っている TDC 回路について概要と得失比較を示す.

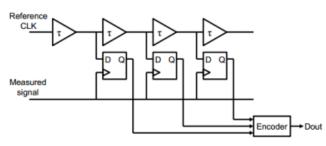

**2. フラッシュ型時間ディジタイザ回路** フラッシュ型時間ディジタイザ回路(Time-to-Digital Converter: TDC)は日本人の発明である [2] (図 1). 全 回路をディジタルで実現できる.

図 1 フラッシュ型時間ディジタイザ回路

# 3. 時間ディジタイザ回路の線形性自己校

#### 正

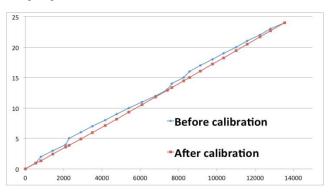

図1の遅延 $\tau$ の相対ばらつきによる TDC 非線形性を完全ディジタル回路により自己校正することができる. [3-5] 図 2 にその FPGA 実現・測定結果を示す.

図2 フラッシュ型時間ディジタイザ回路の線形性自己校正前,校正後の特性比較

この手法を適用することで、ばらつきを積極利用して時間分解能を向上させる確率的時間ディジタイザ回路を実用的なものにすることができる. [6,7]

# 4. 剰余系時間ディジタイザ回路

図1のフラッシュ型時間ディジタイザ回路は分解能を大きくすると、回路規模が非常に大きくなる.これ

を剰余系(表 1)とリング発振回路(図 3)を用いると同等性能の TDC を実現することができる. FPGA 実現・実 測での動作検証をした. [8]

表 1 整数 k と対応する

| 2 | 3. | 5 | に対す | トる | 剰余 | (m1. | m2. | m3 | ) . |

|---|----|---|-----|----|----|------|-----|----|-----|

|   |    |   |     |    |    |      |     |    |     |

| m1 | m2 | m3 | k  |

|----|----|----|----|

| 0  | 0  | 0  | 0  |

| 1  | 1  | 1  | 1  |

| 0  | 2  | 2  | 2  |

| 1  | 0  | 3  | 3  |

| 0  | 1  | 4  | 4  |

| 1  | 2  | 0  | 5  |

| 0  | 0  | 1  | 6  |

| 1  | 1  | 2  | 7  |

| 0  | 2  | 3  | 8  |

| 1  | 0  | 4  | 9  |

| 0  | 1  | 0  | 10 |

| 1  | 2  | 1  | 11 |

| 0  | 0  | 2  | 12 |

| 1  | 1  | 3  | 13 |

| 0  | 2  | 4  | 14 |

| m1 | m2 | m3 | k  |

|----|----|----|----|

| 1  | 0  | 0  | 15 |

| 0  | 1  | 1  | 16 |

| 1  | 2  | 2  | 17 |

| 0  | 0  | 3  | 18 |

| 1  | 1  | 4  | 19 |

| 0  | 2  | 0  | 20 |

| 1  | 0  | 1  | 21 |

| 0  | 1  | 2  | 22 |

| 1  | 2  | 3  | 23 |

| 0  | 0  | 4  | 24 |

| 1  | 1  | 0  | 25 |

| 0  | 2  | 1  | 26 |

| 1  | 0  | 2  | 27 |

| 0  | 1  | 3  | 28 |

| 1  | 2  | 4  | 29 |

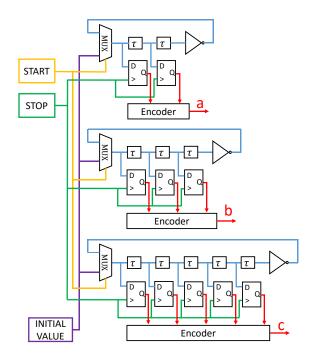

図3 剰余系時間ディジタイザ回路の構成

# 5. Gray code 時間ディジタイザ回路

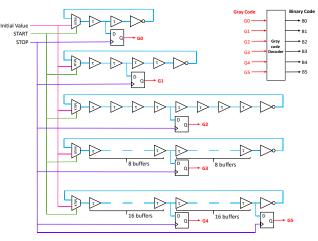

剰余系時間ディジタイザ回路では遅延 $\tau$ 間にミスマッチがあるとグリッチが生じる.この問題を軽減するため Gray code (表 2) 時間ディジタイザを提案・FPGA 実現・測定した. [9] (図 4, 5, 6)

表 2. 4-bit Binary & Gray codes

| Decimal | Binary | Gray |

|---------|--------|------|

| numbers | Code   | Code |

| 0       | 0000   | 0000 |

| 1       | 0001   | 0001 |

| 2       | 0010   | 0011 |

| 3       | 0011   | 0010 |

| 4       | 0100   | 0110 |

| 5       | 0101   | 0111 |

| 6       | 0110   | 0101 |

| 7       | 0111   | 0100 |

| 8       | 1000   | 1100 |

| 9       | 1001   | 1101 |

| 10      | 1010   | 1111 |

| 11      | 1011   | 1110 |

| 12      | 1100   | 1010 |

| 13      | 1101   | 1011 |

| 14      | 1110   | 1001 |

| 15      | 1111   | 1000 |

図 4 6-bit Gray code 時間ディジタイザ回路の構成

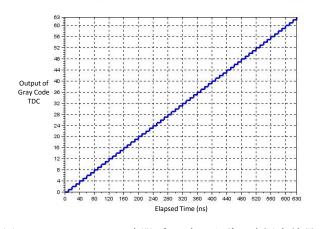

図5 6-bit Gray code 時間ディジタイザ回路測定結果

図 6 6-bit Gray code 時間ディジタイザ回路 FPGA 実現

# 6. 逐次比較近似時間ディジタイザ回路

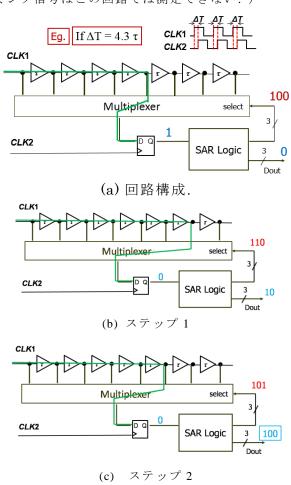

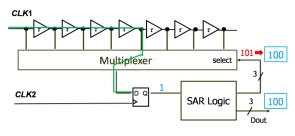

逐次比較近似 AD 変換器にヒントを得て逐次比較近 似時間ディジタイザ回路を考案した. [10, 11] (図 7) し かし、時間は保持できないので、繰り返しタイミング 信号の測定にのみ適用できる. (シングルベントのタ イミング信号はこの回路では測定できない.)

(d) ステップ 3

図 7 逐次比較近似時間ディジタイザ回路.

# 7. デルタシグマ型時間ディジタイザ回路

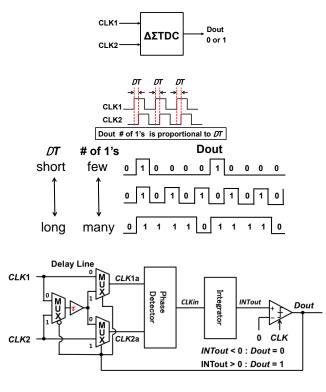

一方, AD/DA 変換器に良く用いられている  $\Delta \Sigma$  変調 技術も日本人の発明である [12].

筆者の研究室では両者を組み合わせたデルタシグ マ TDC 回路[14-21]について研究を行い, 新たなアル ゴリズムを導出してアナログ FPGA 等で動作・有効性 を検証している.(図 8,9) 簡単な回路で測定時間を相 対的に長くとれば非常に細かい時間分解能が得られ, 線形性も良い. [13] 位相ノイズ測定[22-26], 完全デ ィジタル PLL 回路 [27, 28] 等今後ますます応用が広 がることが期待できる.

筆者は、様々なところでデルタシグマ変調器を用い ると上手くいく, 工夫した回路構成を考えてもデルタ シグマ変調器に帰着することが多いということを経験 している.

図8 デルタシグマ型時間ディジタイザ回路

図 9 デルタシグマ型時間ディジタイザ回路の アナログ FPAG (PSoC) 実現

# 8. 時間領域アナログ回路の特徴

ここでは時間ディジタイザ回路等の時間領域アナログ 回路(Time Domain Analog Circuit: TD 回路)と従来の 電圧領域アナログ回路(Voltage Domain Analog Circuit: VD 回路)の特徴を比較する.

- 電圧は保持できるが時間は保持できない.

- 時間差情報は時間差増幅回路で増幅できる

- 時間は無限に続くので TD 回路のダイナミックレンジは無限大である.

- VD 回路のダイナミックレンジは信号レベルが通常 Vss と Vdd 間であるので有限である.

- 基準周波数 fref からその分周 fref/2, fref/4, fref/8,…を正確に得ることができる.

- 基準電圧 Vref からその正確な分圧 Vref/2, Vref/4, Vref/8, …を得ることは難しい.

- ジッタは TD 回路で、ノイズは VD 回路で難しい問題である。

- TD 回路ではリング発振回路はしばしば有効に利用できる. 例えばここでも示したように TDC のヒストグラム 法線 形性自己校正, 剰余系 TDC, Gray code TDC に活用される.

- 大部分の TDC は完全ディジタル構成可能であり、 古カスタムではなく FPGA で実現でき BOST に活 用できる.

- デルタシグマ TDC はアナログ回路が必要であるが、規模が小さいのでアナログ FPGA で実現できる

- 大部分の AD 変換器は比較的規模の大きなアナログ回路(およびディジタル回路)が必要で, FPGA 実現は難しく, 多くの場合フルカスタム CMOS IC として実現しなければならない.

- フラッシュ型, バーニアフラッシュ型, 剰余系, Gray code TDC は1つのタイミングイベントの 測定が可能である.

- 逐次比較近似 TDC, デルタシグマ型 TDC は繰り 返しタイミング信号を測定する.

- ADC アーキテクチャがヒントになり新たな TDC アーキテクチャが発想される.

#### 9. まとめ

この論文では筆者の研究室で研究開発をしている様々な時間ディジタイザ回路を紹介・特徴の比較を行った. 微細 CMOS に適しており, 実・高性能化が容易であるので, 広い応用展開が期待できる.

TDC はディジタル的に設計できフルカスタム CMOS ではなく FPGA 設計でき、破壊的イノベーションになることが期待できる. [29-31]

# 参考文献

#### ナノ CMOS 時代のアナログ技術のレビュー

[1] H. Kobayashi, H. Aoki, K. Katoh C. Li, "Analog/Mixed-Signal Circuit Design in Nano CMOS Era", IEICE Electronics Express, vol.11 no.3, pp.1-15 (2014)

# 最初のフラッシュ型 TDC 回路の発表

[2] Y. Arai, T. Baba, "A CMOS Time to Digital Converter VLSI for High-Energy Physics", IEEE Symposium on VLSI Circuits (1988).

# フラッシュ型 TDC とヒストラム法自己校正

- [3] K. Katoh, Y. Kobayashi, T. Chujo, J. Wang, E. Li, C. Li, H. Kobayashi, "A Small Chip Area Stochastic Calibration for TDC Using Ring Oscillator", Journal of Electronic Testing: Theory and Applications, Springer (Dec. 2014).

- [4] T. Chujo, D. Hirabayashi, K. Kentaroh, C. Li, Y. Kobayashi, J. Wang, K. Sato, H. Kobayashi, "Experimental Verification of Timing Measurement Circuit With Self-Calibration", IEEE International Mixed-Signals, Sensors and Systems Test Workshop (IMS3TW'14), Porto Alegre, Brazil (Sept. 2014).

- [5] K. Katoh, Y. Doi, S. Ito, H. Kobayashi, E. Li, N. Takai, O. Kobayashi, "An Analysis of Stochastic Self-Calibration of TDC Using Two Ring Oscillators", IEEE 22nd Asian Test Symposium, Yilan, Taiwan, (Nov. 2013).

#### 確率的 TDC 回路

- [6] S. Ito, S. Nishimura, H. Kobayashi, S. Uemori, Y. Tan, N. Takai, Takahiro J. Yamaguchi, K. Niitsu, "Stochastic TDC Architecture with Self-Calibration," IEEE Asia Pacific Conference on Circuits and Systems, Kuala Lumpur, Malaysia (Dec. 2010).

- [7] C. Li, J. Wang, H. Kobayashi, R. Shoita, "Timing Measurement BOST Architecture with Full Digital Circuit and Self-Calibration Using Characteristics Variation Positively for Fine Time Resolution", IEEE International Mixed-Signals Testing Workshop, Catalunya, Spain (July 2016).

#### 剰余系 TDC 回路

[8] C. Li, H. Kobayashi, "A Residue Number System Based Time-to-Digital Converter Architecture and its FPGA Implementation", Advanced Micro-Device Engineering VI, Key Engineering Materials (2016)

#### Gray Code TDC 回路

[9] C. Li, H. Kobayashi, "A Glitch-Free Time-to-Digital Converter Architecture Based on Gray Code", 電気学会論文誌 (和文誌 C), vol. 136, no. 1 (2016 年 1 月).

#### 逐次比較近似 TDC 回路

[10] 姜日晨,小林春夫,「バーニアの原理を用いた逐次比較型タイムディジタイザ回路の設計と高性能化」第5回電気学会東京支部栃木・群馬支所合同研究発表会,宇都宮(2015年3月)

[11] R. Jiang, C. Li, M. Yang, H. Kobayashi, Y. Ozawa, N. Tsukiji, M. Hirano, R. Shiota, K. Hatayama, "Successive Approximation Time-to-Digital Converter with Vernier-level Resolution", IEEE International Mixed-Signals Testing Workshop, Catalunya, Spain (July 2016)\_

## 安田靖彦先生のデルタシグマ変調技術の発明回顧録

[12] 安田靖彦「技術の生みの親・育ての親」郵政研究 所月報 巻頭言(2001年7月).

# 最初のデルタシグマ TDC 回路の発表

[13] B. Young, K. Sunwoo A. Elshazly, P. K. Hanumolu, "A 2.4ps Resolution 2.1mW Second-order Noise-shaped Time-to-Digital Converter with 3.2ns Range in 1MHz Bandwidth," IEEE Custom Integrated Circuits, San Jose (Sept. 2010)

# デルタシグマ TDC 回路

- [14] S. Uemori, M. Ishii, H.Kobayashi, et. al, "Multi-bit Sigma-Delta TDC Architecture with Improved Linearity," Journal of Electronic Testing: Theory and Applications, Springer, vol. 29, no. 6, pp.879-892 (Dec. 2013).

- [15] S. Uemori, M. Ishii, H. Kobayashi, et. al, "Multi-bit Sigma-Delta TDC Architecture for Digital Signal Timing Measurement", IEEE International Mixed-Signals, Sensors, and Systems Test Workshop, Taipei, Taiwan (May 2012).

- [16] S. Uemori, M. Ishii, H. Kobayashi, et. al, "Multi-bit Sigma-Delta TDC Architecture with Self-Calibration", IEEE Asia Pacific Conference on Circuits and Systems, Kaohsiung, Taiwan (Dec. 2012).

- [17] Y. Arakawa, Y. Osawa, H. Kobayashi, O. Kobayashi, "Linearity Improvement Technique of Multi-bit Sigma-Delta TDC for Timing Measurement", IEEE 3rd International Workshop on Test and Validation of High-Speed Analog Circuits, Anaheim, CA (Sept. 2013)

- [18] 平林 大樹, 荒川 雄太, 河内智, 石井 正道, 上森 聡史, 佐藤 幸志, 小林 春夫, 新津 葵一, 高井伸和「ディジタル信号タイミング試験用 BOST の検討」電気学会 電子回路研究会, 熊本 (2012年10月)

- [19] T. Chujo, D. Hirabayashi, M. Tsuji, K. Sato, H. Kobayashi, "Multi-bit Delta-Sigma TDC BOST for Timing Test", IEEE International Test Conference, Poster Session, Seattle, WA (Oct. 2014).

- [20] 中條剛志, 平林大樹, 荒船拓也, 佐藤幸志, 小林春夫, "マルチビットデルタシグマ型タイムディジタイザ回路の FPGA 実現・測定検証", 電気学会電子回路研究会, 秋田 (2014年 10月)

- [21] T. Chujo, D. Hirabayashi, T. Arafune, S. Shibuya, S. Sasaki, H. Kobayashi, M. Tsuji, R. Shiota, M. Watanabe, N. Dobashi, S. Umeda, H. Nakamura, K. Sato, "Timing Measurement BOST With Multi-bit Delta-Sigma TDC", 20th IEEE International Mixed-Signal Testing Workshop, Paris, France (June 2015).

# デルタシグマ TDC 回路の位相ノイズ測定への応用

- [22] D. Hirabayashi, Y. Osawa, N. Harigai, H. Kobayashi et. al, "Phase Noise Measurement with Sigma-Delta TDC", IEEE International Test Conference, Poster Session, Anaheim, CA (Sept. 2013).

- [23] 大澤優介, 平林大樹, 針谷 尚裕, 小林春夫, 新津葵一, 小林修「デルタシグマ TDC を用いた 位相ノイズ測定」電気学会 電子回路研究会 島根 (2014 年 7月)

- [24] Y. Osawa, D. Hirabayashi, N. Harigai, H. Kobayashi, K. Niitsu, O. Kobayashi, "Phase Noise Measurement Techniques Using Delta-Sigma TDC", IEEE International Mixed-Signals, Sensors and Systems Test Workshop (IMS3TW'14), Porto Alegre, Brazil (Sept. 2014).

- [25] Y. Osawa, D. Hirabayashi, N. Harigai, H. Kobayashi, O. Kobayashi, "Phase Noise Measurement and Testing with Delta-Sigma TDC," The 4th IEICE International Conference on Integrated Circuits Design and Verification, Ho Chi Minh City, Vietnam (Nov. 2013).

- [26] 小林春夫「デルタシグマ型タイムディジタイザ回路のアルゴリズム・回路設計とアナログ FPGA 実現」アナログ・ミックスドシグナルにおけるシステム設計セミナー 半導体開発におけるシステム設計の成功の秘訣とは?, MathWorks 社セミナー,横浜 (2014 年 6 月)

# 完全ディジタル PLL 回路と TDC 回路

- [27] 湯本哲也,村上健,西村繁幸,田邊朋之,壇徹,高橋伸夫,内藤智洋,北村真一,坂田浩司,小林春夫,高井伸和,新津葵一「TV チューナ用完全ディジタル PLL 回路 システムの観点から」電気学会電子回路研究会,ECT-11-089,長崎(2011年10月)

- [28] R. B. Staszewski, P. T. Balsara (著) 山田庸一郎 (訳) 小林春夫 (監訳) [完全ディジタル PLL 回路の設計ーディープ・サブミクロン CMOS プロセスで実現する All-Digital Frequency Synthesizer」 CQ 出版 (2010年9月出版) (Robert Bogdan Staszewski, Poras T. Balsara, All-Digital Frequency Synthesizer in Deep-Submicron CMOS Wiley-Interscience (2006) の日本語訳)

#### 破壊的イノベーション

- [29] クレイトン・クリステンセン(著), 玉俊平太(監修), 伊豆原弓(翻訳)「イノベーションのジレンマー技術革新が巨大企業を滅ぼすとき」, Harvard Business School Press (2001年)

- [30] クレイトン・クリステンセン、ジェームズ・アルファース、カレン・ディロン(著)、櫻井祐子(訳)「イノベーション・オブ・ライフ」 翔泳社 (2012年)

- [31] クレイトン・クリステンセン、ジェフリー・ダイアー、ハル・グレガーセン(著), 櫻井祐子(訳) 「イノベーションの DNA 破壊的胃のベータの5つのスキル」, Harvard Business School Press (2001年)