# 高信頼・低特性オン抵抗 100V デュアル RESURF LDMOS のスイッチング損失の検討

小島 潤也\* 松田 順一 築地 伸和 神山 雅貴 小林 春夫(群馬大学)

**キーワード**: 横方向拡散 MOS, 信頼性, 電流増大, カーク効果, オン抵抗, スイッチング損失 (LDMOS, reliability, current expansion, Kirk effect, on-resistance, switching loss)

## 1. はじめに

民生用の電源等の回路に多く用いられている LDMOS (Lateral Double-diffused MOSFET) を車載用に展開する 場合、より一層の高い信頼性と広い SOA (Safe Operating Area) が要求される。このためには、LDMOS の中の真性 MOSFET のドレイン側ゲート端周りでのインパクトイオ ン化による電子正孔対の発生を低減し、Kirk 効果(1)による ドレイン電流の増大 (Current Expansion: CE)(2)(3)を抑制 する必要がある。また、LDMOS 本体を ESD (Electro-Static Discharge) 素子として兼用する場合、ドレインのブレーク ダウンはバルクの pn 接合で発生させる必要がある。これら の要件を満たし、かつ低特性オン抵抗を持つ 30~50V 動作 のデュアル RESURF LDMOS トランジスタが既に報告 (4)(5)(6) されている。また、その LDMOS 構造を基に 100V 動 作用の LDMOS も提案(<sup>7)</sup>されている。今回、100V 動作用 LDMOS の特性の最適化を図り、スイッチング損失につい て検討した。

## 2. 従来型と提案型 LDMOS 構造

## 〈2·1〉LDMOS の構造

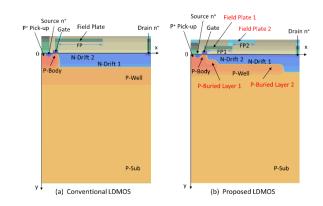

図 1 に単純な構造である従来型、及び電流増大を抑えパラメータの最適化を行った提案型の断面構造図を示す。提案型は従来型をベースにドリフト層を 2 段階(デュアル)の P・埋め込み層で囲ってある。 P・埋め込み層 2 はドリフト層全体の RESURF (Reduced Surface Field)を強め、P・埋め込み層 1 はゲート近傍のドリフト層内の RESURFを一層強化している。FP (Field Plate)は 2 段階になっており、埋め込み層による RESURF を補足している。これらのRESURFにより、提案型ではドリフト層の上層部分のドーズ量を従来型より増加してあり、SOA の強化と低オン抵抗化を図っている。

#### 〈2·2〉シミュレーションによる解析方法

$0.35 \mu m$  CMOS プロセスをベースに、デバイス・シミュレータを用いて不純物プロファイルを関数入力し、従来型と提案型 LDMOS 構造を形成した。ここで、ゲート酸化膜厚は 12 n m、ゲート長は  $0.35 \mu m$ 、ゲート幅は  $0.2 \mu m$ 、ドリ

フト長 (ゲート端~ドレイン端) は 5.55μm である。

用いたデバイス・シミュレータはアドバンスソフト社の 3 次元 TCAD の中の Advance/DESSERT (サンプル版) である。このシミュレータは 3 次元機能を有するが、2 次元で本解析を行なった。

図1 従来と提案型 LDMOS の断面図

Fig. 1. Cross sectional views of the conventional and the proposed LDMOS.

# 3. 各構造の特性比較

## 〈3·1〉電気的特性

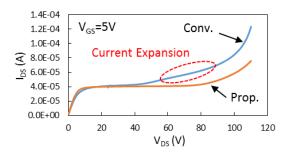

図2に従来型と提案型の $I_{DS}$ - $V_{DS}$  特性 ( $V_{CS}$ =5V) を示す。 従来型では Kirk 効果により CE が発生している。しかし、提案型ではデュアル RESURF 構造により CE の発生はない。また、 $I_{DS}$ - $V_{DS}$  特性から特性オン抵抗値  $R_{on}A$  は、従来型で  $178m\Omega\,mm^2$ 、提案型で  $150m\Omega\,mm^2$  となり、提案型で減少している。

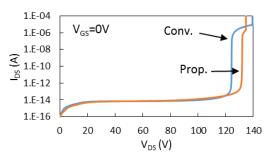

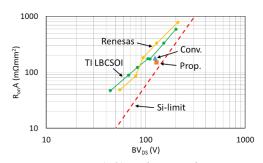

図 3 に従来型と提案型のブレークダウン特性を示す。この図からブレークダウン電圧  $BV_{DS}$  (at  $I_{DS}=1\times10^{-13}$ A) は、従来型で 124V、提案型で 128V である。 $BV_{DS}$  は提案型で高くなっているが、100V 動作の場合、両構造で問題ないと考える。このとき、提案型の $R_{on}A$ - $BV_{DS}$  のトレードオフ特性は、最先端レベルにある(図 4)。

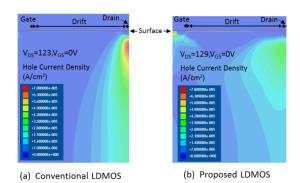

次に、図 5 に従来型と提案型のブレークダウン時の正孔 電流密度分布を示す。これは、ブレークダウン時に構造上 のどこで多くインパクトイオン化による正孔電流が流れているかを示す図であり、この密度が高い(ソース近傍を除く)ところがブレークダウン箇所である。どちらもドレイン下のバルク中で正孔電流密度が高くなっており、その個所でブレークダウンが発生している。したがって、両構造でブレークダウン時にインパクトイオン化によって発生する電子・正孔の酸化膜中へのトラップ、または界面への影響は抑えられ、ESD時の特性変動は少ないと考える。

図 2 IDS-VDS 特性

Fig. 2. IDS-VDS characteristics.

図3 ブレークダウン特性

Fig. 3. Breakdown characteristics.

図 4 特性オン抵抗-ブレークダウン特性

Fig. 4. RonA-BVDS characteristics.

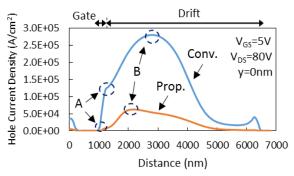

# 〈3·2〉界面の正孔電流密度と電界強度

図 6、7に従来型と提案型の界面に沿う正孔電流密度分布 (y=0) を示す。真性 MOSFET の特性に最も影響を与える ゲート側ドリフト端 (A の箇所) での提案型の正孔電流密度は、従来型に比べて一桁以上低下している。ホットキャリアによる特性劣化寿命 MTTF (Mean Time To Failure)が、DAHC (Drain Avalanche Hot Carrier) 注入の場合、基板電流 (この場合、ゲート側ドリフト端での正孔電流密

図5 ブレークダウン時の正孔電流密度分布

Fig. 5. Hole current density distributions at the breakdown voltages.

図 6 界面の正孔電流密度の分布

Fig. 6 Hole current density profiles along the surface.

図7 界面下の正孔電流密度の分布

Fig. 7. Electric field profiles along near the surface.

度)のべき乗 ( $\sim$  -3 乗)に比例する $(^{(0)}$ ことを考慮すると、提案型のホットキャリア耐性は従来型より十分にあるものと考える。

図6のBの箇所で見られる正孔電流密度のピークは、ドリフト層内部でインパクトイオン化により発生した正孔が界面に流れ込んだことによる<sup>(7)</sup>。したがって、界面では正孔のエネルギーはインパクトイオン化した時点より低減しており、この高い正孔電流密度が直接界面にダメージを与える可能性は低いものと推測する。

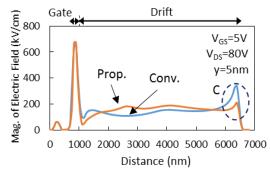

図 7 に従来型と提案型の界面に沿う電界強度分布 (y=5nm) を示す。ドリフト領域のドレイン側 (C の箇所) では、Kirk 効果により従来型と提案型ともにピークを持つ

が、後者のピークは前者より低く抑えられている。このことが、図2の提案型の特性において CE の発生が見られないことに繋がる。

## 4. スイッチング損失の考察

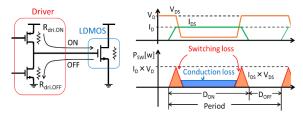

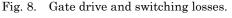

LDMOS を電源回路のスイッチング素子として用いるときに消費する損失を考える。スイッチング時の損失には、①LDMOS のゲート容量を充放電する際に生じるゲートドライブ損失と(図 8(a))、②過渡的に LDMOS のドレイン・ソース間を流れる電流とそこに掛かる電圧によるスイッチング損失がある (図 8(b))。また、導通時の損失として、導通損失がある (図 8(b))。

ゲートドライブ、スイッチング、及び導通の損失を取り込んだスイッチング特性の性能指数 FOM (figure of merit) =  $R_{on}A \times Q_g$  は、従来型では  $332m\Omega nC$ 、提案型では  $312m\Omega nC$  となった。ここで、 $Q_g$  は単位面積当たりの充電時のゲート電荷量であり、図 9 の回路条件でシミュレーションから得られた。提案型の FOM は従来型より低くなっており、提案型のスイッチング素子としての損失は従来型より小さいことが分かる。提案型のミラー容量は 2 段階の FP により従来型より増大するため、 $Q_g$  は増大するが、提案型の  $R_{on}A$ がそれ以上に小さいことが、FOM の低下を引き起こしている。

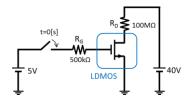

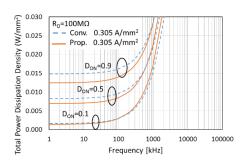

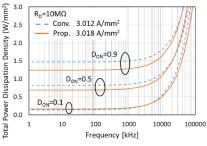

次に、図9の負荷抵抗 RDとデューティ比 Donの値を変 えて全損失密度のスイッチング周波数依存性を図 10 に示 す。全損失密度は、ゲートドライブ損失密度、スイッチン グ損失密度、及び導通損失密度を合計したものである。全 損失密度は周波数が高くなってくると次第に急上昇を始め る。この急上昇は RD の増大と共に周波数の低い方にシフト している。これは、RDが大きいほど導通損失は低下するが、 スイッチング時の損失がほとんど変化しないことによる。 この上昇の特性を提案型と従来型で比較すると、低周波領 域において提案型は従来型より低いが、周波数が高くなる につれてそれは逆転する。この現象は、低い周波数領域で は提案型の低 RonA による低伝導損失に起因しており、周波 数が高くなるにつれて提案型のスイッチング時の大きな損 失が顕著になることによる。また、この逆転する周波数は Don の増大と共に高くなる。これは、Don の増大と共に伝 導損失の割合が増えることによる。

上記逆転する周波数を  $D_{ON}$  と  $R_D$  の組み合わせで表 1 に示す。この周波数は、100kHz (at  $D_{ON}$ =0.1、 $R_D$ = $100M\Omega$ ) から 30MHz (at  $D_{ON}$ =0.9、  $R_D$ = $10M\Omega$ ) まで変化する。仮に DC-DC コンバータのスイッチング周波数を数百 kHz 程度、 $R_D$ = $50M\Omega$  とした場合、提案型の全損失密度は  $D_{ON}$  の広い範囲で従来型より低い。

(a) Gate drive loss (b) Switching loss 図 8 ゲートドライブ損失とスイッチング損失

図9 過渡解析時のシミュレーション回路

Fig. 9 Simulation circuit for transient analysis.

(a) Loss at  $R_D=100M \Omega$

(b) Loss at  $R_D=50M \Omega$

(c) Loss at R<sub>D</sub>=10M Ω

図 10 全損失密度のスイッチング周波数特性

Fig. 10. Switching frequency dependence of total power dissipation density.

# 表 1 図 10 で提案型と従来型の特性が交差するスイッチ ング周波数 (kHz)

Table 1. Switching frequency at which the characteristics of the proposed and the conventional LDMOS in Fig. 10 cross.

| $D_{ON}$ $R_{D}$ $(M\Omega)$ | 100  | 50   | 10    |

|------------------------------|------|------|-------|

| 0.1                          | 100  | 400  | 4000  |

| 0.5                          | 600  | 2000 | 20000 |

| 0.9                          | 1000 | 3000 | 30000 |

## 5. まとめ

従来型 LDMOS 構造に対して、p 埋め込み層と FP を 2 段階にしてドリフト層の RESURF を強化した LDMOS を提案し、その LDMOS の静特性とスイッチング特性をシミュレーションで確認した。本構造では、インパクトイオン化の低減によりホットキャリア耐性を高め、Kirk 効果によるドレイン電流の増大を抑制できた。提案型の特性オン抵抗値は  $150 \mathrm{m}\,\Omega\,\mathrm{mm}^2$ 、ブレークダウン電圧  $BV_{DS}$  は 128V となっており、 $R_{on}A$ - $BV_{DS}$  特性は最先端レベルにある。更に、提案型のブレークダウンの箇所は、従来型と同様にバルクであるため、ブレークダウン時にゲート酸化膜へのダメージはなく、提案型の ESD 耐性は従来型と同程度に高いものと考える。提案型のスイッチング特性の性能指数 FOM (= $R_{on}A \times Q_g$ ) は従来型の  $332 \mathrm{m}\,\Omega\,\mathrm{n}\,\mathrm{C}$  から  $312 \mathrm{m}\,\Omega\,\mathrm{n}\,\mathrm{C}$  になり、スイッチング素子としての損失を低減できた。

#### 謝辞

本研究で用いた3次元TCADは、アドバンスソフト社から借用させて頂いているものであり、アドバンスソフト社に深謝申し上げる。

## 文 献

- (1) C. T. Kirk: "A Theory of Transistor Cutoff Frequency (ft) Falloff and High Current Densities", IRE Transactions on Electron Devices, Vol. 9, No. 2 pp.164–174(1962).

- (2) Chih-Chang Cheng, H. L. Chou, F. Y. Chu, R. S. Liou, Y. C. Lin, K. M. Wu, Y. C. Jong, C. L. Tsai, C.L. Jun Cai, and H. C. Tuan: "Investigation of Parasitic BJT Turn-on Enhanced Two-stage Drain Saturation Current in High-voltage NLDMOS", 23rd International Symposium on International Power Semiconductor Devices & IC's (ISPSD), pp.208–210(2011).

- (3) Jingxuan Chen: "HV EDMOS Design with Expansion Regime Suppression", Master Thesis of Applied Science, Department of Electrical and Computer Engineering, University of Toronto, (2013).

- (4) 松田順一,神山雅貴,築地伸和,小林春夫:「高信頼性 Nch-LDMOS の提案」,電気学会研究会,EDD-15-066,SPC-15-148 (2015 年).

- (5) 松田順一, 小島潤也, 神山雅貴, 築地伸和, 小林春夫: 「高信頼性・低オン抵抗デュアル RESURF Nch-LDMOS の提案」,第63回応用物理学会春季学術講演会,東工大,20a-S422-11 (2016).

- (6) Jun-ya Kojima, Jun-ichi Matsuda, Masataka Kamiyama, Nobukazu Tsukiji, Haruo Kobayashi : "Optimization and Analysis of High Reliability 30-50V Dual RESURF LDMOS", IEEE 13th International Conference on Solid-State and Integrated Circuit Technology, Hangzhou, China (2016).

- (7) 松田順一, 小島潤也, 築地伸和, 神山雅貴, 小林春夫:「高信頼性・低特性オン抵抗 100V デュアル RESURF LDMOS トランジスタ」,電気学会研究会, EDD-16-071, SPC-16-158 (2016 年).

- (8) C. Hu, S. C. Tam, F.-C. Hsu, P.-K. Ko, T.-Y. Chan, and K. W. Terrill: "Hot-electron-induced MOSFET degradation, monitor, and improvement", IEEE Trans. Electron Devices, Vol. 32, No. 2, pp.375-385 (1985)2, pp.375-385 (1985).