# 90 nm N チャネル MOSFET での 飽和速度パラメータ抽出の新アプローチ

高橋莉乃\*, 青木均, 築地伸和, 東野将史, 澁谷将平 栗原圭汰, 小林春夫(群馬大学)

## A New Approach for Velocity Saturation Calculations of 90 nm N channel MOSFET

Rino Takahashi\*, Hitoshi Aoki, Nobukazu Tsukiji, Masashi Higashino, Shohei Shibuya, Keita Kurihara, Haruo Kobayashi (Gunma University)

#### Abstract

The drain current equations in the saturation region are the key to characterize and simulate MOSFET devices. It is difficult to obtain so-called pinch-off currents,  $I_{ds,sat}$ , for saturation current characterizations. In this research, we propose an extraction method for the velocity saturation parameter,  $\nu_{sat}$ , by using  $I_{ds}$  versus  $V_{ds}$  measurement of an N channel MOSFET with 90 nm process. As far as we investigated, there is only one paper which describes  $\nu_{sat}$  extraction for early CMOS process devices; however this is not applicable to advanced fine CMOS device. The extracted  $\nu_{sat}$  using our proposed method reasonably agreed with measured data without using global optimization functions.

キーワード:デバイスモデリング, MOSFET, 速度飽和, ピンチオフ電圧, 飽和領域, バルクチャージ, 直列抵抗 (device modeling, velocity saturation, pinch off voltage, bulk charge, series resistance)

## 1. はじめに

MOSFET をはじめとする電界効果トランジスタ (例えば近年車載電子機器などに使用されている高耐圧用 LDMOSトランジスタ,窒化ガリウム化合物トランジスタ) の特性解析では、ドレイン電流特性が線形から飽和領域に移行するポイントを正確に求めることが重要である。このポイントはピンチオフと呼ばれ、ここでの電流を  $I_{ds\_sat}$ 、電圧を  $V_{ds\_sat}$ と表わす。最大電界においてピンチオフポイントで、多数キャリアの速度飽和が起きている。この速度飽和パラメータは $v_{sat}$ と表し、ほとんどの電界効果トランジスタ用デバイスモデルにおいて物理パラメータとして重要である。

これまでに調査した限りでは、速度飽和の抽出に関する 発表は直列抵抗を考慮することなく飽和速度抽出を可能に する方法が1件だけ発表されている.[1] しかしこの方法 は近年のサブミクロン、ナノメータテクノロジーMOSFET など、2 重拡散層を用いたプロセス・デバイスで使用することは困難である。理由は、軽いドーピングを施した拡散層がバイアス依存を持った抵抗となり、[1]の手法が前提としている固定抵抗ではなくなるためである。特にトランジスタのチャネル長を短くしたとき、誤差は次第に大きくなる。このことから、筆者らは改良案としてチャネル長が直線的に  $L_{m,inf}$ ( $1/I_{ds,sat}$ )に依存することを利用し、オーバードライブ電圧を変えた方法を提案した。[2] そこでは飽和速度が実際の値より大きく評価されていた。そこで本研究では高精度コンパクトモデルとして回路シミュレーションで使用されている BSIM4 モデル [3]のモデル式を用いて直列抵抗を考慮し高精度モデリングを実現した。

## 2. ナノメータ MOSFET における vsat の導出

バルクチャージを考慮しない長チャネルの MOSFET では 飽 和 電 圧 は  $V_{gs} - V_{th}$  に 等 し く , ド レ イ ン 電 流 は

$((V_{qs} - V_{th}) * V_{ds} - V_{ds}^2)/2$ に比例する. バルクチャージを 考慮したとき、特にディープサブミクロン、ナノメータプ ロセスにおける,  $V_{ds,sat}$ と  $I_{ds}$ は, BSIM4 モデルにおいて 以 下の方程式を満たすようにポアソン方程式を一から解き直 して導出されている.

$$V_{ds,sat} = \frac{V_{gst}}{A_{bulk}} \quad (1)$$

$$I_{ds} = \frac{W_{eff}}{L_{eff}} \mu_{eff} C_{ox} \left( V_{gst} \cdot V_{ds} - \frac{1}{2} A_{bulk} V_{ds}^2 \right) \quad (2)$$

加えて、これら式(1)、(2)内のバルクに関する内部変数 Abulk については、以下のように示される.

$A_{bulk}$

$$= \left(1 + \frac{K_1}{2\sqrt{(\emptyset_s - V_{bs})}} \left\{ \frac{\left(A_0 L_{eff}\right)}{L_{eff} + 2\sqrt{X_j X_{dep}}} \cdot \left( \left[1 - A_{gs} V_{gst} \left(\frac{L_{eff}}{L_{eff} + 2\sqrt{X_j X_{dep}}}\right)^2\right] \right) + \frac{B_0}{W_{eff} + B_1} \right\}$$

$K_1$ ,  $A_0$ ,  $A_{gs}$ ,  $B_0$ ,  $B_1$ はモデルパラメータである.  $L_{eff}$ ,  $X_i$ ,  $X_{dep}$  はそれぞれ、実効チャネル長、接合深さ、空乏層 幅を表す。BSIM4 のマニュアルより、 $L_{eff}$ が十分に小 さいとき, Abulk は1と近似できる. これらを用いて, ピンチオフ電圧  $V_{ds,sat}$ のときの飽和電流  $I_{ds,sat}$ は以下 のように示される.

$$I_{ds,sat} = W_{eff} C_{ox} (V_{gst} - A_{bulk} V_{ds,sat}) \nu_{sat}$$

(4)

$$V_{ast} = V_{as} - V_{th}$$

(5)

式(4),(5)より,飽和速度 $\nu$ satについて変形し以下の式 を得た.

$$u_{sat} = \frac{I_{ds,sat}}{W_{eff}C_{ox}(V_{gst} - V_{ds,sat})}$$

$$(L_{eff} < 90 nmのとき) (6)$$

3. 測定データからのVsat抽出手法 使用した 90 nm N チャネル MOSFET は、酸化膜 厚  $T_{ox}$ = 2.5 nm, マスクチャネル長  $L_{mask}$ = 0.1  $\mu$ m, マ スクチャネル幅  $W_{mask}$ = 10  $\mu$ m を測定した.

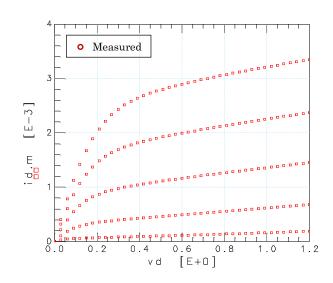

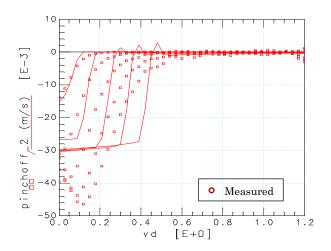

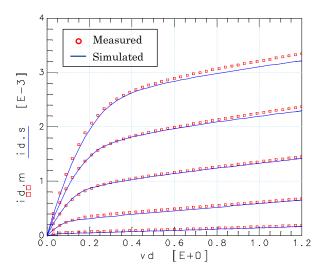

飽和速度  $\nu_{sat}$ の導出は、実効チャネル幅  $W_{eff}$ , 単位 面積当たりのゲート容量  $C_{ox}$ , しきい値電圧  $V_{th}$ , ピン チオフ電圧  $V_{ds,sat}$ , 電流  $I_{ds,sat}$ , 同点におけるゲートソ ース電圧  $V_{gs}$ の測定に基づく. 先の3つの内部変数は 各トランジスタにおいて定数となる. 以下に, 本研究 における  $V_{ds.sat}$ ,  $I_{ds.sat}$ ,  $V_{gs}$ , の導出の手順を示す. こ れらの測定には90 nm N チャネル MOSFET の Ids- $V_{ds}$ のグラフ (図 1) を用いた. ピンチオフ点をそれぞ れ導出するため  $I_{ds}$  $-V_{ds}$ グラフを二階微分した. 二階 微分したグラフは図2のようになり、一定の値が得ら れた. この値による補助線との交点を順に  $V_{ds.sat1}$ ,  $V_{ds,sat2}$ , …とし  $V_{ds,sat}$ に対して 5 点の値を得た.

図 1 90 nm N チャネル MOSFET の Ids-Vds 特性 Fig. 1.  $I_{ds}-V_{ds}$  measurement of the 90 nm N

channel MOSFET ( $L_{mask} = 0.1 \mu m$ ,  $W_{mask} = 10 \mu m$ ).

図 2 I<sub>ds</sub>-V<sub>ds</sub> 特性を 2 階微分したグラフ

Fig. 2. Second order derivative of the  $I_{\rm ds}\!-\!V_{\rm ds}$  characteristics.

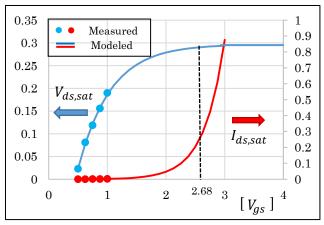

$V_{ds,sat1}$ のときの飽和電流を  $I_{ds,sat1}$ ,  $V_{dsa,sat2}$ のときの飽和電流を  $I_{ds,sat2}$ , と以下順に  $I_{ds,sat}$ に対する 5 点の値を得た上でそれらをプロットした。この点を満たす曲線を,  $V_{ds,sat}$ ,  $I_{ds,sat}$ , それぞれについて関数式を作成して 5 点とのフィッティングを行った。(図 3)

$$V_{ds,sat} = PEAKV - ANG * BASE^{V_{gs}}$$

(7)

$I_{ds,sat} = ANGI * \exp(BASE * V_{gs})$

$- PEAKI$  (8)

式(7)は、最大値 PEAKVをとるため、グラフは  $V_{gs}$ の増加と共に収束した。このピークの値を  $V_{ds,sat}$  とし、同時にこの時の  $V_{gs}$  の値( $V_{gs}=2.68V$ )を測定し、さらに式(8)に代入することで、 $I_{ds,sat}$ の値を得た。

図 3  $V_{ds,sat}$ ,  $I_{ds,sat}$ のピーク関数によるフィッティング

Fig. 3. The fitting with the peak function result of

#### V<sub>ds,sat</sub> and I<sub>ds,sat</sub>.

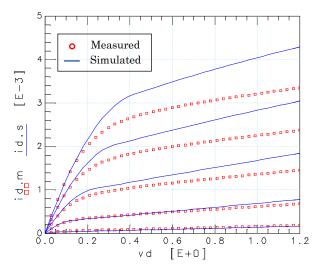

上記の手順で  $V_{ds,sat}$ ,  $I_{ds,sat}$ ,  $V_{gs}$ ,  $と \nu_{sat}$ の計算に必要な値をフィッティング関数から導出した。これらの値を用いて式(6)により飽和速度を計算すると、 $\nu_{sat}=706~\mathrm{K}$ となった。本結果をBSIM4のモデルパラメータに定義した。その他の直流ドレイン電流モデルパラメータについては事前に高精度抽出・最適化済みである。図 4のシミュレーション値は、回路シミュレータ SPICE によるシミュレーション結果である。

## 4. ソース・ドレイン直列抵抗による補正

本 90 nm プロセスの N チャネル MOSFET では、 測定時にプローブ針がパッドと接触する部分のコン タクト抵抗と、LDD の拡散層のバイアス依存抵抗が 直列に接続している。これらの抵抗により電圧降下が 起きるためデバイス内部での  $V_{ds,sat}$ は小さくなる。

ソースとドレインの合計コンタクト抵抗を  $R_X$ と定義する. また、LDD の拡散抵抗成分は BSIM4 モデルによる、単位チャネル幅の抵抗モデルパラメータ RDSWを使用し、BSIM4 モデル式を用いると、

V<sub>ds.sat new</sub>

$$= V_{ds,sat} - (RDSW[Vgs = 2.68V] \cdot W_{eff} \cdot 100$$

$$+ R_X) \cdot I_{ds,sat} \quad (9)$$

となる. ここで求めた式(9)の  $V_{ds,sat\_new}$ を式(6)に代入し直して $v_{sat}$ を再計算すると,  $v_{sat}=115~\mathrm{K}$ となった. この値を BSIM4 のモデルパラメータに定義し, 図 4 と同じ条件で SPICE シミュレーションを実施した結果を図 5 のシミュレーション・プロットに示した.

## 5. 測定データによるν<sub>sat</sub>値の検証

本実験の考案モデルにより導出した、 $\nu_{sat} = 706 \, \mathrm{K}$  について、測定データと比較・検証したものが図 4 となる.  $I_{ds}$  の微小部分ではよく一致しているが、増加に伴い次第に誤差が大きくなることがわかる. これは前項で述べた通り、コンタクト抵抗と拡散抵抗による直

列抵抗を考慮していないことによる誤差である. これらを考慮し式(9)を用いて再計算した値は  $v_{sat} = 115 \, K$ であり、測定データとの検証のグラフが図 5 である. 大電流部分で誤差がみられるが、図 4 と比較して測定値とよく一致している.

図4 補正前の考案モデルによる Ids-Vds 特性

Fig. 4.  $I_{ds} - V_{ds}$  characteristics based on the new model before correction.

図5 直列抵抗による補正後の Ids-Vds 特性

Fig. 5.  $I_{\rm ds} - V_{\rm ds}$  characteristics based on the new model corrected by series resistance.

#### 6. まとめ

本論文では $v_{sat}$ の新しい抽出方法を提案した. ナノメータ MOSFET の測定データを用いた実験では,高精度な抽出結果を得られた. 本手法は,BSIM4 モデルに基づいた近年のプロセス・デバイスにも応用可能な方法である. 本手法による $v_{sat}$ の抽出は,MOSFET 以外にも,多くの電界効果トランジスタで用いることが可能であるため,極めて有効である.

今後は[1]の手法を参考に、同プロセス内のゲート・チャネル長を変えたデバイス測定を行い、チャネル内部の抵抗を高精度に抽出する手法を検討する予定である。これによりゲートバイアス電圧依存の直列抵抗による高精度な補正が可能と考えられる。

#### 参考文献

[1] R. J. Schreutelkamp, L. Deferm, "A New Method for Measuring the Saturation Velocity of Submicron CMOS Transistors", Solid-State Electronics, vol. 38, no. 4, pp.791-793 (April 1995)

[2] R. Takahashi, H. Aoki, N. Tsukiji, M. Higashino, S. Shibuya, K. Kurihara, H. Kobayashi, "Velocity Saturation Calculations for 90nm MOSFET Modeling in Saturation Regions", 8th International Conference on Advanced Micro-Device Engineering, Kiryu (Dec. 2016).

[3] BSIM4;http://decenti.ing.unipi.it/~a008309/mat\_stud/PSM/2016/Approfondimenti/bsimset.pdf

[4] H. Aoki, M. Shimasue, Y. Kawahara, CMOS Modeling Technology, Theory and Practice of Compact Model for SPICE, Maruzen (Jan 2006)