#### 電力変換効率曲線を用いた降圧形DC/DC 電源回路の回路素子値推定に関する検討

○櫻井 翔太郎 築地 伸和 小堀 康功 小林 春夫

群馬大学理工学部電子情報理工学科 通信処理システム工学第二研究室小林研究室 学部4年 櫻井翔太郎

### アウトライン

1. 研究背景と目的

2. 推定原理一DCDC電源の損失と効率

3. 推定結果

## アウトライン

1. 研究背景と目的

2. 推定原理一DCDC電源の損失と効率

3. 推定結果

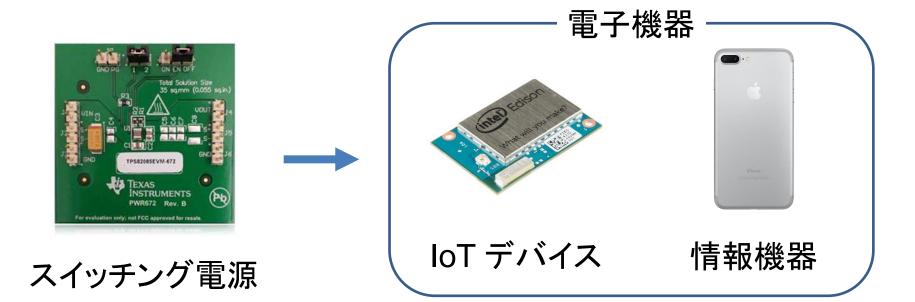

## 研究背景

電圧を降圧/昇圧する回路 小型 軽量 高効率

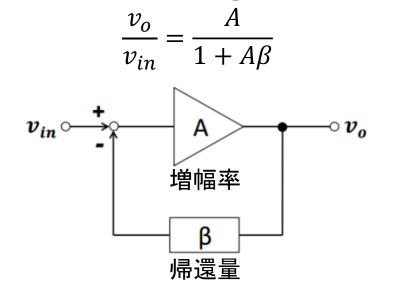

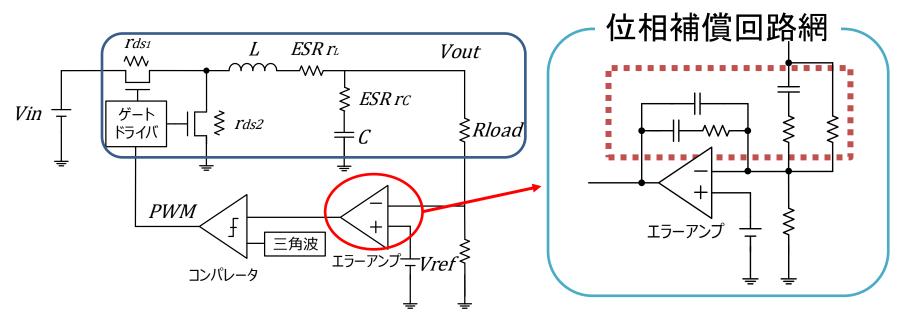

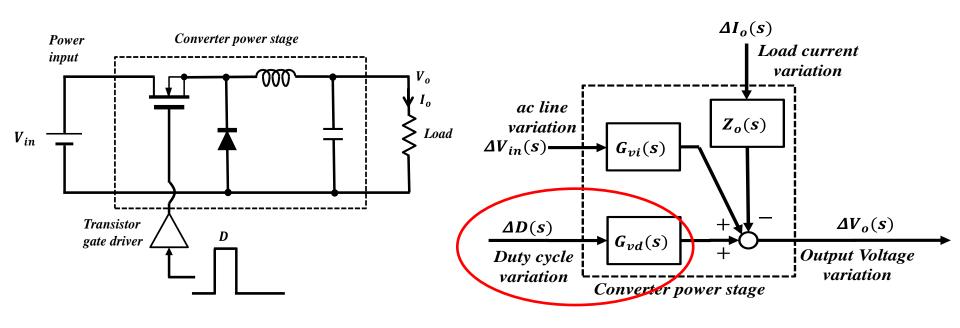

## 負帰還回路

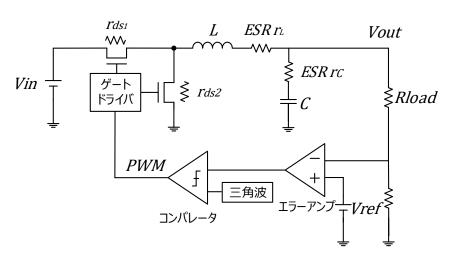

#### スイッチング電源は負帰還制御を用いる

$$A\beta = -1$$

の時、回路は発振

#### 適切な位相補償設計が必要

#### 位相補償設計

$$G_{dv}(s)\Big|_{\substack{\Delta V_i=0\\ \Delta I_o=0}} = \frac{\Delta V_o}{\Delta D} \to \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

パワーステージの伝達関数

位相補償設計に必要!

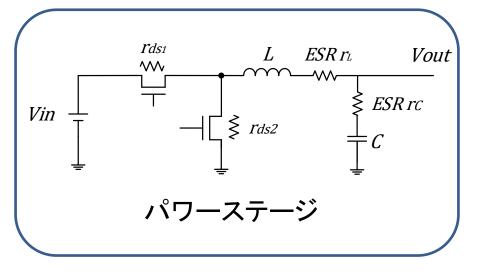

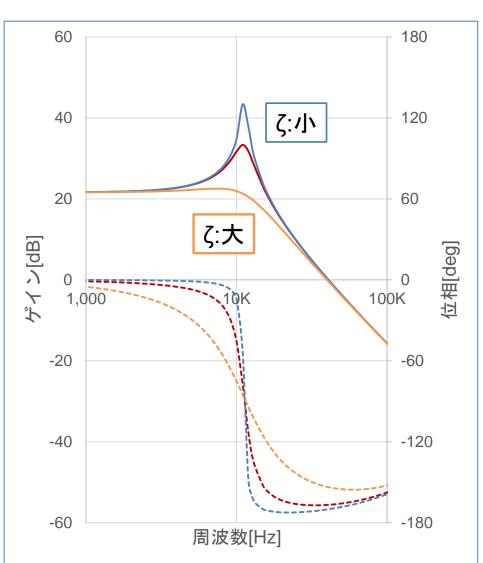

## パワーステージの伝達関数と素子値

$$G_{dv}(s)\Big|_{\substack{\Delta V_i=0\\\Delta I_o=0}} = \frac{\Delta V_o}{\Delta D} \to \frac{\omega_n^2}{s^2 + 2\underline{\zeta}\omega_n s + \omega_n^2}$$

振動係数ζが特性に関与

$$\zeta = \frac{r_L + r_{ds} + r_C}{2} \sqrt{\frac{C}{L}}$$

#### ζは回路素子値に依存

位相補償設計に 回路素子値は必須

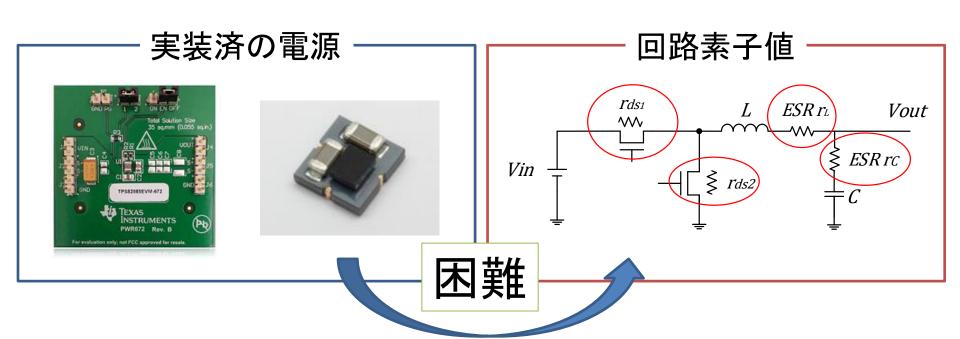

# 現状

#### 提案解決手法

#### 実装済の電源

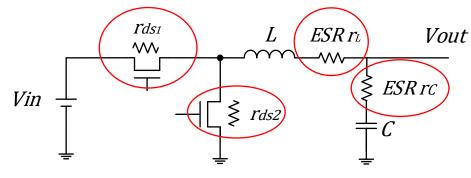

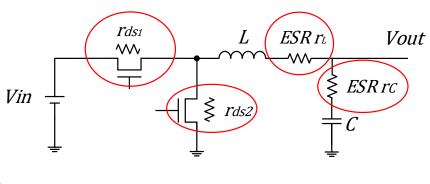

# 回路素子値 Vin Trds1 L ESR r1 Vout ESR rc C

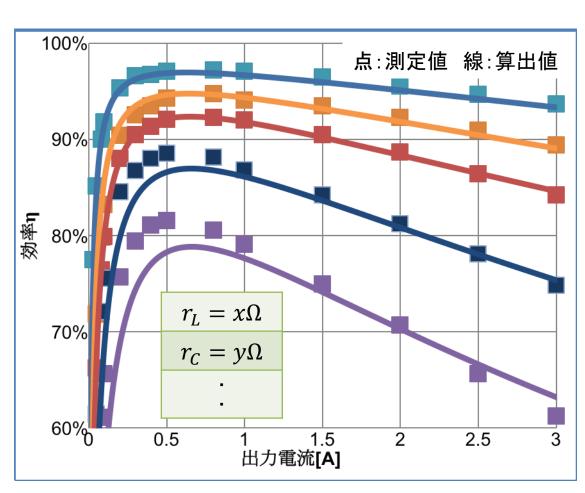

#### 測定された効率曲線

回路素子値を直接 測定せずに効率曲線から推定

#### 目的

出力電流[A]

効率η[%]

#### 損失の理論式

$$P_{sw\ loss} = \frac{1}{6} V_i I_o (\Delta T_{ON} + \Delta T_{OFF}) \cdot f_{sw}$$

$$P_L = R_L \cdot I_o^2 \qquad P_C = R_C \cdot I_C^2$$

$$\eta = \frac{V_{out} \cdot I_o}{V_{out} \cdot I_o + P_{loss}}$$

#### 回路素子值

## アウトライン

1. 研究背景と目的

2. 推定原理一DCDC電源の損失と効率

3. 推定結果

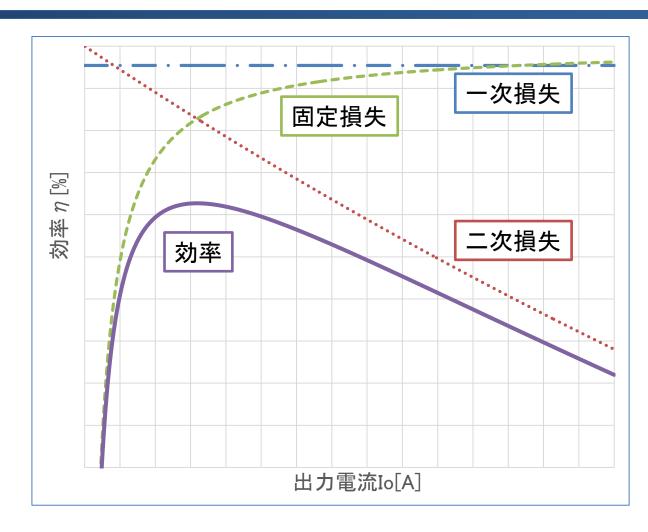

## スイッチング電源の損失

- 1. 出力電流に比例する一次損失 : $P_1[W]$  スイッチング損失

- 2. 出力電流の二乗に比例する二次損失  $:P_2[W]$  導通損失

- 3. 出力電流に依存しない固定損失 : $P_{const}[W]$

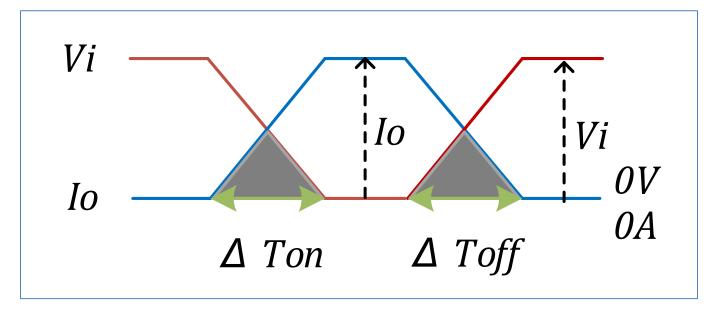

## P<sub>1</sub> -スイッチング損失

#### 一次損失

$$P_{sw \ loss} = f_{sw} \left[ \int_{0}^{\Delta T_{on}} v_{tr}(t) \cdot i_{tr}(t) dt + \int_{0}^{\Delta T_{off}} v_{tr}(t) \cdot i_{tr}(t) dt \right]$$

$$= \frac{1}{6} V_{i} \cdot I_{o} (\Delta T_{oN} + \Delta T_{oFF}) \cdot f_{sw}$$

$V_i$ :ドレインソース間電圧[V]  $I_o$ :出力電流(ドレイン電流)[A]

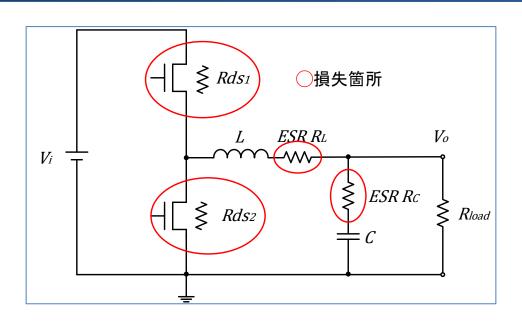

# P2 ーインダクタ、キャパシタの導通損失

#### 二次損失

ESR(Equivalent Series Resistance)

等価直列抵抗による I<sup>2</sup>R ドロップ 導線、金属皮膜の抵抗成分が起因

#### インダクタの銅損

$$P_L = R_L \cdot I_o^2$$

$R_L$ :コイルの等価直列抵抗 $[\Omega]$

$I_o$ :出力電流[A]

#### • キャパシタの損失

$R_C$ : キャパシタの直列等価抵抗 $[\Omega]$

$I_c$ : キャパシタに流れるリップル電流[A]

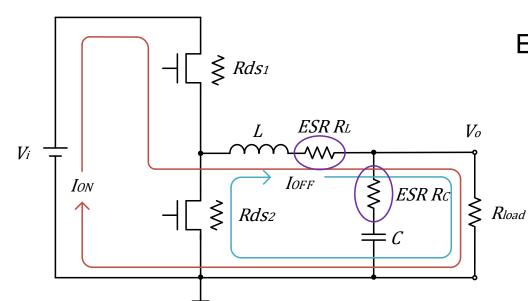

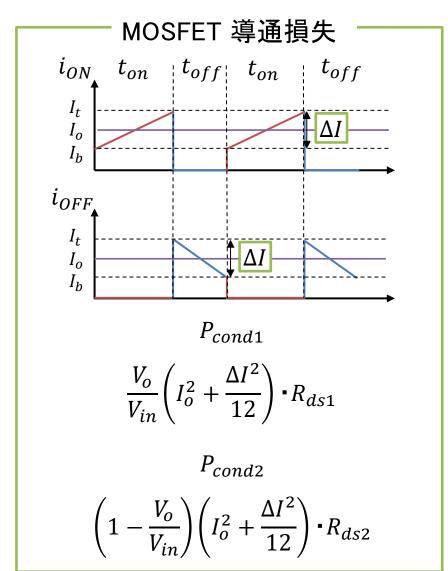

## $P_2$ —MOSFET 導通損失

#### 二次損失

$$P_{cond} = I_o^2 \left[ \frac{V_o}{V_{in}} (R_{ds1} - R_{ds2}) + R_{ds2} \right]$$

$I_o$ :出力電流[A]

Δ*I*:リップル電流[A]

$R_{DS1}$ : ハイサイドMOSオン抵抗[ $\Omega$ ]  $R_{DS2}$ : ローサイドMOSオン抵抗[ $\Omega$ ]

## スイッチング電源の損失式

次損失:*P*₁

$$P_{sw\ loss} = \frac{1}{6} V_i I_o (\Delta T_{ON} + \Delta T_{OFF}) \cdot f_{sw}$$

二次損失:P<sub>2</sub>

$$P_L = R_L \cdot I_o^2$$

$$P_L = R_L \cdot I_o^2 \qquad P_C = R_C \cdot I_c^2 \quad \text{$\%$} I_C \propto I_o$$

$$P_{cond} = I_o^2 \left[ \frac{V_o}{V_{in}} \left( R_{ds1(on)} - R_{ds2(on)} \right) + R_{ds2(on)} \right]$$

固定損失:Pconst

ゲートドライバ

エラーアンプ コントロールステージ コンパレータ の自己消費電力

パラメータとして値で与える

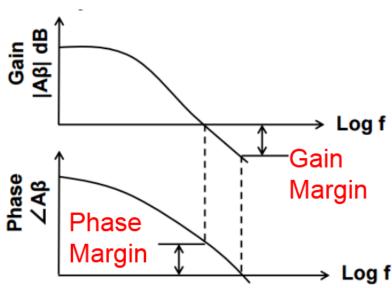

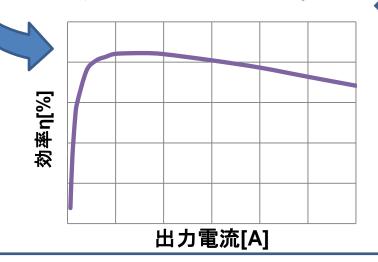

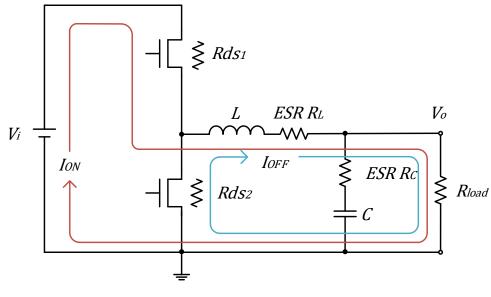

## 各損失の効率に与える影響

出力電流に対して

- 一次損失→一定

- 二次損失→単調減少

- 固定損失 →対数増加

各損失による影響を考慮しながらフィッティング

## 各損失と電力変換効率

$$\begin{aligned} P_2 &= P_{MOS} + P_L + P_C = K_2 \cdot I_o^2 \\ P_1 &= P_{sw} = K_1 \cdot I_o \\ P_{const} \end{aligned}$$

$$P_{loss} = P_2 + P_1 + P_{const}$$

#### 電力変換効率

$$\eta = \frac{V_{out} \cdot I_o}{V_{out} \cdot I_o + P_{loss}}$$

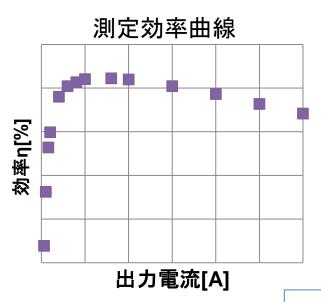

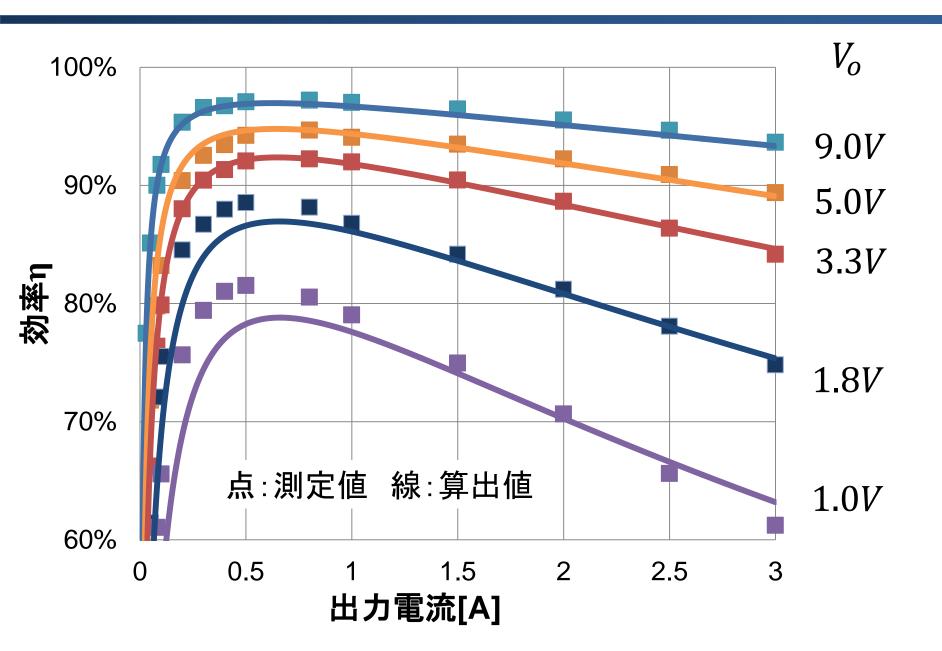

算出した効率を実測値と比較 フィッティングにより素子値を推定

## アウトライン

1. 導入

2. 推定原理一DCDC電源の損失と効率

3. 推定結果

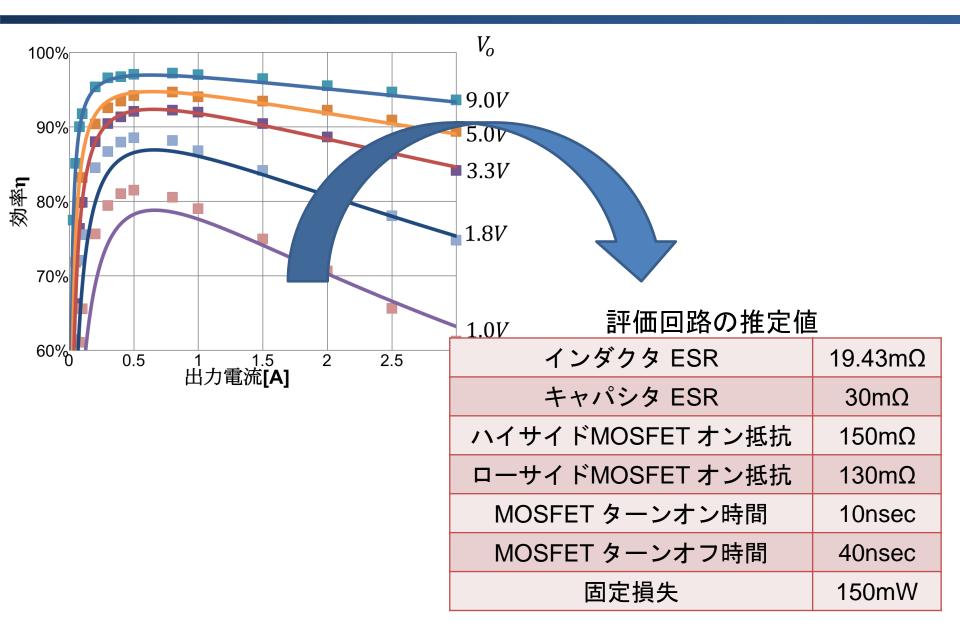

## 推定対象

- 市販の同期整流形DC/DCコンバータの評価基板を使用

- 測定した電力変換効率曲線のみを使用

#### 推定パラメータ

- □ インダクタ ESR

- MOSFETのターンオン時間

- □ 固定損失

#### □ キャパシタ ESR

- MOSFETのハイサイドのオン抵抗 MOSFETのローサイドのオン抵抗

- MOSFETのターンオフ時間

#### 評価回路の設定パラメータ

| 入力電圧 $V_i$                | 12.0V                    |  |

|---------------------------|--------------------------|--|

| 出力電圧 V <sub>o</sub>       | 1.0V/1.8V/3.3V/5.0V/9.0V |  |

| スイッチング周波数 f <sub>sw</sub> | 380kHz                   |  |

| 出力インダクタ L                 | 10µH                     |  |

| 出力キャパシタ C                 | 20µF                     |  |

## フィッティング結果

## 推定結果

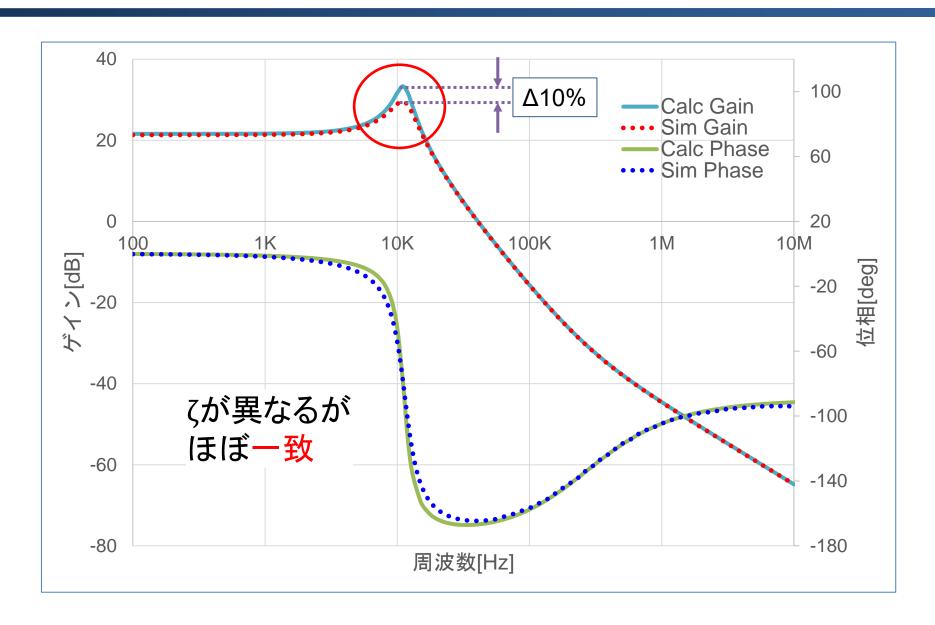

## 推定結果を用いた伝達関数の計算

位相補償設計にあたり パワーステージの伝達関数が必要

推定値を用いることで算出が可能

# パワーステージ伝達関数

#### 開ループ伝達関数

$$G_{dv}(s)\Big|_{\Delta V_i=0} = \frac{\Delta V_o}{\Delta D} = \frac{V_i \cdot \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2} \left(1 + \frac{s}{\omega_{esr}}\right)$$

$$= \frac{V_i(1 + j\omega C r_c)}{1 - \omega^2 LC + j\omega C (r_L + r_c + r_{ds})}$$

$$\zeta = \frac{r_L + r_c + r_{ds}}{2} \sqrt{\frac{c}{L}}, \ \omega_n = \frac{1}{\sqrt{LC}}, \ \omega_{esr} = \frac{1}{Cr_c}$$

#### 伝達関数のパラメータ

| スイッチング周波数 fsw                  | 380kHz | 入力電圧 $V_i$                    | 12V   |

|--------------------------------|--------|-------------------------------|-------|

| 出力インダクタ L                      | 10µH   | 出力キャパシタ C                     | 20µF  |

| インダクタ ESR $r_L$                | 19.43Ω | キャパシタ ESR $r_{C}$             | 30mΩ  |

| ハイサイド MOSFET<br>オン抵抗 $r_{ds1}$ | 150mΩ  | ローサイドMOSFET<br>オン抵抗 $r_{ds2}$ | 130mΩ |

# 推定算出値とシミュレーションの比較

## アウトライン

1. 研究背景と目的

2. 推定原理一DCDC電源の損失と効率

3. 推定結果

## まとめと課題

#### まとめ

- ・ 測定された効率曲線から回路素子値を推定する 手法を提案

- ・ 推定値を用いてパワーステージの 開ループ伝達関数を算出

#### 課題

- 実際に回路素子値が一致しているか、測定済みの 実装電源と比較

- 未着目損失の影響の検討

# ご清聴ありがとうございました

1. 研究背景と目的

2. 推定原理一DCDC電源の損失と効率

3. 推定結果

#### Q&A

Q目的は伝達関数を求めたいということで良いか?伝達関数が一致すればよいか? 宇大

A電圧モードでは位相補償の設計に伝達関数が必要となることから、伝達関数を推定し、位相補償の設計を最適化することが目的ですのでその通りである。

Qスイッチング損失の理論式が少し違うかも A再考察します。

#### Q&A

#### Q鉄損は含まれているか?

A固定損失として数値の中に入っているものとした ため、具体的な値を示してはいない。

Q位相を確保するとのことだが、実際に行っている減衰定数の整合性に関しては示した?

A今後の課題として、回路素子値を測定した実装 回路と比較する必要がある。なので今回はまだ 示せていない。