21<sup>st</sup> IEEE International Mixed-Signal Testing Workshop Catalunya, Spain

July 4, 2016 15:00-15:30

JAPAN

Conference Room: Goya

# Successive Approximation Time-to-Digital Converter with Vernier-level Resolution

R. Jiang, C. Li, M. Yang, <u>H. Kobayashi</u>, Y. Ozawa N. Tsukiji, M. Hirano, R. Shiota, K. Hatayama

Gunma University, Socionext Inc.

# Contents

- Research Objective

- TDC Application to LSI Testing Technology

- 4 Types of TDCs Developed at Gunma Univ.

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ SAR-typeTDC

- ✓ Delta-Sigma TDC

- Discussions and Conclusion

# Contents

# Research Objective

- TDC Application to LSI Testing Technology

- 4 Types of TDCs Developed at Gunma Univ.

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ SAR-typeTDC

- ✓ Delta-Sigma TDC

- Discussions and Conclusion

## **Research Objective**

Compare 4 types of

Time-to-Digital Converters (TDCs)

developed at the presenter's lab

for LSI testing technology.

Especially present details of the SAR TDC architecture and its calibration method.

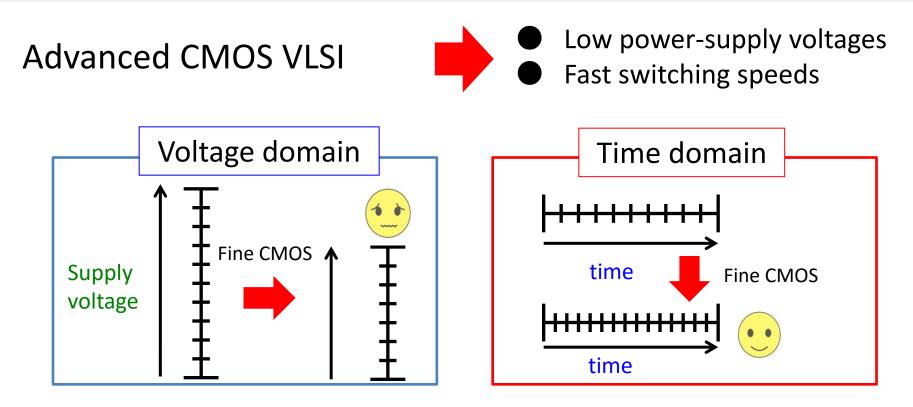

# **Research Background**

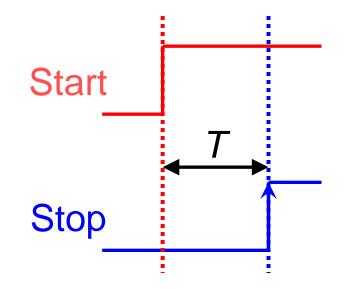

A Time-to-Digital Converter (TDC) provides a digital output proportional to the time between two clock transitions.

The TDC is a key component in time-domain analog circuits,

# (e.g. Sensor Interfaces, All-Digital PLLs, ADCs, ...)

# Time to Digital Converter (TDC)

• time interval  $\rightarrow$  Measurement  $\rightarrow$  Digital value

Start → TDC → Dout

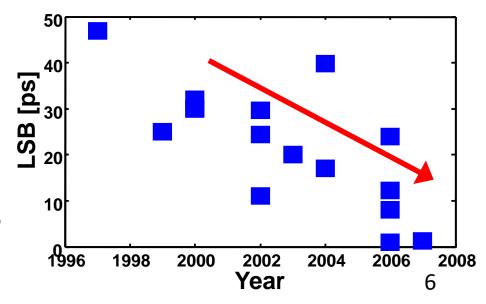

#### **Higher resolution with CMOS scaling**

- Key component of Timedomain analog circuit

- Higher resolution can be obtained with scaled CMOS

#### **Time Domain Analog Circuit Features**

Voltage domain:

Signal range : Up to power supply voltage Time domain:

Signal range : Time continues indefinitely

Large dynamic range

Time domain analog circuit :

Binary amplitude (Vss, Vdd)

# Contents

#### Research Objective

# <u>TDC Application to LSI Testing Technology</u>

- 4 Types of TDCs Developed at Gunma Univ.

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ SAR-typeTDC

- ✓ Delta-Sigma TDC

- Discussions and Conclusion

# ATE System and TDC

- "Timing" is very important in ATE systems

- Many High-performance TDCs are used there.

# Such as for Clock timing, jitter measurements

[1] K. Yamamoto,at. el. (Advantest Corp.),

"Multi Strobe Circuit for 2.133 GHz Memory Test System,"

IEEE International Test Conference, Paper 6.1 (2006).

# Analog/Mixed-Signal BIST, BOST

• TDC can be used for BIST, BOST

#### BIST, DFT

Chip design time maybe longer Chip may be larger Difficult to assure its reliability Long time-to-market Costly Should be simple

#### BOST

Design/implementation after tape out Attractive

#### I have a feeling

Japanese companies prefer BOST, US companies prefer BIST.

# Contents

- Research Objective

- TDC Application to LSI Testing Technology

# <u>4 Types of TDCs Developed at Gunma Univ.</u>

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ SAR-typeTDC

- ✓ Delta-Sigma TDC

- Discussions and Conclusion

#### 4 Types of TDCs

|                     | Clocks<br>Under<br>Test | Measurement<br>Time | Time<br>Resolution | Circuit | FPGA              |

|---------------------|-------------------------|---------------------|--------------------|---------|-------------------|

| Flash-type          | Single O<br>event       | Short 🔵             | Coarse 🔀           | Large 🔀 | Digital 🔵         |

| Gray code<br>based  | Single O<br>event       | Short 🔵             | Coarse 🔀           | Small 🔵 | Digital 🔵         |

| SAR-type            | Repetitive<br>clock     | Middle              | Middle             | Small 🔵 | Digital 🔵         |

| Delta-Sigma<br>type | Repetitive<br>clock     | Long 🔀              | Fine 🔵             | Small 🔵 | Small 🛆<br>Analog |

# Contents

- Research Objective

- TDC Application to LSI Testing Technology

- <u>4 Types of TDCs Developed at Gunma Univ.</u>

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ SAR-typeTDC

- ✓ Delta-Sigma TDC

- Discussions and Conclusion

#### 4 Types of TDCs

|                     | Clocks<br>Under<br>Test | Under Measurement Time<br>Time Resolution |          | Circuit | FPGA           |

|---------------------|-------------------------|-------------------------------------------|----------|---------|----------------|

| Flash-type          | Single O<br>event       | Short 🔵                                   | Coarse 🔀 | Large 🔀 | Digital 🔵      |

| Gray code<br>based  | Single O<br>event       | Short 🔵                                   | Coarse 🔀 | Small 🔵 | Digital 🔵      |

| SAR-type            | Repetitive<br>clock     | Middle                                    | Middle   | Small 🔵 | Digital 🔵      |

| Delta-Sigma<br>type | Repetitive<br>clock     | Long 🔀                                    | Fine 🔵   | Small 🔵 | Small <u> </u> |

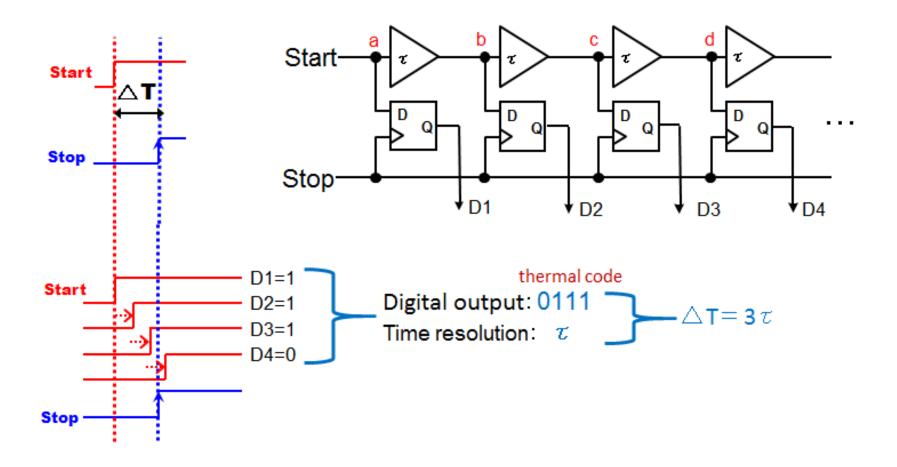

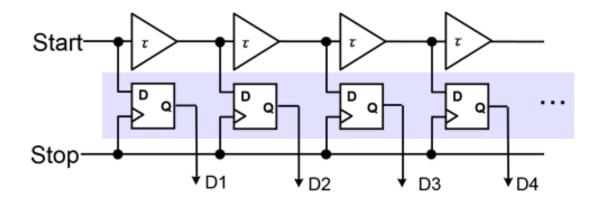

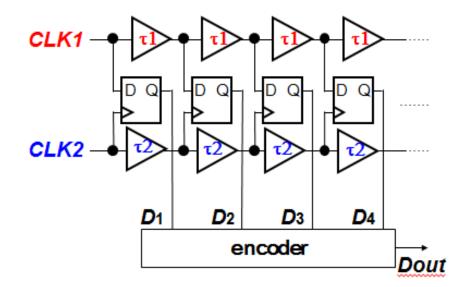

#### Flash-type TDC

#### Flash-type TDC Evaluation

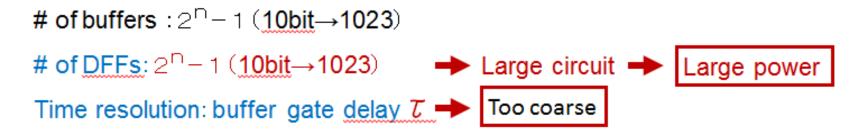

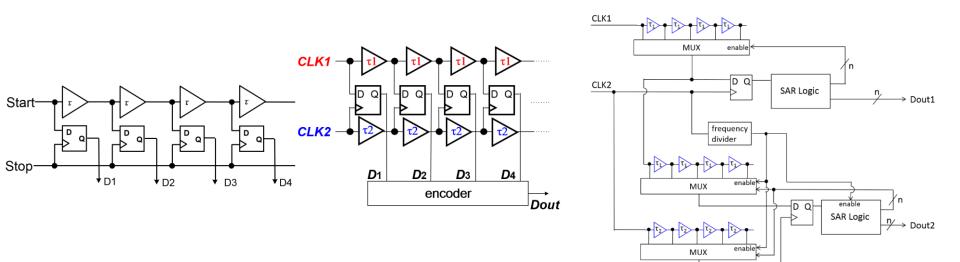

#### Vernier-type TDC

Delay:  $\tau_1 > \tau_2$ Time resolution :  $\tau_1 - \tau_2$

# Contents

- Research Objective

- TDC Application to LSI Testing Technology

- <u>4 Types of TDCs Developed at Gunma Univ.</u>

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ SAR-typeTDC

- ✓ Delta-Sigma TDC

- Discussions and Conclusion

#### 4 Types of TDCs

|                     | Clocks<br>Under<br>Test | Measurement<br>Time | Time<br>Resolution | Circuit | FPGA           |

|---------------------|-------------------------|---------------------|--------------------|---------|----------------|

| Flash-type          | Single O                | Short 🔵             | Coarse 🔀           | Large 🔀 | Digital 🔵      |

| Gray code<br>based  | Single O<br>event       | Short 🔿             | Coarse 🔀           | Small   | Digital 🔵      |

| SAR-type            | Repetitive<br>clock     | Middle              | Middle             | Small 🔵 | Digital 🔵      |

| Delta-Sigma<br>type | Repetitive<br>clock     | Long 🔀              | Fine 🔵             | Small 🔵 | Small <u> </u> |

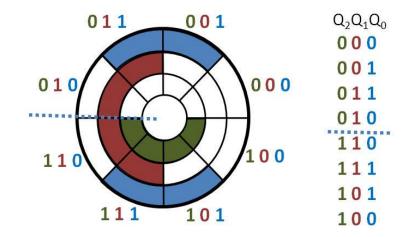

#### **Concept of Gray code**

# Gray code is a binary numeral system where two successive values differ in only one bit.

4-bit Gray code vs. 4-bit Natural Binary Code

| Decimal<br>numbers | Natural Binary<br>Code | 4-bit Gray<br>Code |  |

|--------------------|------------------------|--------------------|--|

| 0                  | 0000                   | 0000               |  |

| 1                  | 0001                   | 0001               |  |

| 2                  | 0010                   | 0011               |  |

| 3                  | 0011                   | 0010               |  |

| 4                  | 0100                   | 0110               |  |

| 5                  | 0101                   | 0111               |  |

| 6                  | 0110                   | 0101               |  |

| 7                  | 0111                   | 0100               |  |

| 8                  | 1000                   | <b>1</b> 100       |  |

| 9                  | 1001                   | 1101               |  |

| 10                 | 1010                   | 1111               |  |

| 11                 | 1011                   | 1110               |  |

| 12                 | 1100                   | 1010               |  |

| 13                 | 1101                   | 1011               |  |

| 14                 | 1110                   | 1001               |  |

| 15                 | 1111                   | 1000               |  |

FRANK GRAY and A. L. Johnsrud in television booth. Behind the glass panels at sides and top are the photo-electric cells.

Gray code was invented by Frank Gray at Bell Lab in  $194\overline{20}$

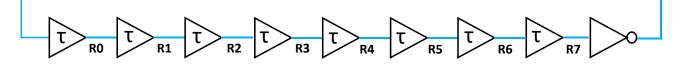

#### How to utilize Gray code in TDC

In a ring oscillator, between any two adjacent states, only one output changes at a time.

| 8-stage Ring Oscillator Output |    |    |    |    | 4-k | oit Gr | ay Co     | ode |    |    |    |

|--------------------------------|----|----|----|----|-----|--------|-----------|-----|----|----|----|

| RO                             | R1 | R2 | R3 | R4 | R5  | R6     | <b>R7</b> | G3  | G2 | G1 | G0 |

| 0                              | 0  | 0  | 0  | 0  | 0   | 0      | 0         | 0   | 0  | 0  | 0  |

| 1                              | 0  | 0  | 0  | 0  | 0   | 0      | 0         | 0   | 0  | 0  | 1  |

| 1                              | 1  | 0  | 0  | 0  | 0   | 0      | 0         | 0   | 0  | 1  | 1  |

| 1                              | 1  | 1  | 0  | 0  | 0   | 0      | 0         | 0   | 0  | 1  | 0  |

| 1                              | 1  | 1  | 1  | 0  | 0   | 0      | 0         | 0   | 1  | 1  | 0  |

| 1                              | 1  | 1  | 1  | 1  | 0   | 0      | 0         | 0   | 1  | 1  | 1  |

| 1                              | 1  | 1  | 1  | 1  | 1   | 0      | 0         | 0   | 1  | 0  | 1  |

| 1                              | 1  | 1  | 1  | 1  | 1   | 1      | 0         | 0   | 1  | 0  | 0  |

| 1                              | 1  | 1  | 1  | 1  | 1   | 1      | 1         | 1   | 1  | 0  | 0  |

| 0                              | 1  | 1  | 1  | 1  | 1   | 1      | 1         | 1   | 1  | 0  | 1  |

| 0                              | 0  | 1  | 1  | 1  | 1   | 1      | 1         | 1   | 1  | 1  | 1  |

| 0                              | 0  | 0  | 1  | 1  | 1   | 1      | 1         | 1   | 1  | 1  | 0  |

| 0                              | 0  | 0  | 0  | 1  | 1   | 1      | 1         | 1   | 0  | 1  | 0  |

| 0                              | 0  | 0  | 0  | 0  | 1   | 1      | 1         | 1   | 0  | 1  | 1  |

| 0                              | 0  | 0  | 0  | 0  | 0   | 1      | 1         | 1   | 0  | 0  | 1  |

| 0                              | 0  | 0  | 0  | 0  | 0   | 0      | 1         | 1   | 0  | 0  | 0  |

For any given Gray code, each bit can be generated by a certain ring oscillator.

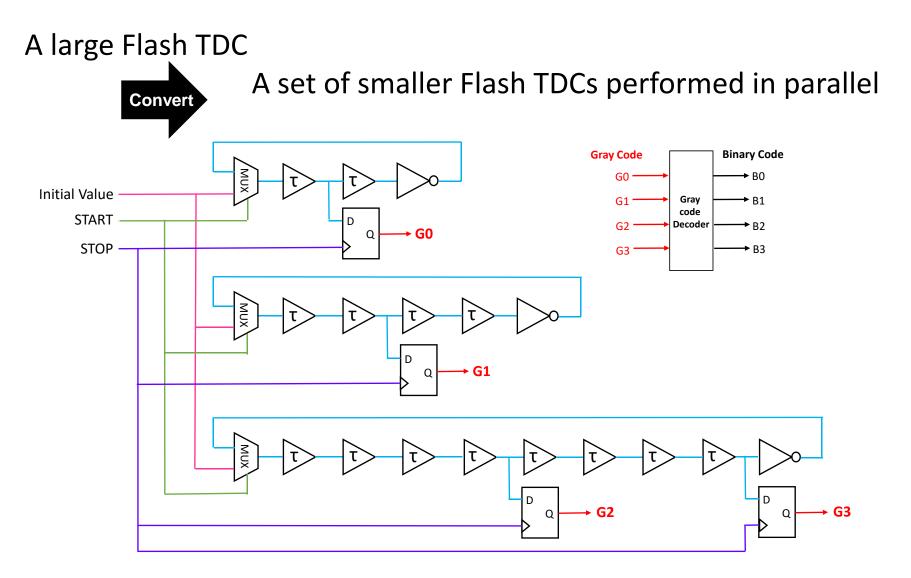

Proposed Gray code TDC architecture in 4-bit case

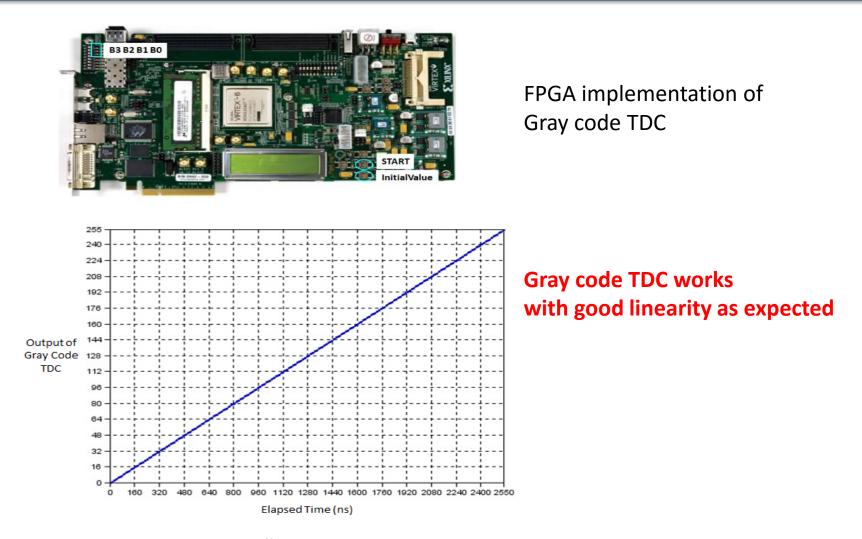

#### FPGA measurement results of 8-bit Gray code TDC

[1] C. Li, H. Kobayashi, "A Gray Code Based Time-to-Digital Converter Architecture and its FPGA Implementation", IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Sendai, Japan (Aug. 26-28, 2015).

# Flash TDC vs. Gray code TDC

|                | Number of         | Number of             | Maximum stage of        |

|----------------|-------------------|-----------------------|-------------------------|

|                | delay cells       | DFFs                  | RO                      |

| Gray code TDC  | 2 <sup>n</sup> -2 | п                     | 2 <sup><i>n</i>-1</sup> |

| Flash-type TDC | 2 <sup>n</sup>    | 2 <i><sup>n</sup></i> | 2 <sup>n</sup>          |

|                |                   |                       |                         |

For large measurement range, the number of flip-flops in Gray code TDC decreases rapidly ( $n \ll 2^n$ )

#### **Reduction of circuit complexity!!**

# Contents

#### Research Objective

TDC Application to LSI Testing Technology

# 4 Types of TDCs Developed at Gunma Univ.

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ <u>SAR-typeTDC</u>

- ✓ Delta-Sigma TDC

- Discussions and Conclusion

#### 4 Types of TDCs

|                     | Clocks<br>Under<br>Test | Measurement<br>Time | Time<br>Resolution | Circuit | FPGA              |

|---------------------|-------------------------|---------------------|--------------------|---------|-------------------|

| Flash-type          | Single O<br>event       | Short 🔵             | Coarse 🔀           | Large 🔀 | Digital 🔵         |

| Gray code<br>based  | Single O<br>event       | Short 🔵             | Coarse 🔀           | Small 🔵 | Digital 🔵         |

| SAR-type            | Repetitive<br>clock     | Middle              | Middle             | Small 🔵 | Digital 🔵         |

| Delta-Sigma<br>type | Repetitive<br>clock     | Long 🔀              | Fine 🔵             | Small 🔵 | Small 🛆<br>Analog |

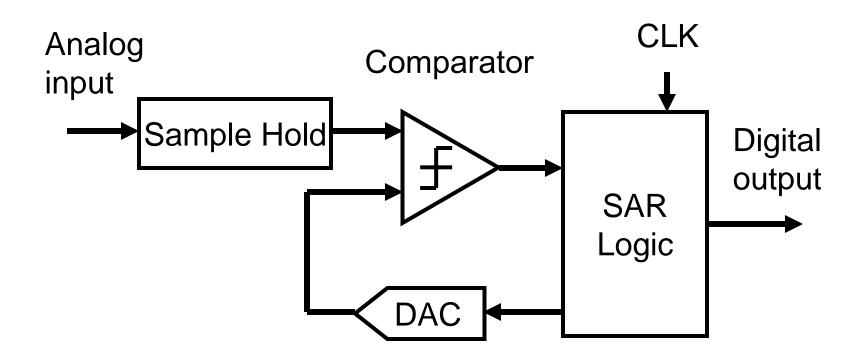

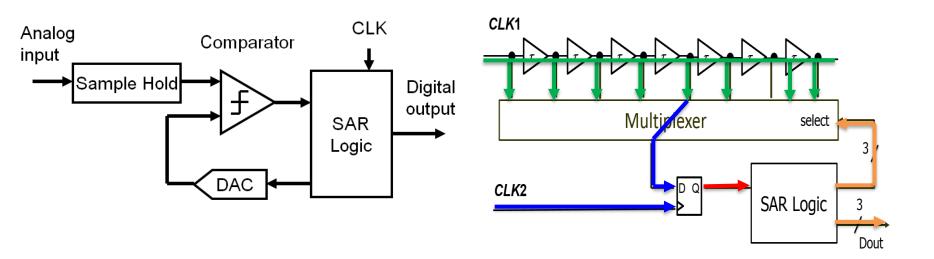

# **SAR ADC Block**

SAR ADC is digital centric.

$\rightarrow$  Suitable for fine CMOS implementation.

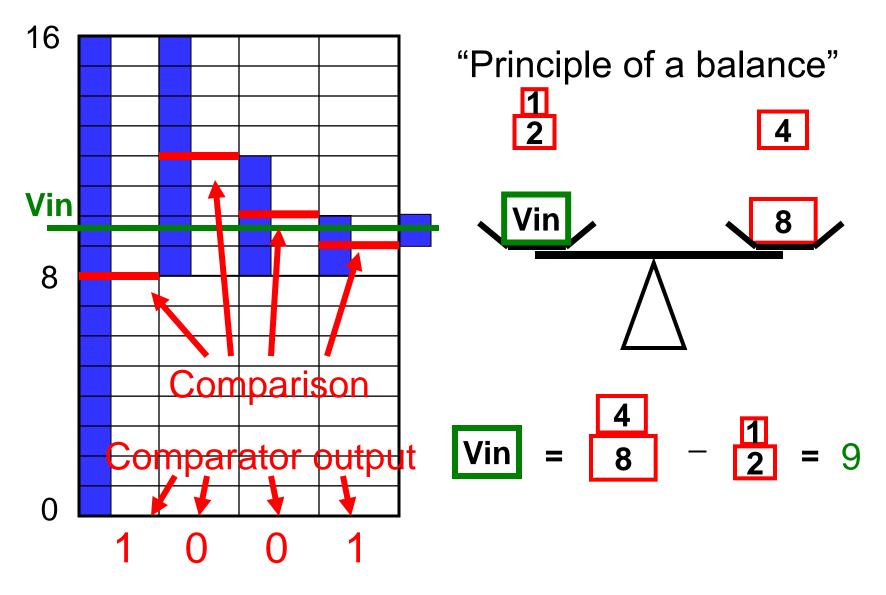

#### **SAR ADC Operation**

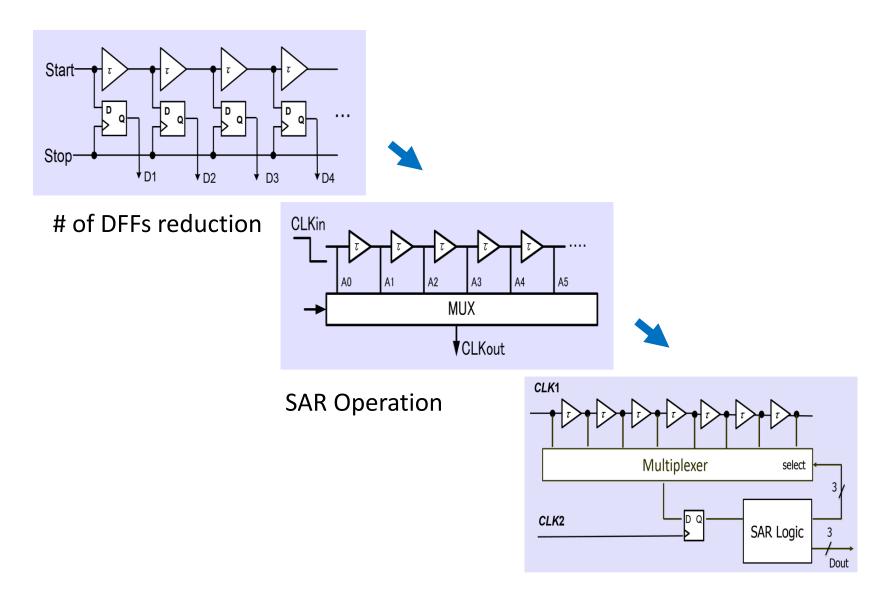

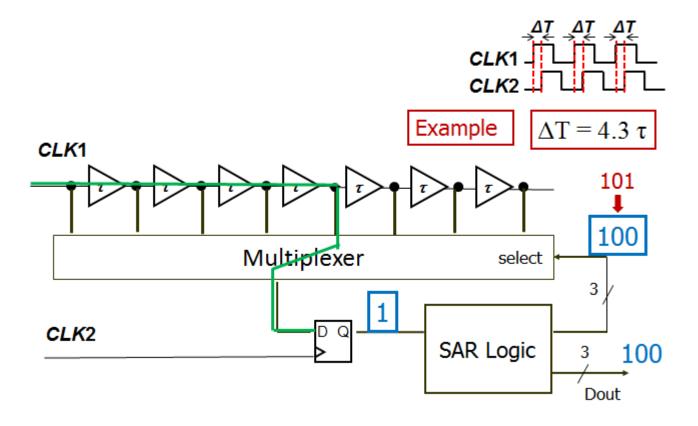

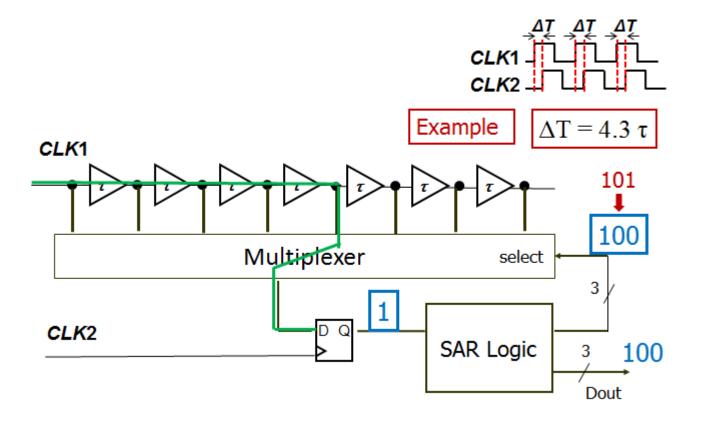

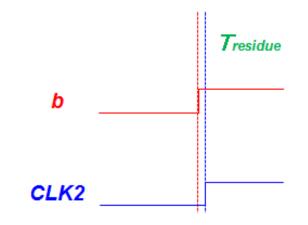

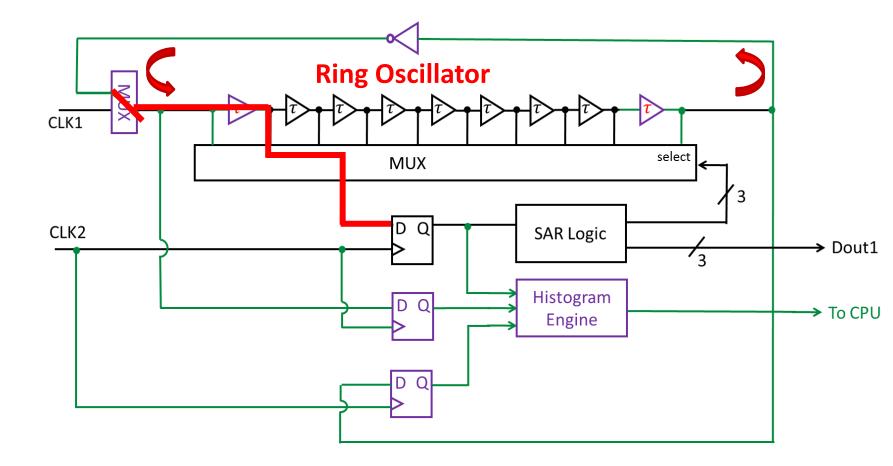

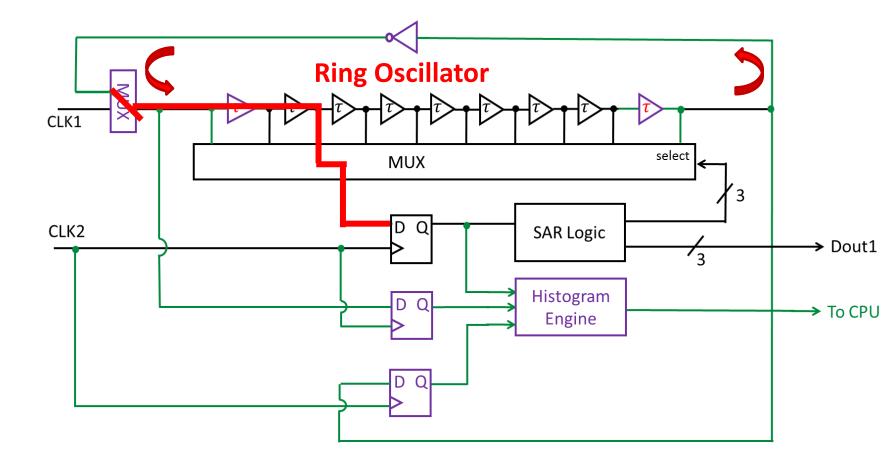

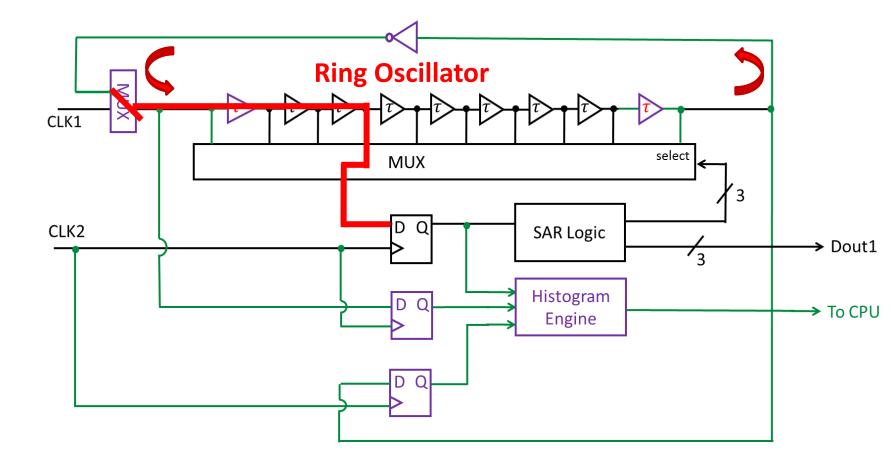

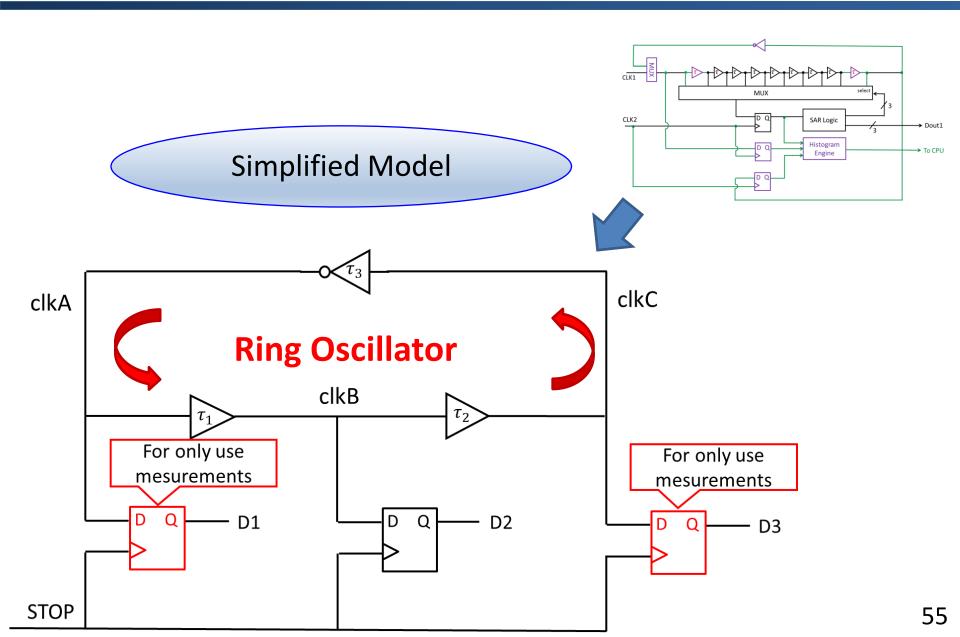

# **SAR TDC Configuration**

# SAR ADC versus SAR TDC

#### SAR ADC

- Comparator

- DAC

SAR TDC • DFF

• Delay chain, MUX

#### SAR TDC Operation Step 4 Steady State

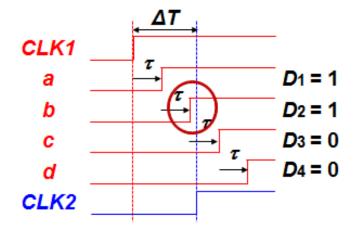

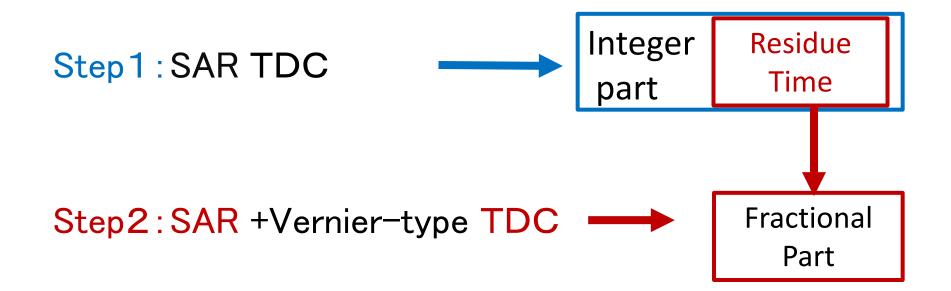

#### **Residue Time Usage**

SAR TDC Operation Result

Residue time <u>Tresidue</u> Sub-<u>TDC</u> with fine time resolution

Fine time resolution

#### with 2-Step SAR+Vernier-Type TDC

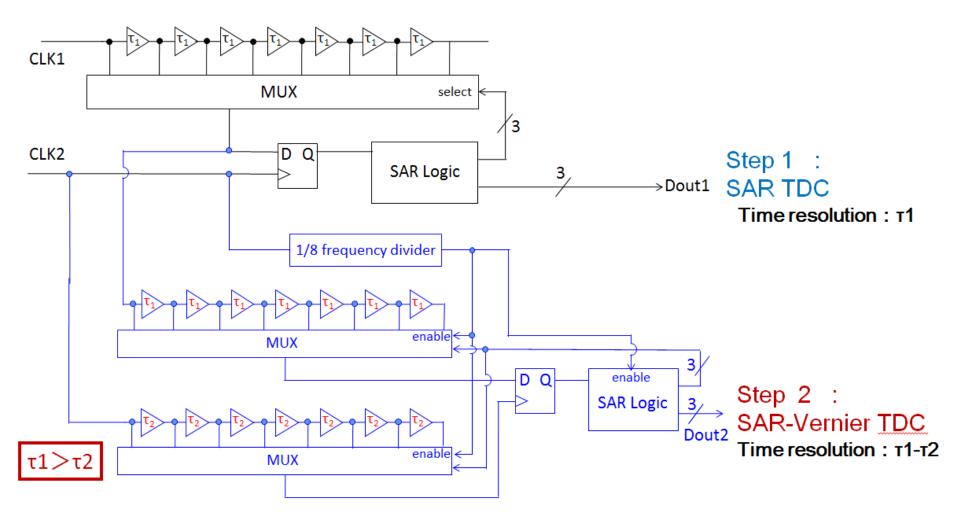

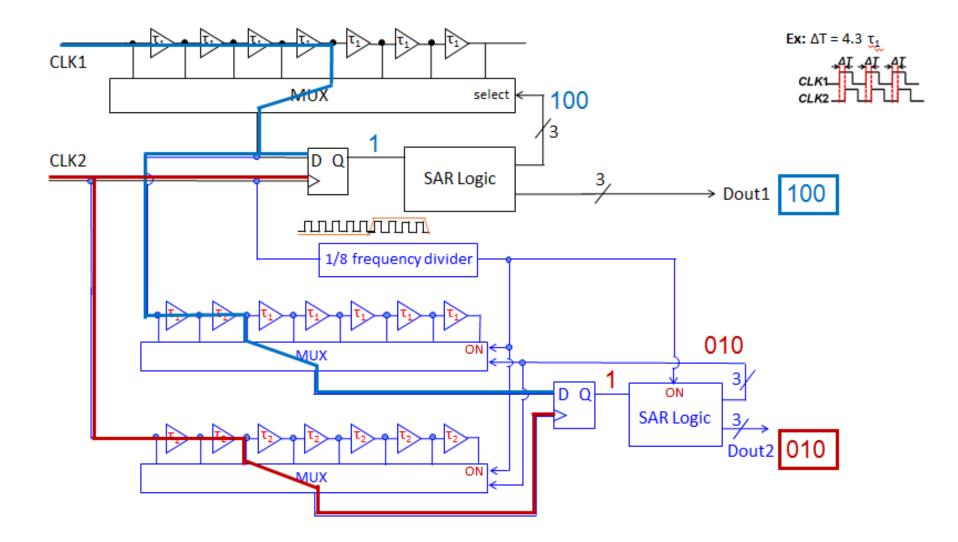

#### **3bit SAR + 3bit SAR-Vernier TDC Configuration**

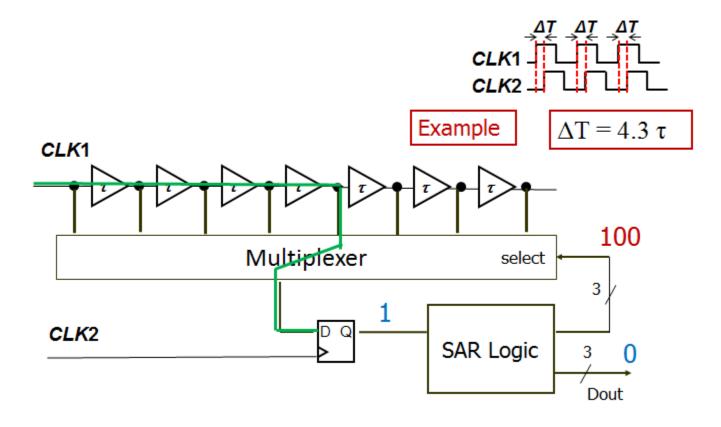

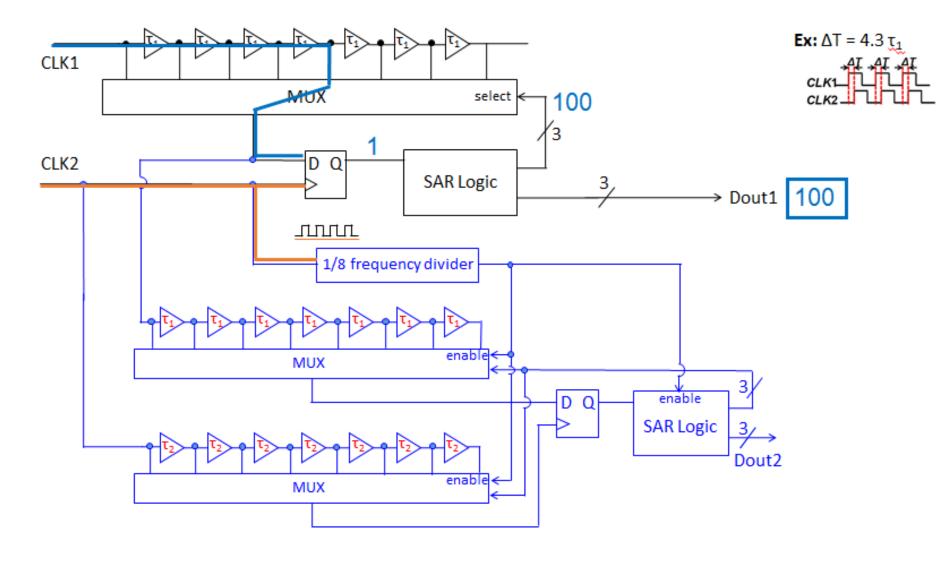

#### **3bit SAR + 3bit SAR-Vernier TDC Operation ①**

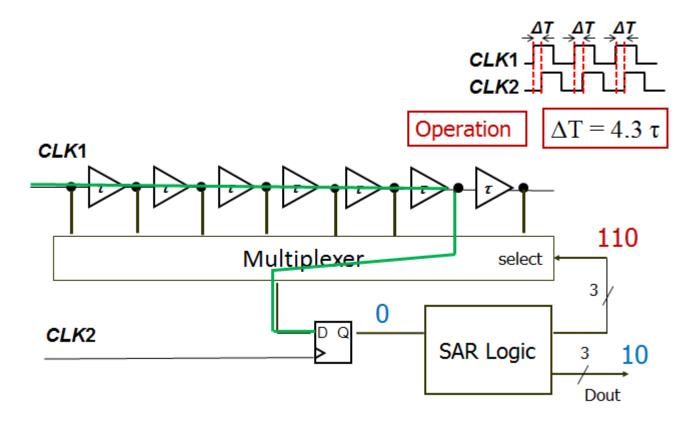

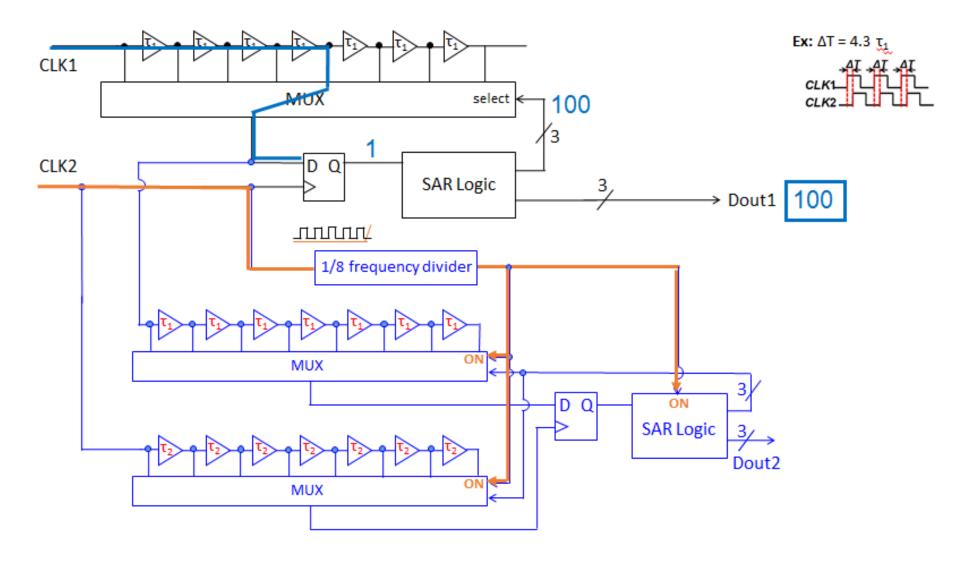

#### **3bit SAR + 3bit SAR-Vernier TDC Operation ②**

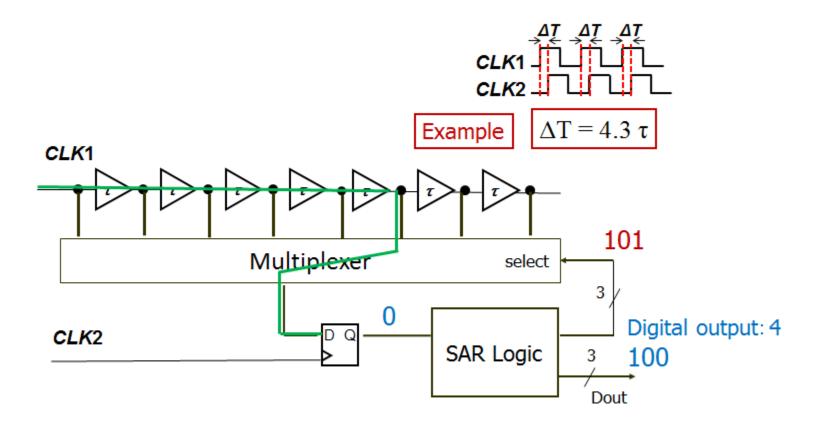

#### **3bit SAR + 3bit SAR-Vernier TDC Operation ③**

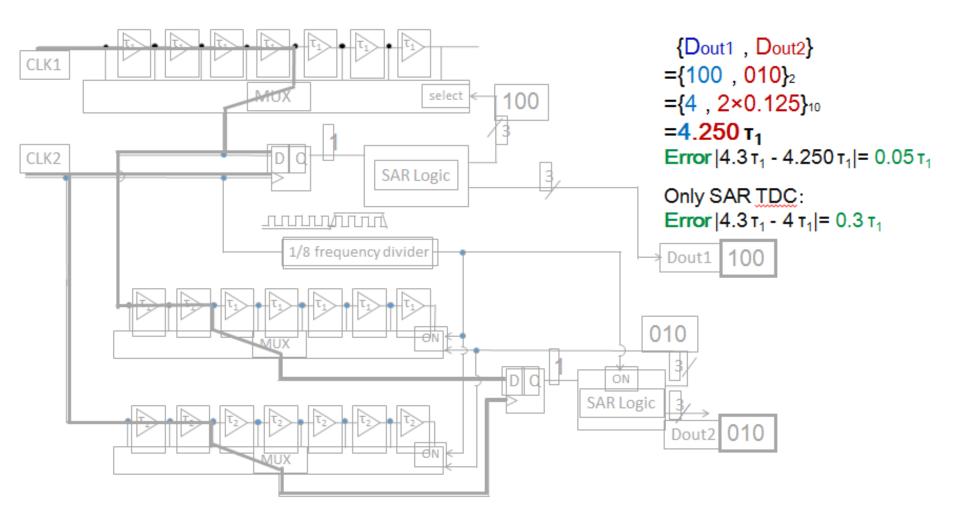

#### **3bit SAR + 3bit SAR-Vernier TDC Output**

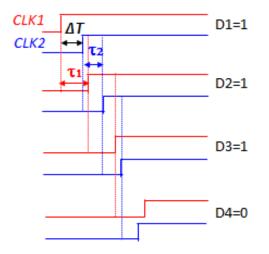

#### Flash TDC vs. Vernier TDC vs. SAR + SAR-Vernier

| 10bit design case             |          | 5bit+5bit |  |  |

|-------------------------------|----------|-----------|--|--|

| # of buffers: 1023            | 2046     | 93        |  |  |

| # of <u>DFFs</u> : 1023       | 1023     | 14        |  |  |

| Time resolution: <sup>1</sup> | τ1-τ2    | τ1-τ2     |  |  |

| Measurement time: One shot    | One shot | 10 times  |  |  |

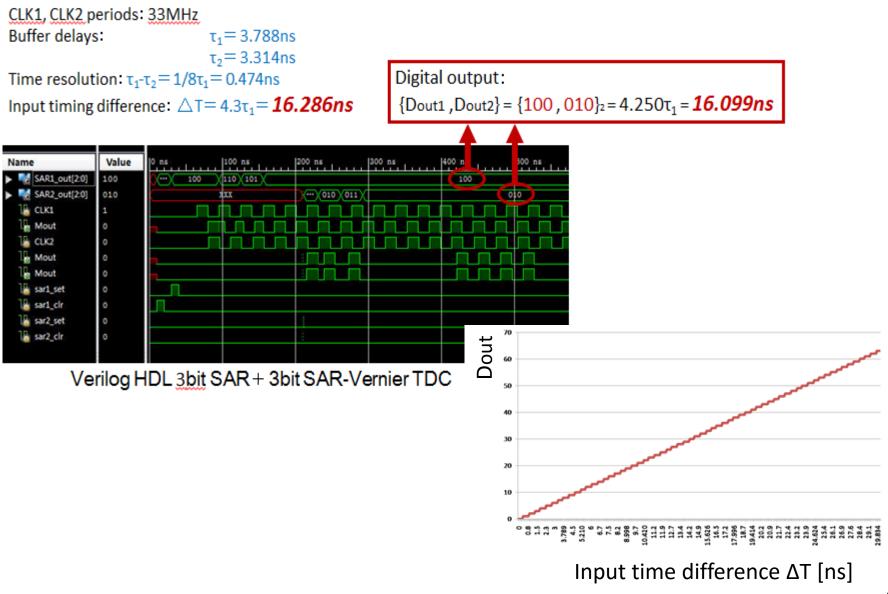

#### Xilinx ISE 14.1 RTL Simulation Verification

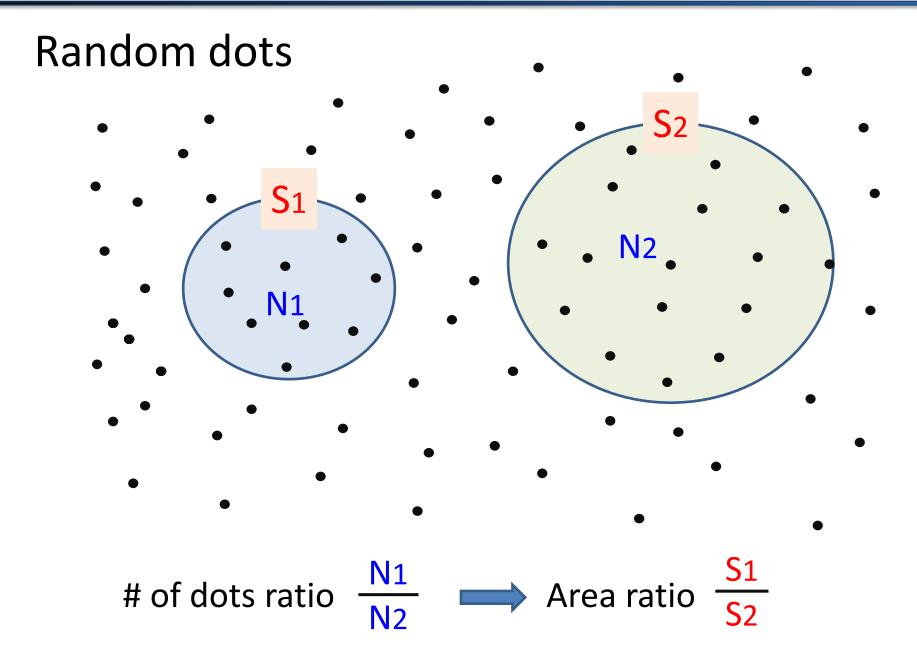

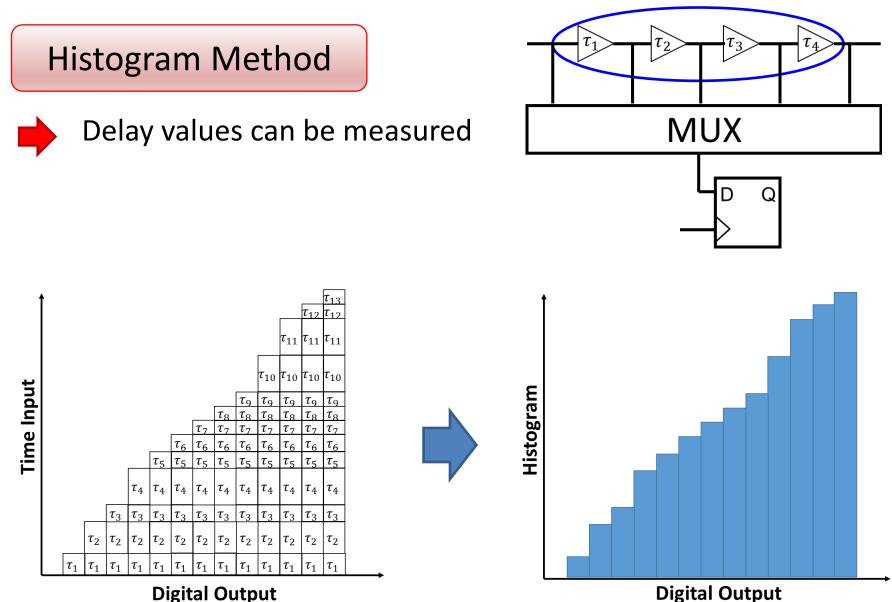

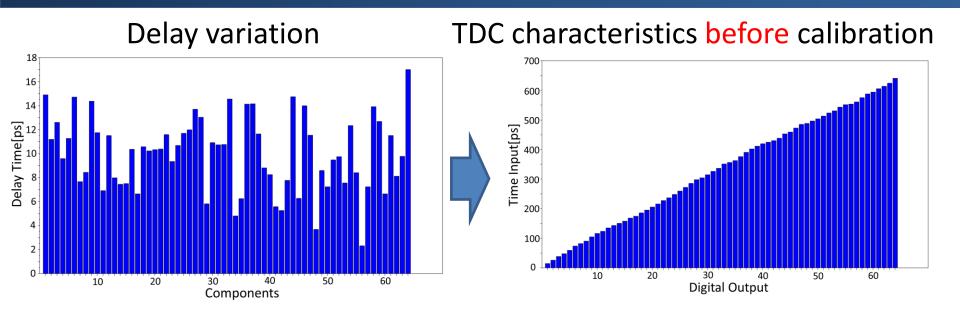

#### **Random Variation among Delay Cells**

Delay 7 variation

Relative variation

TDC nonlinearity

Absolute (average value) variation

TDC input range & time resolution

• Focus on relative variation here.

#### **Measurement with Histogram**

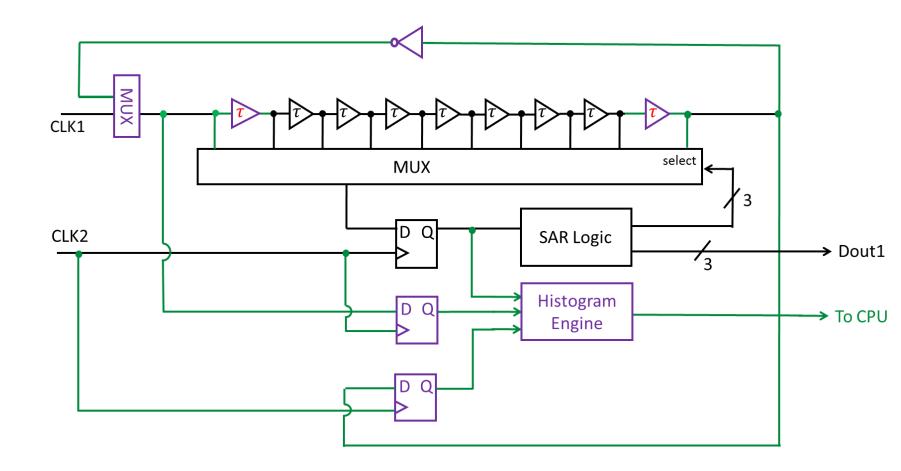

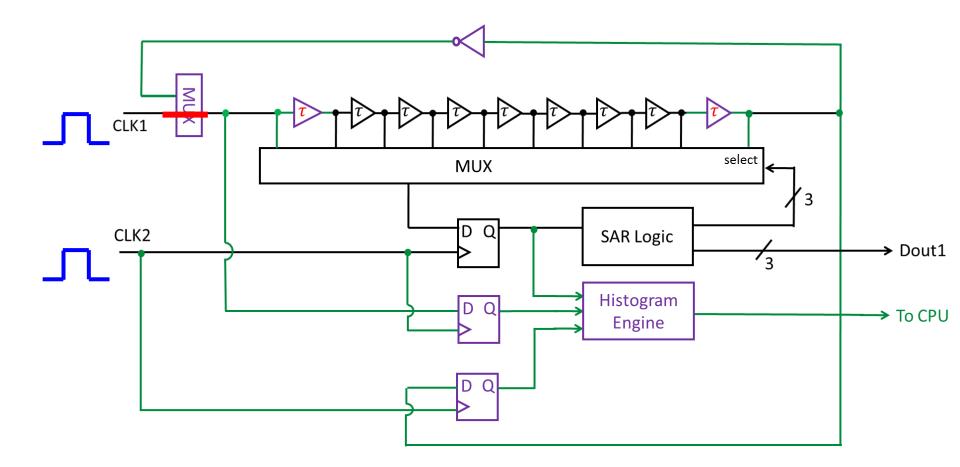

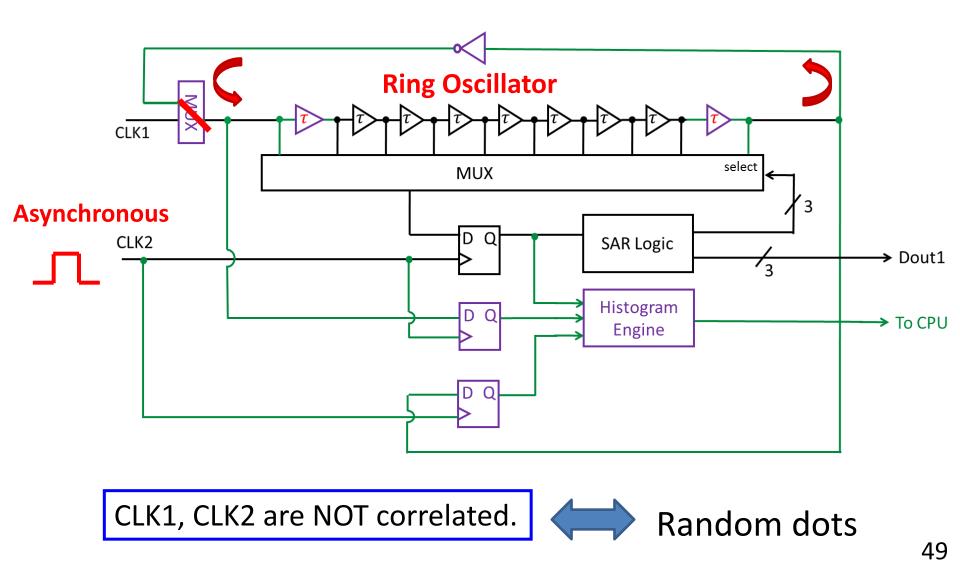

#### **SAR TDC with Self-Calibration**

Addition of calibration circuit, interconnection

47

#### **Normal Operation Mode**

48/36

#### **Calibration Mode**

#### **Calibration Mode (1)**

#### **Calibration Mode (2)**

#### **Calibration Mode (3)**

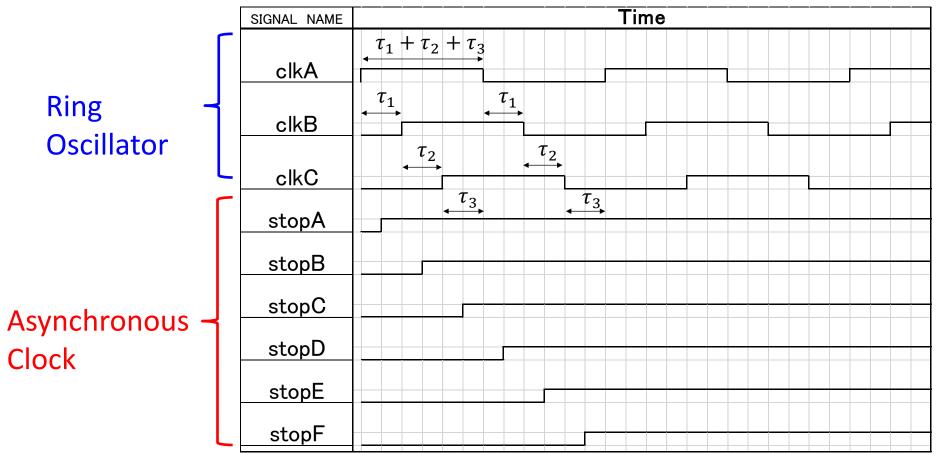

#### **Measurement of Delay Values**

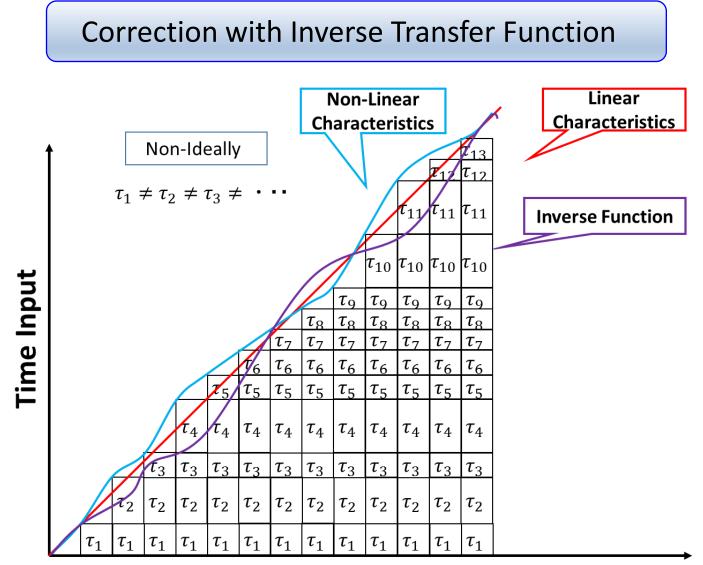

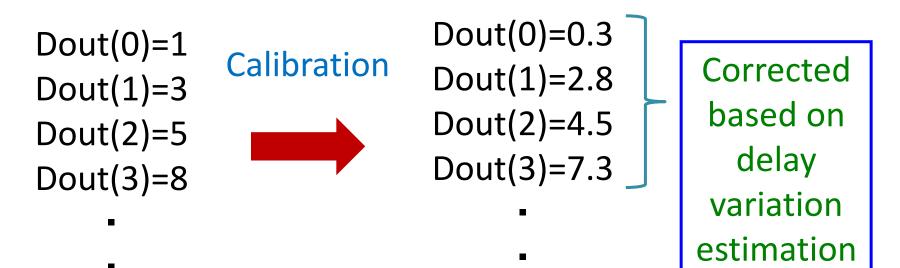

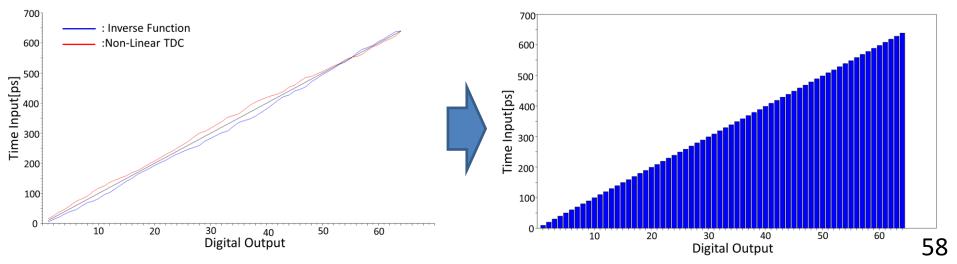

## **Digital Correction of TDC Nonlinearity**

#### **Digital Output**

#### **Measurement of Delays with Histogram**

55/36

**Timing Chart**

## **Digital Error Correction**

TDC linearity self-calibration with histogram

## **Simulation Verification**

#### TDC characteristics after calibration

## **Vernia Invention**

"Vernia" technology was invented by French mathematician, Pierre Vernier.

1580- 1637

#### "La construction, l'usage, et les proprietes du quadrant nouveau de mathematiques" (1631)

### Contents

#### Research Objective

TDC Application to LSI Testing Technology

## <u>4 Types of TDCs Developed at Gunma Univ.</u>

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ SAR-typeTDC

- ✓ <u>Delta-Sigma TDC</u>

- Discussions and Conclusion

#### 4 Types of TDCs

|                     | Clocks<br>Under<br>Test | Measurement<br>Time | Time<br>Resolution | Circuit | FPGA              |

|---------------------|-------------------------|---------------------|--------------------|---------|-------------------|

| Flash-type          | Single O<br>event       | Short 🔵             | Coarse 🔀           | Large 🔀 | Digital 🔵         |

| Gray code<br>based  | Single O<br>event       | Short 🔵             | Coarse 🔀           | Small 🔵 | Digital 🔵         |

| SAR-type            | Repetitive<br>clock     | Middle              | Middle             | Small   | Digital 🔵         |

| Delta-Sigma<br>type | Repetitive<br>clock     | Long 🔀              | Fine 🔵             | Small   | Small 🛆<br>Analog |

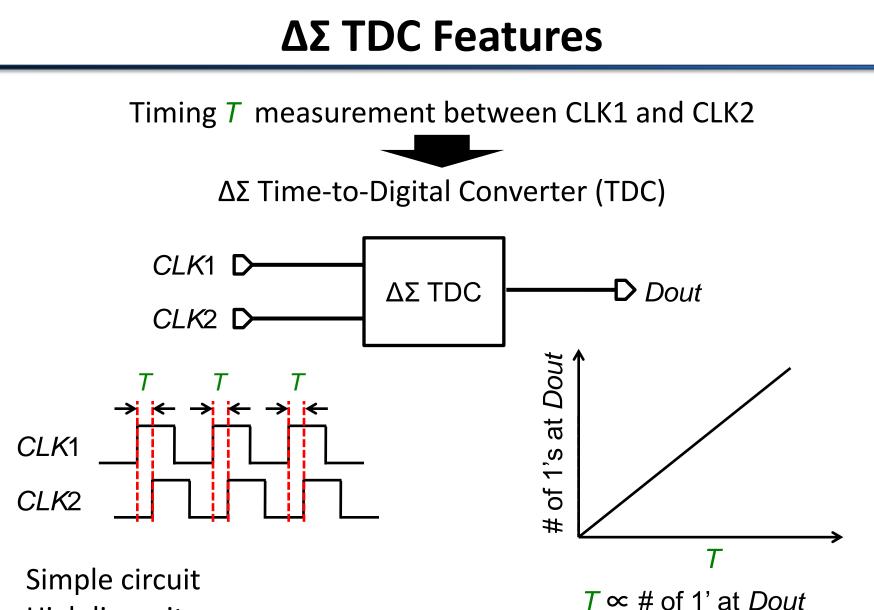

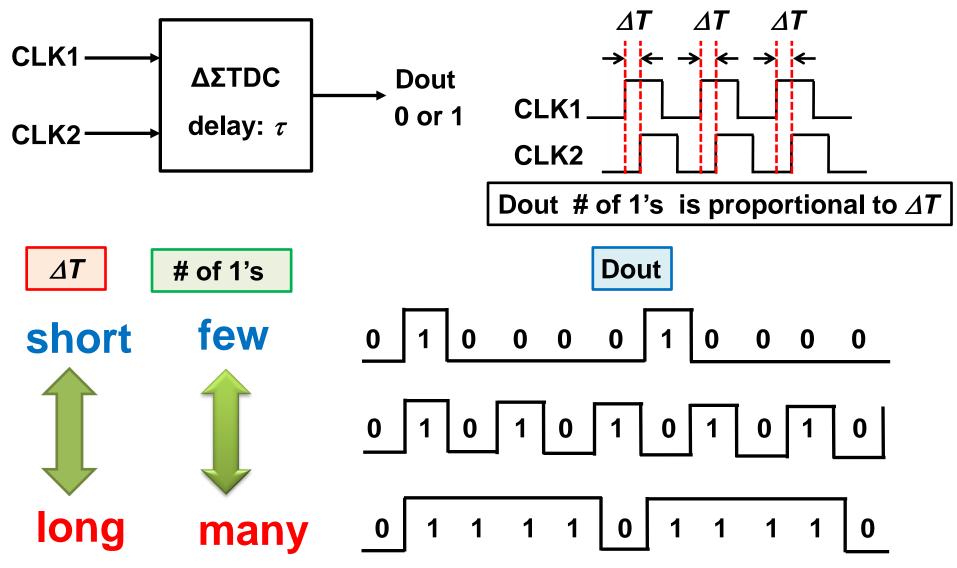

- **High linearity**

- Measurement time  $\rightarrow$  longer  $\Rightarrow$  time resolution  $\rightarrow$  finer ۲

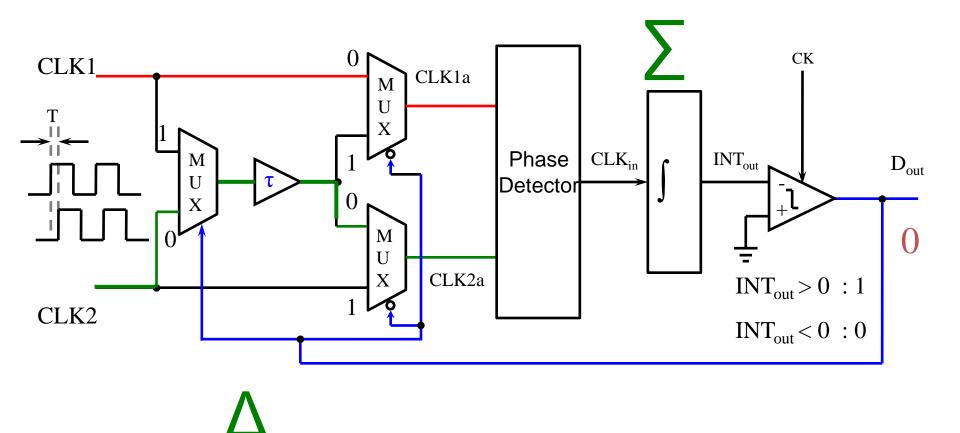

## Principle of $\Delta\Sigma TDC$

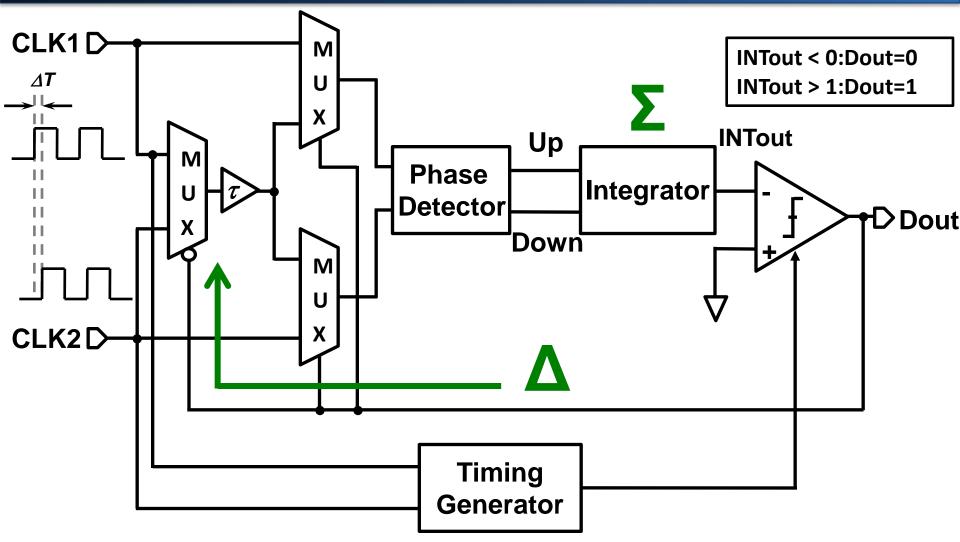

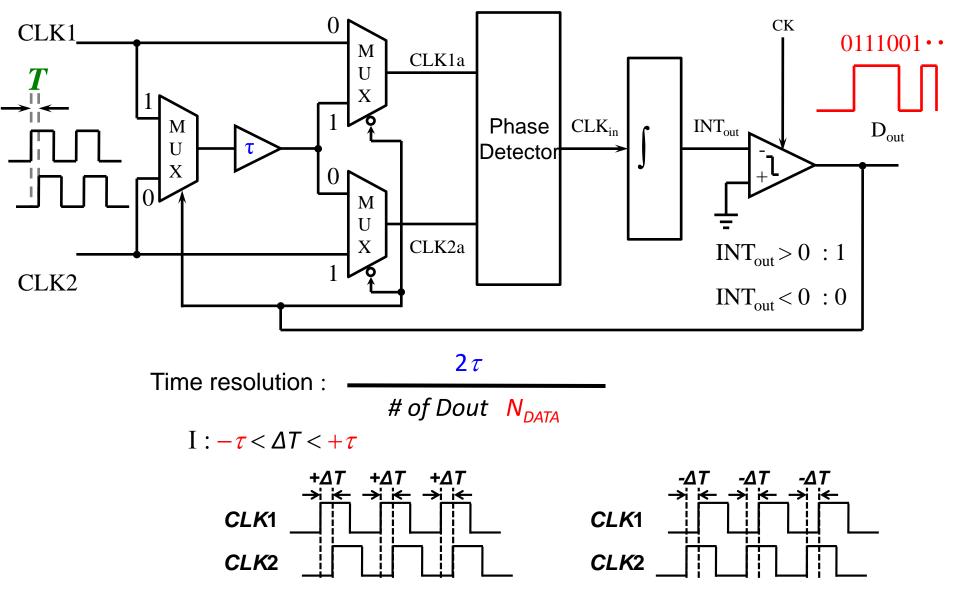

## **ΔΣΤDC Configuration**

## Single-Bit ΔΣ TDC

Delay line with 1bit digital input is inherently linear.

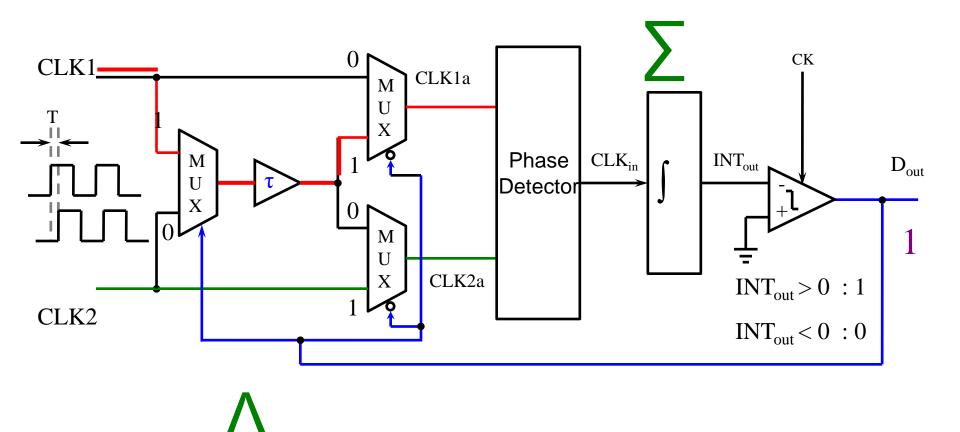

## **Operation of Single-Bit ΔΣ TDC**

In case Dout =1

## **Operation of Single-Bit ΔΣ TDC**

In case Dout =0

#### **ΔΣ TDC Implementation with Analog FPGA**

Analog FPGA PSoC (Programmable System on Chip) Cypress

[1] T. Chujo. H. Kobayashi, et. al.,

"Timing Measurement BOST With Multi-bit Delta-Sigma TDC", 20th IEEE International Mixed-Signal Testing Workshop, Paris, France (June 24-26, 2015).

# $\Delta\Sigma$ or $\Sigma\Delta$ ? That is a question

Delta-sigma modulator was invented by Prof. Yasuhiko Yasuda in 1960 at University of Tokyo, Japan.

ΛΣ

ΣΔ In many IEEE papers Use the term " $\Delta\Sigma$ " according to Prof. Yasuda.

Prof. Yasuda

## Contents

#### Research Objective

- TDC Application to LSI Testing Technology

- 4 Types of TDCs Developed at Gunma Univ.

- ✓ Flash-type TDC

- ✓ Gray code based TDC

- ✓ SAR-typeTDC

- ✓ Delta-Sigma TDC

#### Discussions and Conclusion

## **TDC Possibility for Timing BOST**

- TDC can be implemented with FPGA

- It can be realized with full digital circuit.

ADC cannot be.

- FPGA implementation of TDC can be disruptive innovation.

- IC designers & researchers tend to be interested in full custom IC design, instead of FPGA.

## Summary

- Two-step SAR TDC with self-calibration has been introduced.

- 4-types of TDCs are compared.

- They have their own advantages and disadvantages.

- TDC can be implemented with FPGA

It can be used for timing BOST.

Time continues indefinitely.

Kobayashi Laboratory

# Time is GOLD !!

TDC is a key.