### ΔΣDA変調器のデジタルディザ信号によるリミットサイクル低減技術の検討

新井 薫子, 小林 春夫 (群馬大学) 小島 潤也,

T161D034@gunma-u.ac.jp

困難

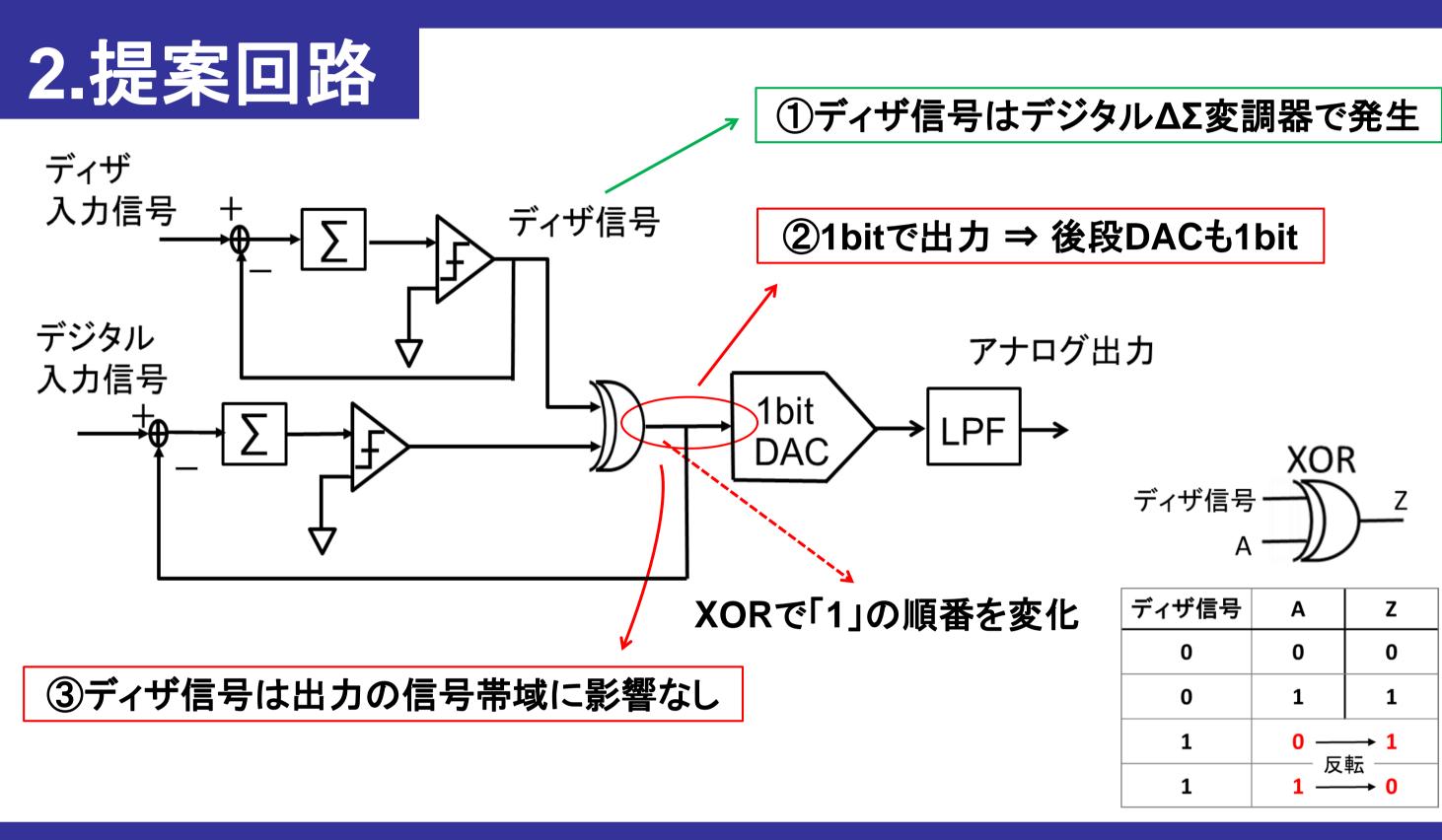

#### 1.研究目的 <ΔΣDA変換器の特徴> 量子化器 アナログ出力 デジタル入力 メリット 変調器 1bit 出力 アナログ ・大部分はデジタル回路 DAC **LPF** わずかなアナログ回路 リミットサイクル • 高分解能、高線形性 デメリット デジタルΔΣ変調器 ・微小信号では変調器出力に 入力信号成分にない周期信号成分が出力 信号成分 (リミットサイクル) Frequency Fs/2 ①ディザ信号はデジタルΔΣ変調器で発生 ディザ 入力信号

直流・低周波信号を高分解能、高線形に生成 ⇒電子計測器、LSI試験装置等に使用

アナログをLPFで急峻に落とす・・・

アナログ出力 = 信号成分 + リミットサイクル

目的・リミットサイクルを低減

・LPFの性能要求を緩和

### <dither(ディザ)の起源>

■ 第二次世界大戦の頃 爆撃機には計算機が使用 ディザ信号

地上より飛行機上の方がうまく動作

理由:振動の刺激が誤差を減少 didderen (震える) → dither(ディザ)

※人間でも・・・

「完全に静かな場所では集中できない」

Philip E. Vernon 心理学者(英)

5.4dB < 22.9dB

リミットサイクル低減

Fs/2

**Frequency**

中心値

-100

-120

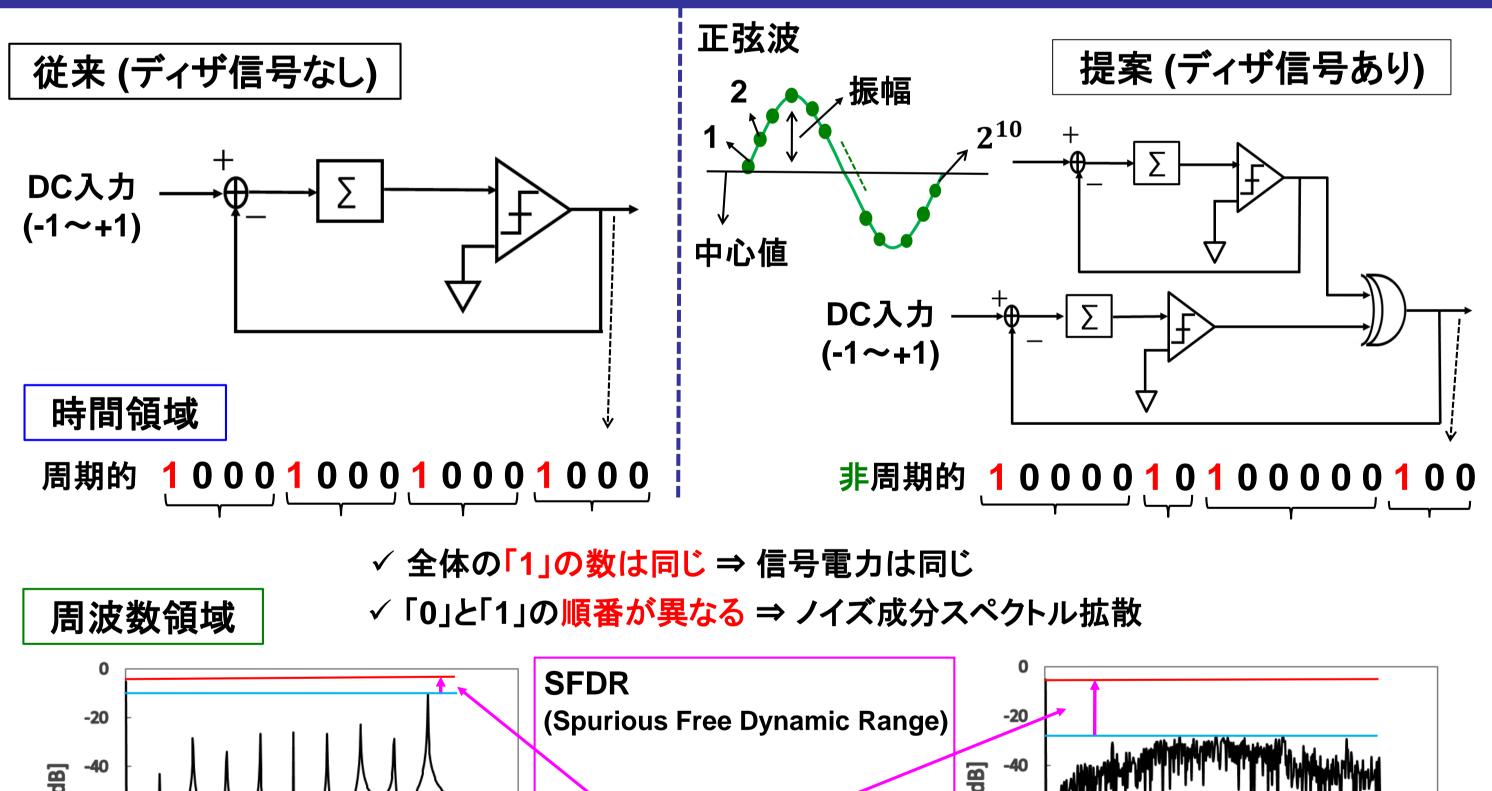

# 3.シミュレーション結果 (データ数:10bit)

勉強中

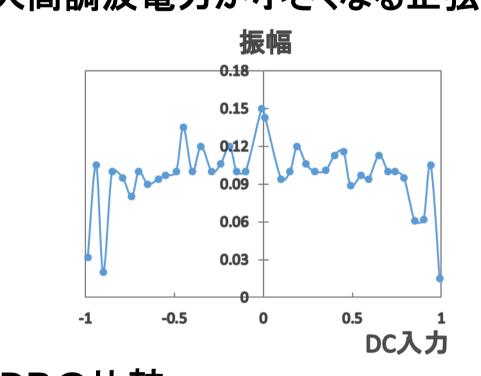

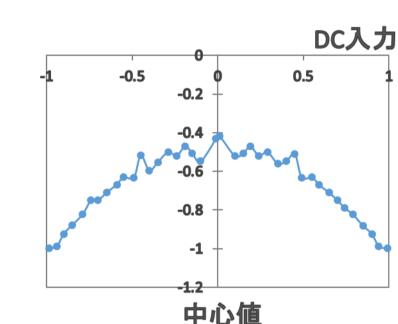

◆最大高調波電力が小さくなる正弦波の振幅・中心値

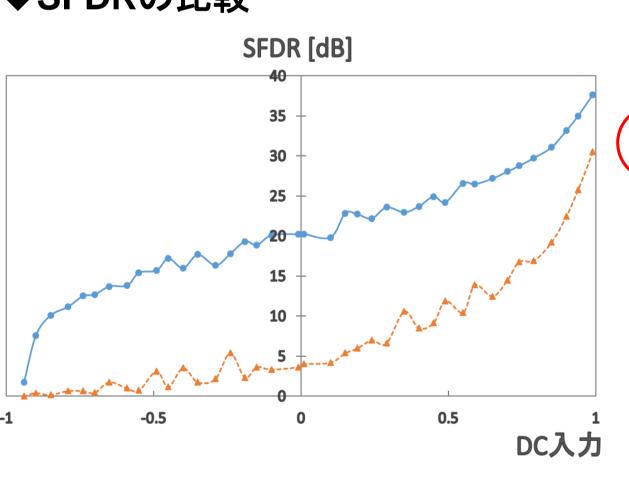

◆SFDRの比較

SFDRが10dB以上改善!!

ディザ信号あり ——

ディザ信号なし - 一-

#### 4.FPGA実装 SFDR [dB] 振幅 0.256 **SFDR** 三角波 Reg 10dB以上改善!! 中心値を変化 ディザ信号あり —— ディザ信号なし - ----DC入力 DC Reg DC入力 $(-0.8 \sim +0.8)$ 変調器出力の「1」の数の差 近似 「1」の数の差は DC入力 ±2の範囲内 -0.8 -0.6 -0.4 -0.2 0 0.2 0.4 0.6 0.8 DC入力 -0.7

Xilinx (Virtex-6 ML605)

-100

-120

Fs/2

**Frequency**

#### 5.まとめ 〈従来〉

ΔΣ変調器は直流・低周波信号でリミットサイクル発生

〈提案〉

デジタルディザ信号と排他的論理和を用いた構成

- リミットサイクル低減

- SFDR向上、線形性保持

- FPGAでの動作を確認

# 参考文献

[1] R.Schreier, G.C Temes, Understanding Delta-Sigma Data Converters, Wiley-IEEE press (2009).

[2]小島潤也, 新井薫子, 小林春夫, "ΔΣ変調器のデジタルディザ 信号による性能改善と回路設計の検討",第6電気学会東京支部 栃木·群馬支所合同研究発表会, 前橋, ETT-16-9, ETG-16-9 (2016年3月)