IEEE International Symposium on Intelligent Signal Processing and Communication Systems 2017

NOVEMBER 6-9, 2017, XIAMEN, CHINA

Nov. 8 WP-L2 14:30-15:50

#### SAR TDC Architecture for One-Shot Timing Measurement with Full Digital Implementation

#### Y. Ozawa, T. Ida, R. Jiang, S. Sakurai, <u>R.Takahashi,</u> R. Shiota, H. Kobayashi Gunma University, <u>Socionext Inc.</u>,

Kobayashi Lab. Gunma University

#### Objective

#### Development of highly-linear, fine time-resolution TDC for high-speed digital I/O interface timing measurement

#### Innovation

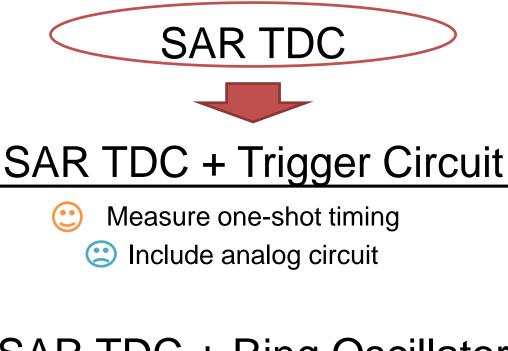

#### Trigger Circuit **One-shot** timing measurement & Good for low frequency repetitive timing Ring Oscillator **One-shot** timing measurement Å Good for high & low frequency repetitive timing

#### Approach

#### SAR TDC + Ring Oscillator

Measure one-shot timing

Without analog circuit

#### Full digital FPGA implementation

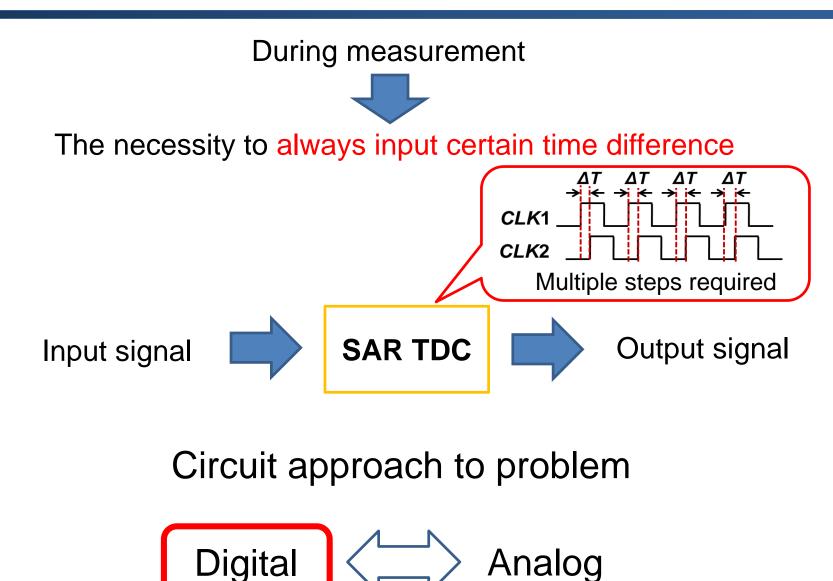

#### Problems in Operation of SAR

## Outline

- Research Objective

- Conventional TDC Architecture

- Flash TDC

- SAR TDC Architecture & Operation

- Proposed SAR TDC Analog Centric

- Proposed SAR TDC Digital Centric

- Architecture & Operation

- High Frequency

- Low Frequency

- Simulation

Conclusion

## Outline

#### Research Objective

- Conventional TDC Architecture

- Flash TDC

- SAR TDC Architecture & Operation

- Proposed SAR TDC Analog Centric

- Proposed SAR TDC Digital Centric

- Architecture & Operation

- High Frequency

- Low Frequency

- Simulation

Conclusion

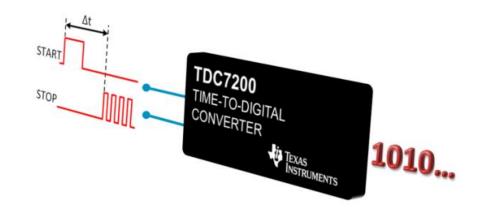

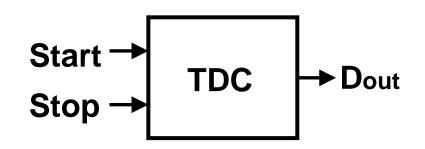

## Time to Digital Converter (TDC)

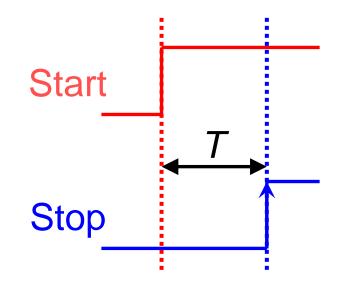

• Time interval  $\rightarrow$  Measurement  $\rightarrow$  Digital value

- Key component of Timedomain analog circuit

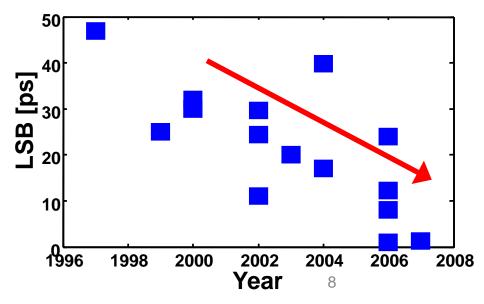

- Higher resolution can be obtained with scaled CMOS

#### **Higher resolution with CMOS scaling**

#### Background

A Time-to-Digital Converter (TDC) provides a digital output proportional to time between two clock transitions.

The TDC is a key component in time-domain analog circuits,

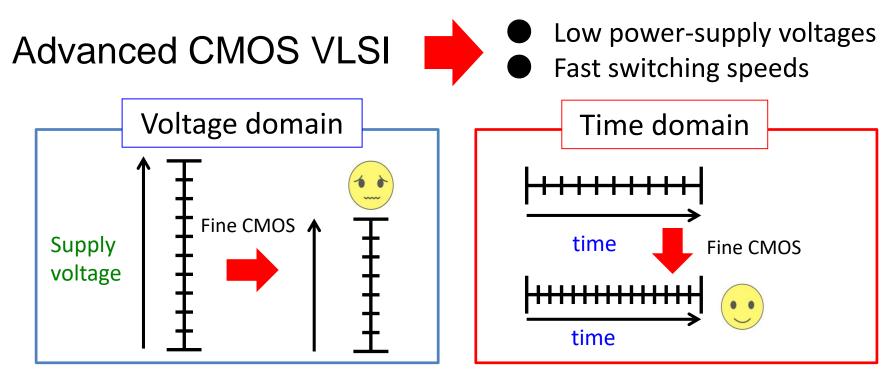

#### **Time Domain Analog Circuit Features**

#### • Voltage domain:

Signal range : Up to power supply voltage Time domain:

Signal range : Time continues indefinitely

Large dynamic range

# Time domain analog circuit: Binary amplitude (Vss, Vdd) Can consist of digital circuit

## Outline

#### Research Objective

## Conventional TDC Architecture Flash TDC

- SAR TDC Architecture & Operation

- Proposed SAR TDC Analog Centric

- Proposed SAR TDC Digital Centric

- Architecture & Operation

- High Frequency

- Low Frequency

- Simulation

Conclusion

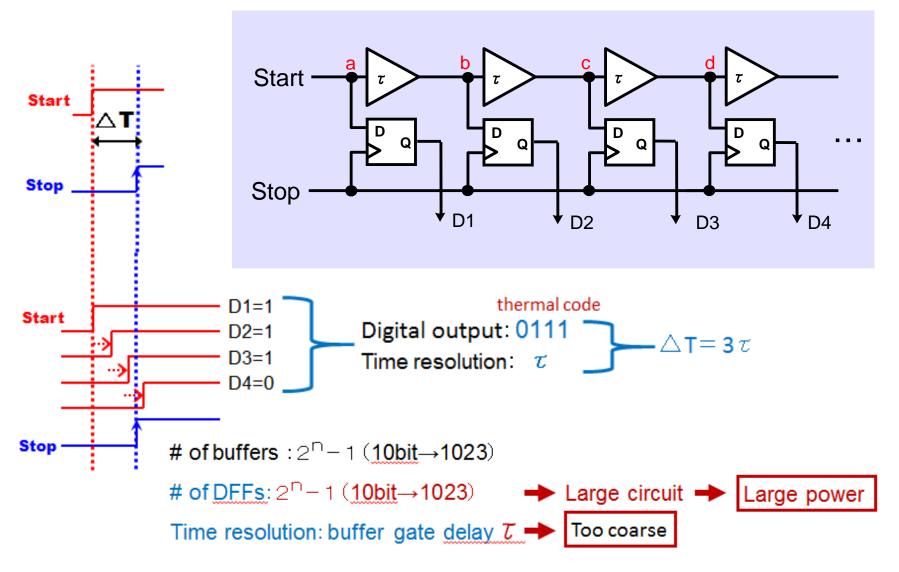

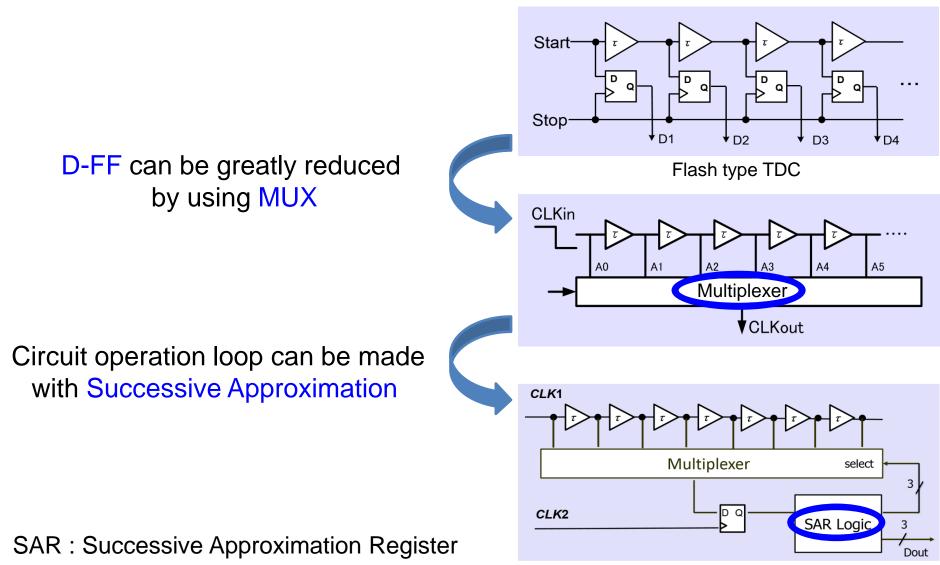

## Flash-type TDC

## Outline

- Research Objective

- Conventional TDC Architecture

Flash TDC

- SAR TDC Architecture & Operation

- Proposed SAR TDC Analog Centric

- Proposed SAR TDC Digital Centric

- Architecture & Operation

- High Frequency

- Low Frequency

- Simulation

Conclusion

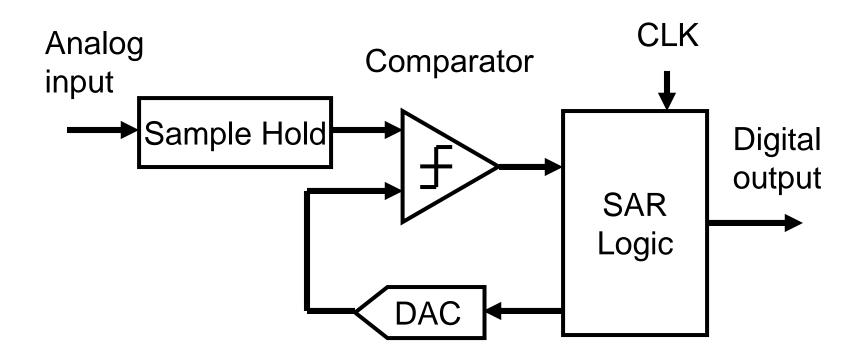

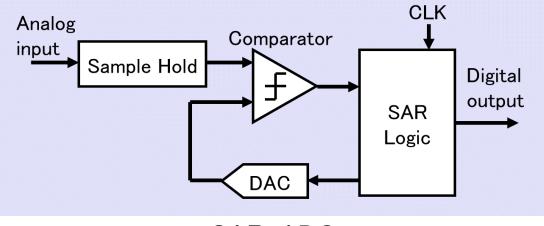

#### SAR ADC Block

SAR ADC is digital centric.

$\rightarrow$  Suitable for fine CMOS implementation.

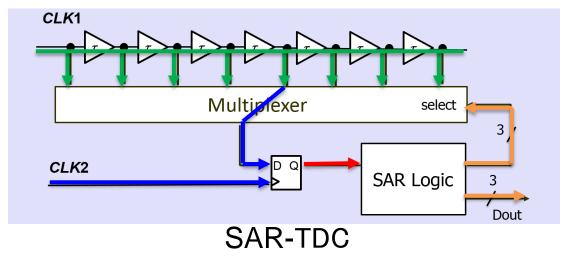

#### SAR TDC Architecture

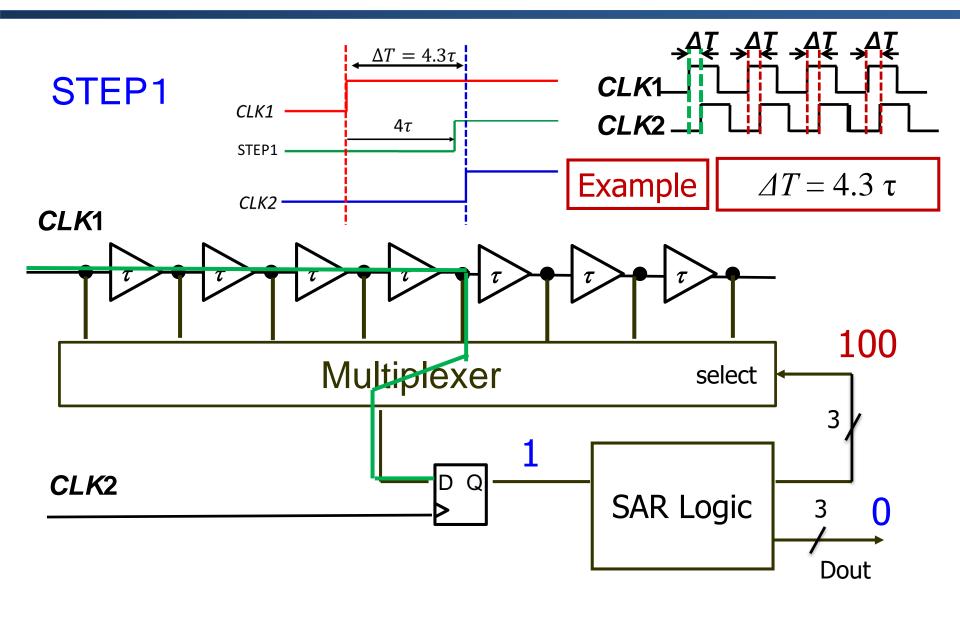

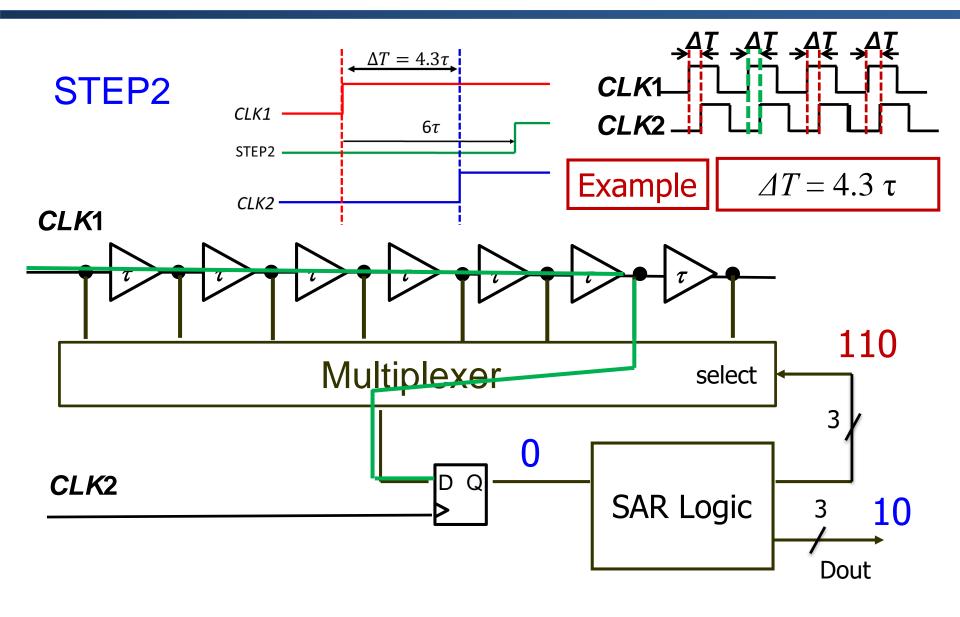

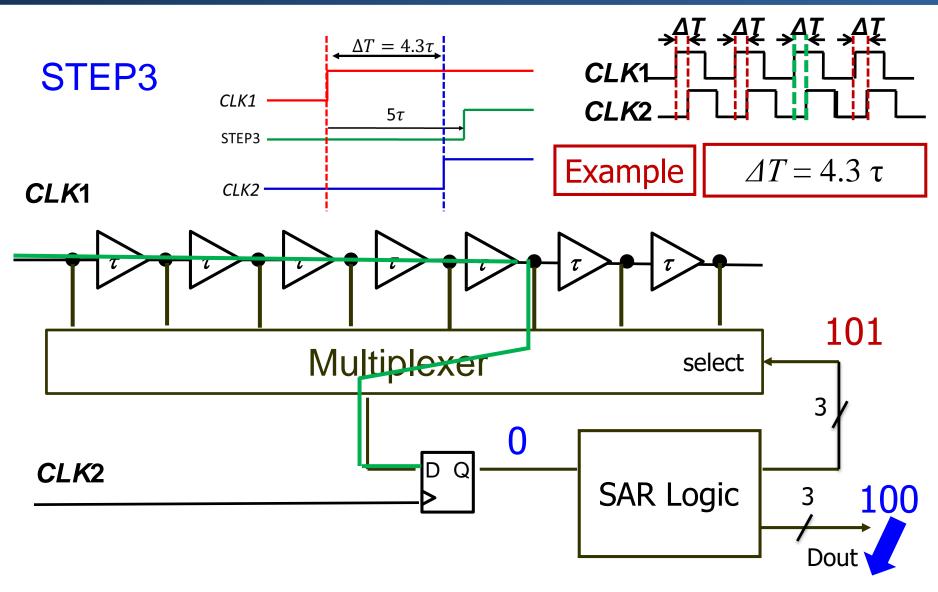

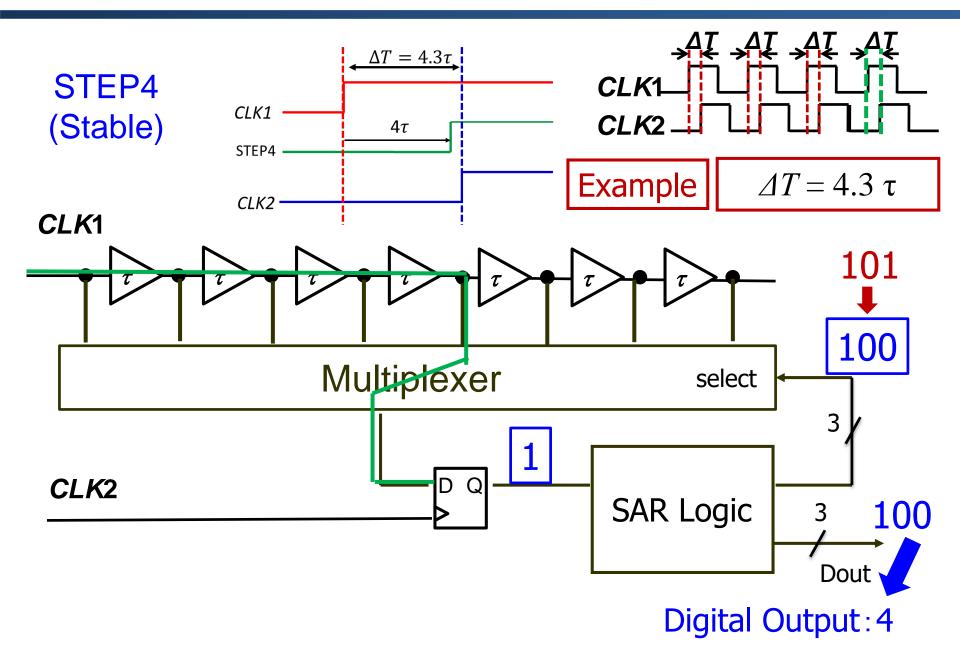

SAR TDC

#### SAR-ADC VS SAR-TDC

SAR ADC :ComparatorDAC

SAR-ADC

SAR TDC :D-FFDelay Line

Digital Output:4

## Outline

- Research Objective

- Conventional TDC Architecture

- Flash TDC

- SAR TDC Architecture & Operation

- Proposed SAR TDC Analog Centric

- Proposed SAR TDC Digital Centric

- Architecture & Operation

- High Frequency

- Low Frequency

- Simulation

Conclusion

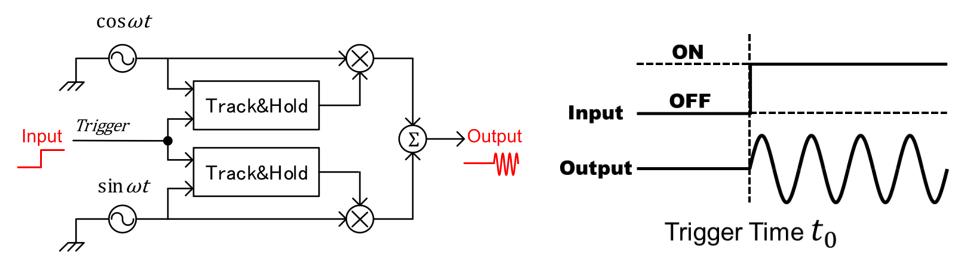

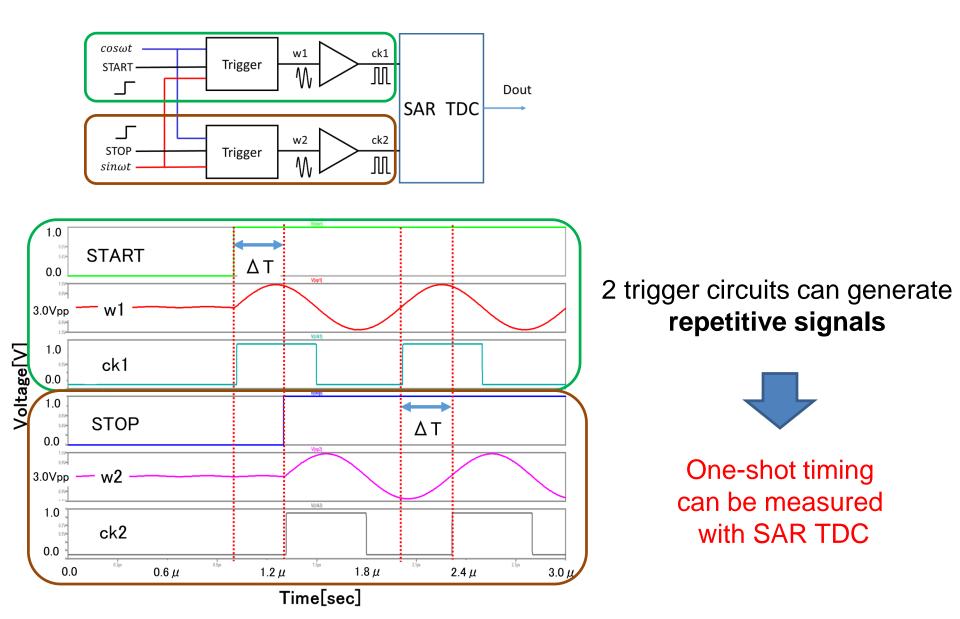

## **Trigger Circuit**

#### □Output starts to oscillate at rising timing edge of input

#### **D**Output waveform with no transient change

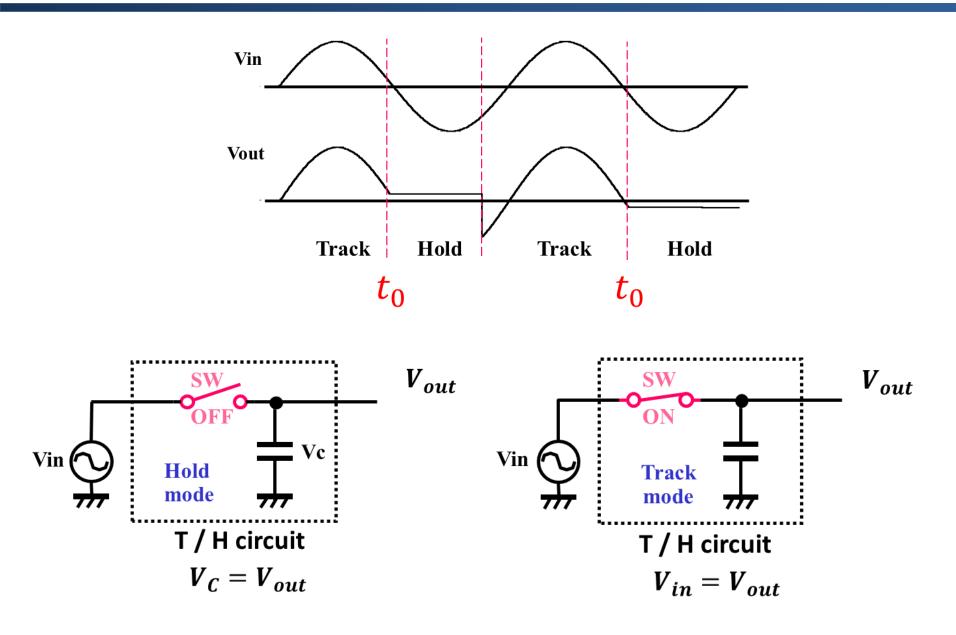

#### T/H Circuit

#### **Trigger Circuit Waves**

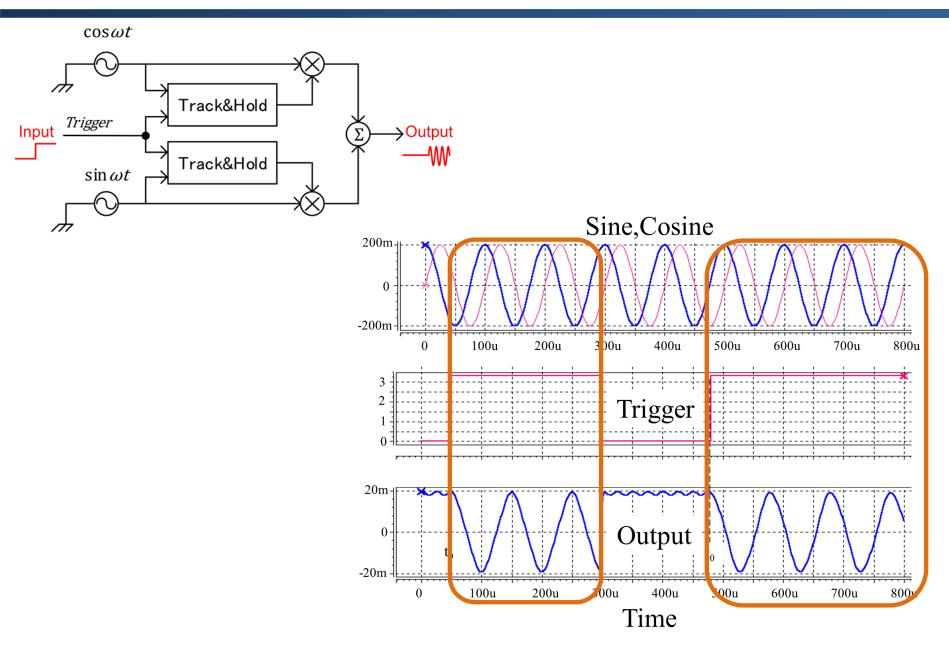

## Combination of Trigger Circuit & SAR TDC<sup>25/40</sup>

#### **Proposed Circuit**

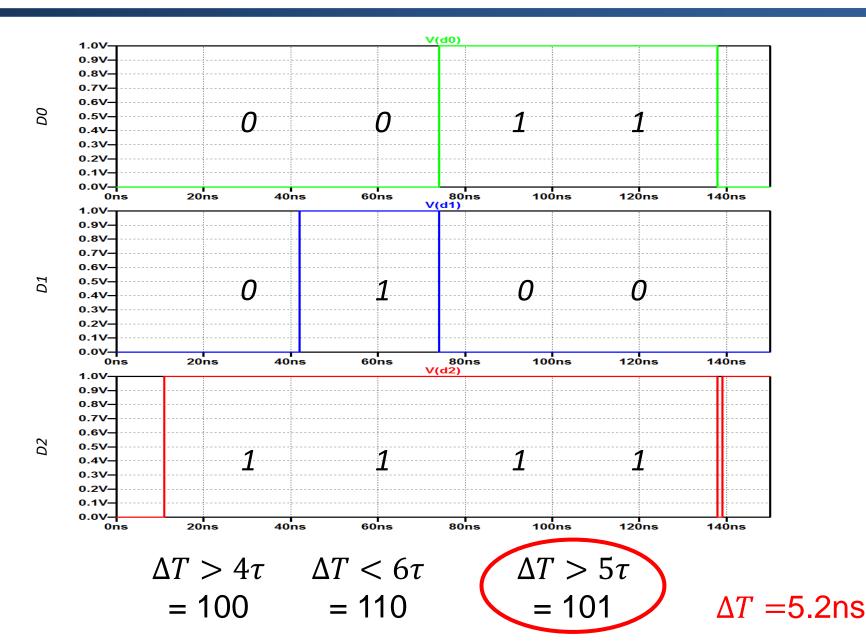

#### **Simulation Results**

## Outline

- Research Objective

- Conventional TDC Architecture

- Flash TDC

- SAR TDC Architecture & Operation

- Proposed SAR TDC Analog Centric

- Proposed SAR TDC Digital Centric

- Architecture & Operation

- High Frequency

- Low Frequency

- Simulation

Conclusion

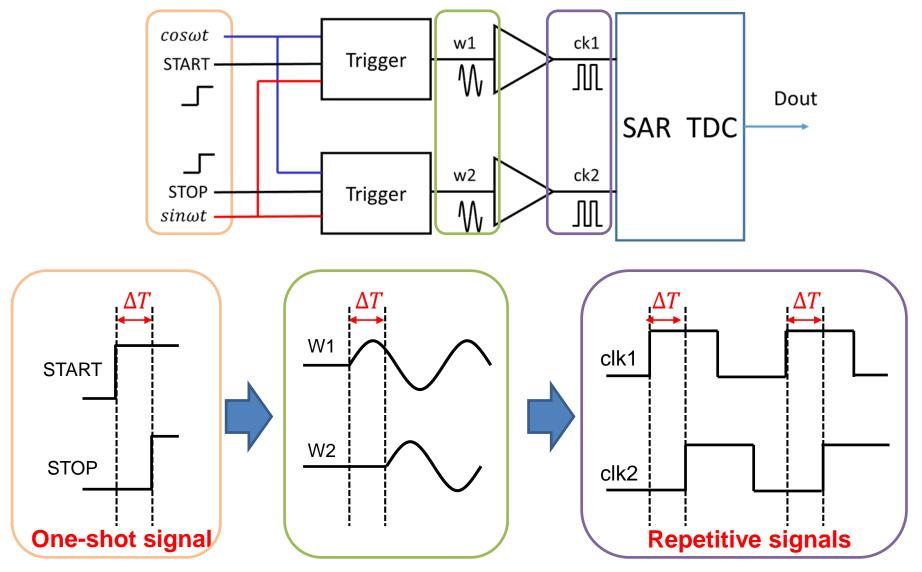

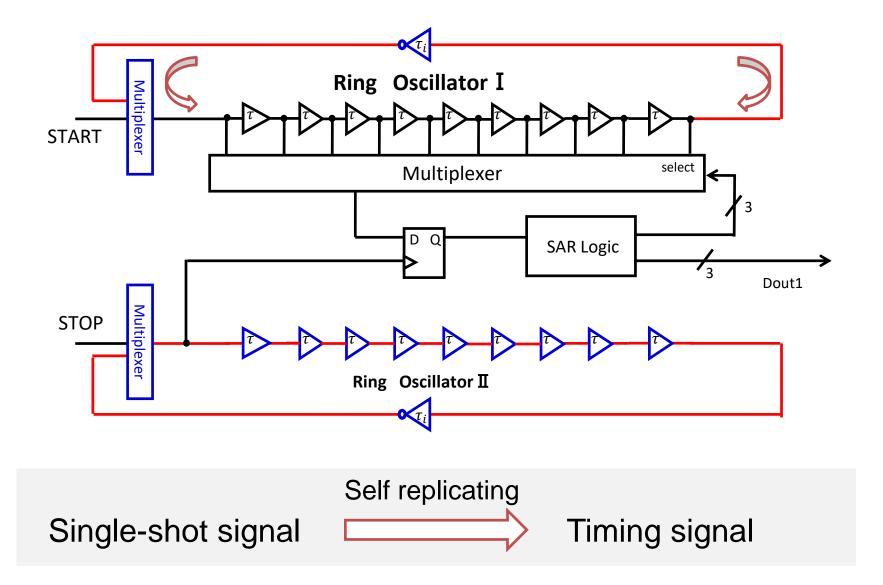

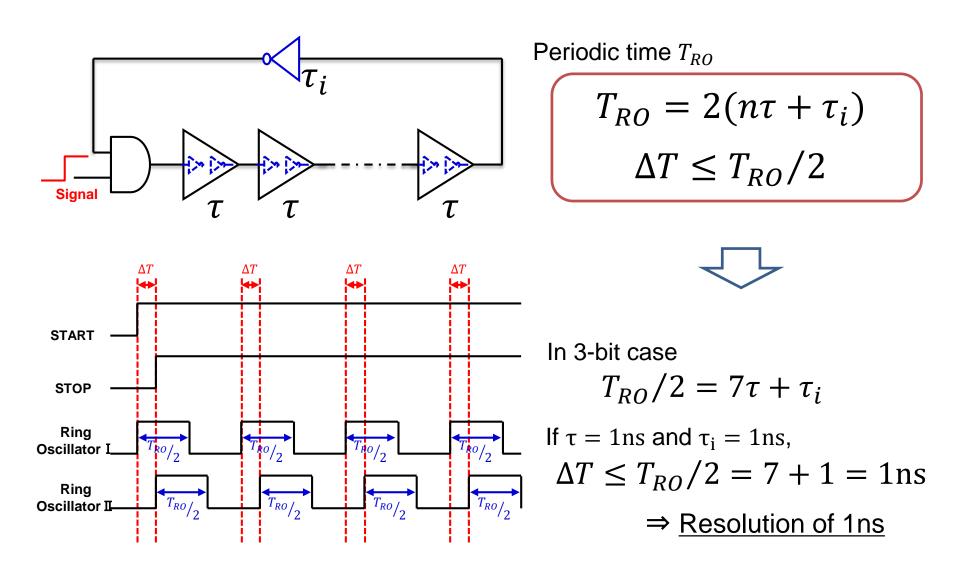

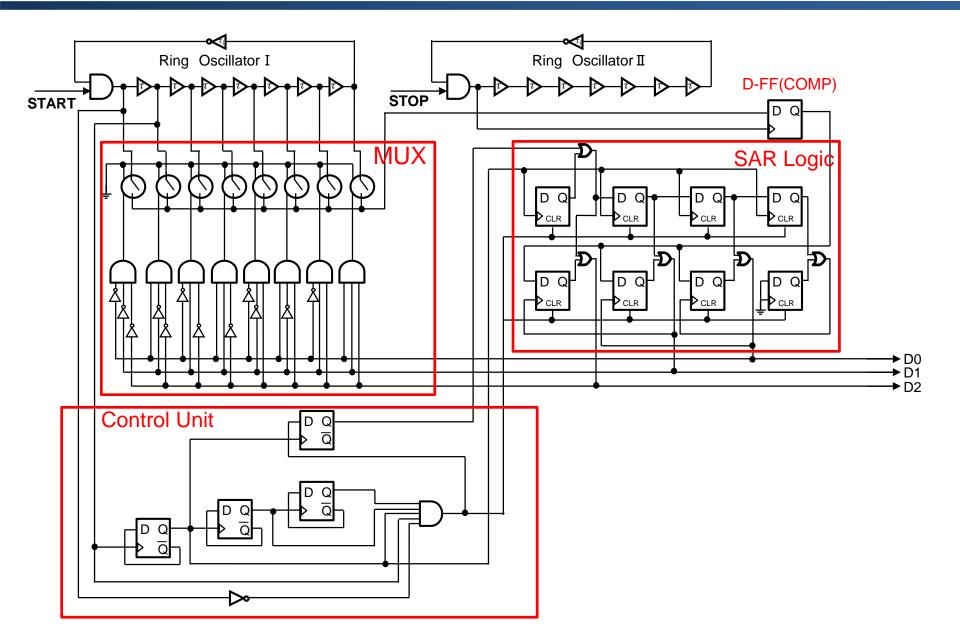

#### **Ring Oscillator**

#### **Ring Oscillator**

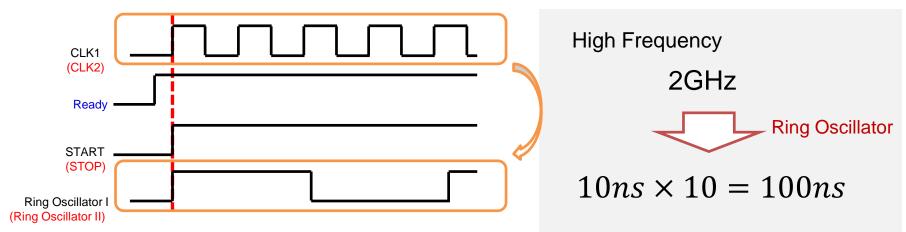

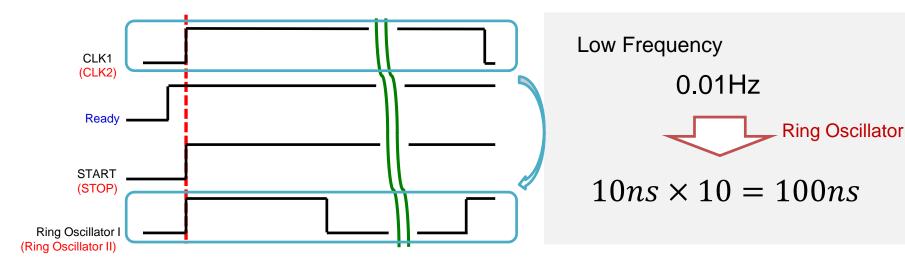

## Frequency Repetitive Clock Measurement<sup>30/40</sup>

#### High Frequency

Low Frequency

#### **Simulated Circuit**

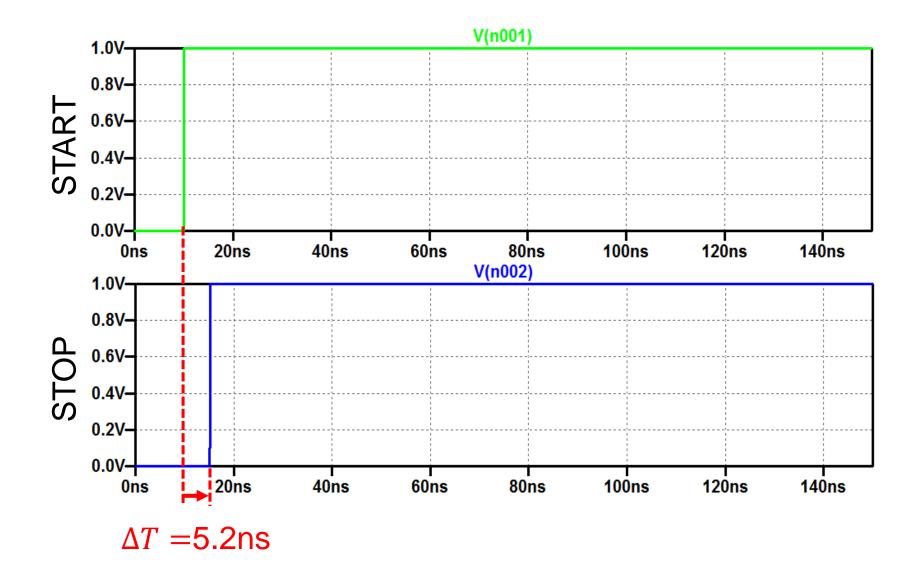

#### **One-Shot Input Signal**

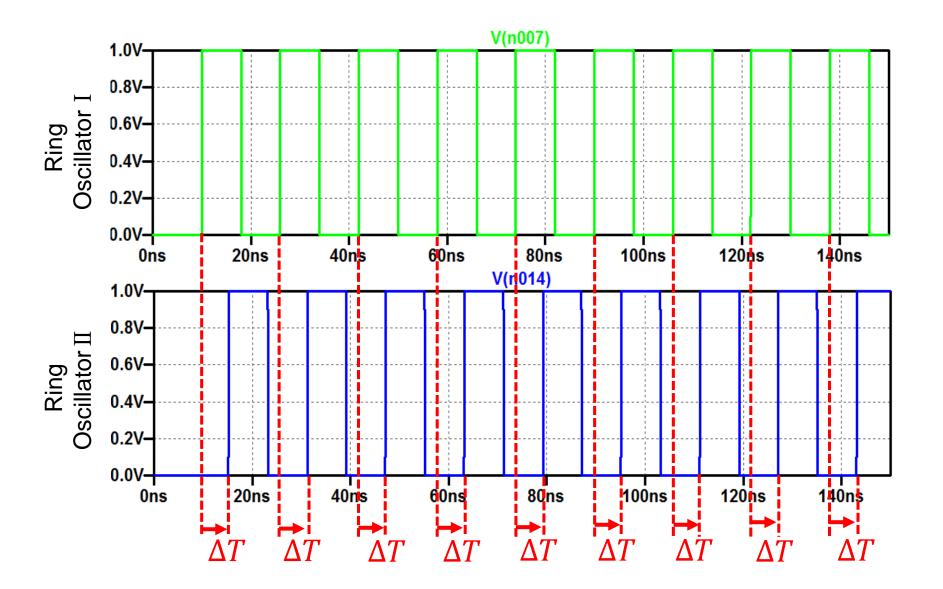

#### Simulated Ring Oscillator Waveforms

#### **D-FF Output Signal at Each Step**

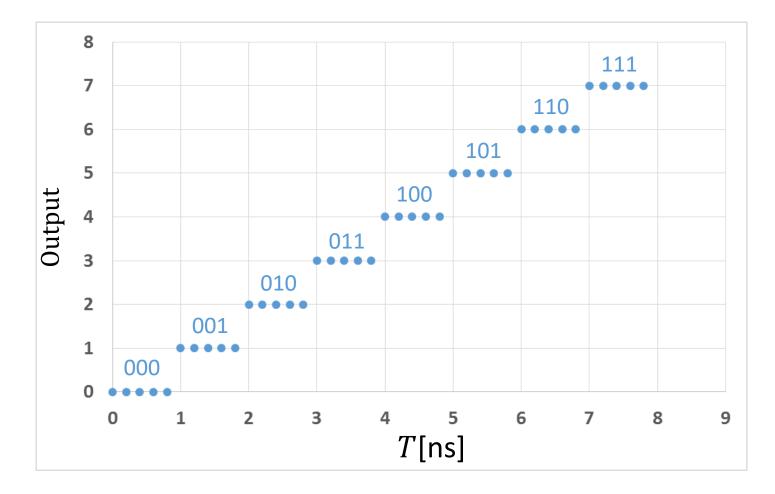

#### **Input Output Linearity**

Proposed SAR TDC input & output have linear relationship

## Outline

- Research Objective

- Conventional TDC Architecture

- Flash TDC

- SAR TDC Architecture & Operation

- Proposed SAR TDC Analog Centric

- Proposed SAR TDC Digital Centric

- Architecture & Operation

- High Frequency

- Low Frequency

- Simulation

Conclusion

#### Discussion (1)

SAR TDC operates with external clock

Operation speed depends on measured clock witch may be variable

**Employing ring oscillators**

#### Frequency is fixed

Reasonable as mixed-signal circuit design

#### Discussion (2)

#### <u>Assumption</u>

# Two ring oscillators are completely matched (oscillation frequencies are the same)

In reality they are not

#### Future work

Mismatch compensation or self-calibration method (e.g. redundancy SAR algorithm)

#### Conclusion

✓ Trigger circuit can generate repetitive signals

- ✓ Ring oscillator helps the realization of full digital FPGA

- ✓ One shot timing can be measured with SAR TDC

- The remaining work

Taking care of mismatches between two ring oscillators

40/40

TDC is a key.