## 低スイッチング損失かつ低特性オン抵抗の スケーラブル 20-40V LDMOSトランジスタ

小島潤也 松田順一 築地伸和 神山雅貴 小林春夫 群馬大学

- 研究背景•目的

- 従来型・提案型LDMOSトランジスタ構造

- シミュレーション結果

- I<sub>DS</sub>-V<sub>GS</sub>特性

- I<sub>DS</sub>-V<sub>DS</sub>特性

- ブレークダウン特性

- 特性オン抵抗-ブレークダウン電圧特性

- ホットキャリア耐性

- まとめ

- 研究背景•目的

- ・ 従来型・提案型LDMOSトランジスタ構造

- シミュレーション結果

- I<sub>DS</sub>-V<sub>GS</sub>特性

- I<sub>DS</sub>-V<sub>DS</sub>特性

- ブレークダウン特性

- 特性オン抵抗-ブレークダウン電圧特性

- ホットキャリア耐性

- まとめ

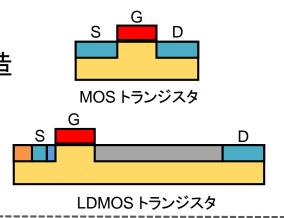

## 研究背景•目的

#### LDMOS (Laterally Double Diffused MOS) トランジスタ

- •特長

- ゲート-ドレイン間の電界強度を緩和する構造 耐圧が高い⇒高電圧を印加可能

- パワーMOSトランジスタの一種電源回路のスイッチングなどに使用

#### <u>車載用 20-40V 動作 のLDMOSトランジスタ</u>に注目

- 広SOA (Safe Operation Area)、高信頼性

Point

- 低特性オン抵抗

- 低スイッチング損失

- 20-40Vの複数電圧で動作可能

- └→ 製造プロセスコストが上がらず、1チップ上に作製可能

左記条件を満たす LDMOS構造を提案

## Si, SiC, GaN との特徴比較

■ 次世代パワー半導体は SiC (シリコン・カーバイド)

GaN (ガリウム・ナイトライド) が注目されているが...

|                                        | SiC, GaN | Si (シリコン)               |  |  |

|----------------------------------------|----------|-------------------------|--|--|

| 性能<br>(オン抵抗, スイッチング損失,<br>小型化, 高温での動作) | 0        | Δ                       |  |  |

| コ <i>スト</i><br>(基板, 製造プロセス)            | ×        | 0                       |  |  |

| 他回路との相性                                | 素子単体で使用  | 他の回路と組み合わせ可<br>Si ⇒ 集積化 |  |  |

半導体にとって「安さ」は重要 Siで高性能を追求

- 研究背景•目的

- 従来型・提案型LDMOSトランジスタ構造

- シミュレーション結果

- I<sub>DS</sub>-V<sub>GS</sub>特性

- I<sub>DS</sub>-V<sub>DS</sub>特性

- ブレークダウン特性

- 特性オン抵抗-ブレークダウン電圧特性

- ホットキャリア耐性

- ・まとめ

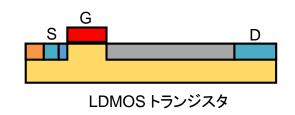

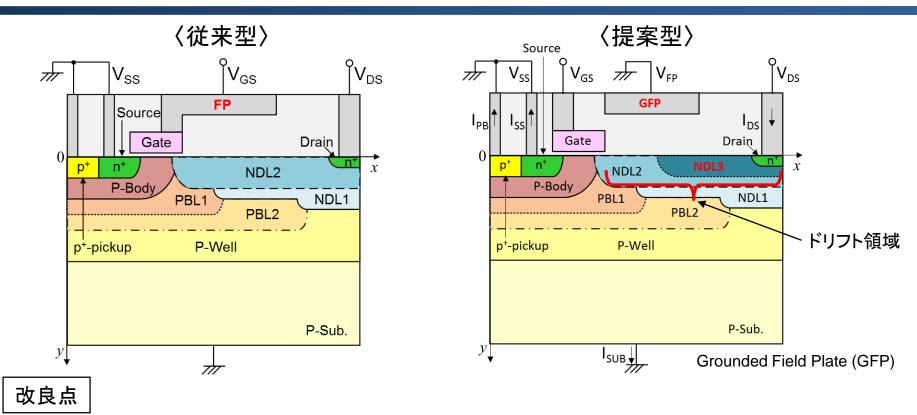

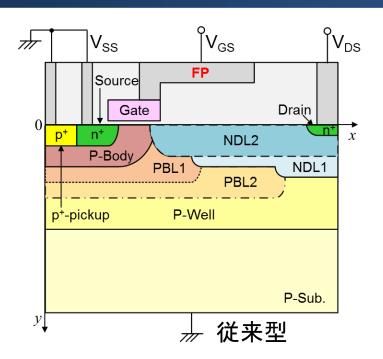

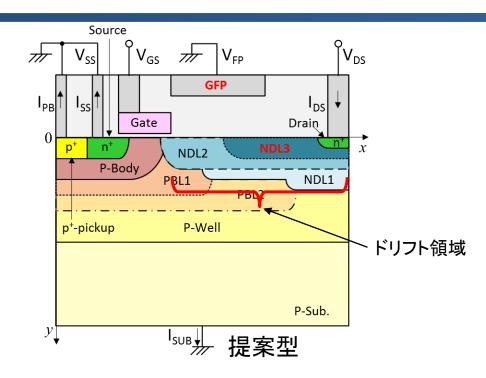

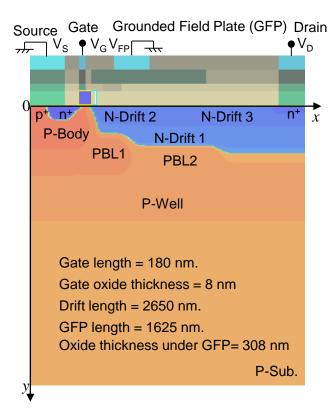

## 従来型・提案型のLDMOSトランジスタ構造

- NDL3 (ゲート側ドリフト領域を除く) ⇒ 電流増大の抑制(広SOA)、特性オン抵抗の低減

- ・フィールド・プレートの接地 ⇒ ミラー容量の低減(スイッチング損失低減)、RESURFの補助

電子デバイス・半導体電力変換合同研究会, EDD-17-082,SPC-17-181, (2017年11月)で発表

#### 発表の重点内容

・ドリフト領域の長さを50%まで比例縮小して、20-40V 動作での特性を確認 (広SOA、高信頼性を確保できているか)

- 研究背景•目的

- ・ 従来型・提案型LDMOSトランジスタ構造

- ・ <u>シミュレーション結果</u>

- I<sub>DS</sub>-V<sub>GS</sub>特性

- I<sub>DS</sub>-V<sub>DS</sub>特性

- ブレークダウン特性

- 特性オン抵抗-ブレークダウン電圧特性

- ホットキャリア耐性

- ・まとめ

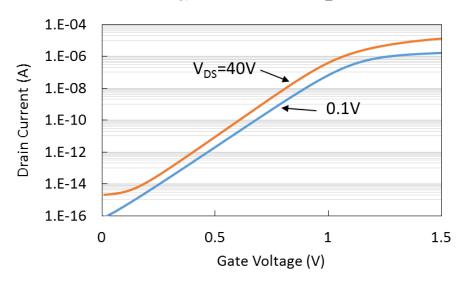

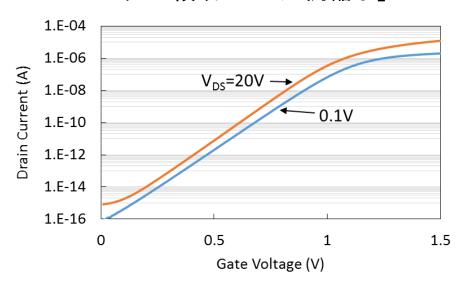

## 提案型のI<sub>DS</sub>-V<sub>GS</sub>特性

#### ドリフト領域「縮小なし」

#### ドリフト領域「50%比例縮小」

| ドリフト領域                                | 縮小     | なし     | 50%比例縮小 |        |  |

|---------------------------------------|--------|--------|---------|--------|--|

| ドレイン電圧V <sub>DS</sub>                 | 0.1V   | 40V    | 0.1V    | 20V    |  |

| しきい値電圧<br>(at I <sub>DS</sub> =0.1µA) | 1.026V | 0.922V | 1.023V  | 0.923V |  |

|                                       | 1      |        |         |        |  |

しきい値電圧のシフト量は「縮小なし」と「50%比例縮小」でほぼ同じ

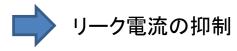

## 提案型のI<sub>DS</sub>-V<sub>DS</sub>特性

#### ドリフト領域「縮小なし」

# 電流増大(Current Expansion:CE) 200 (Yil) 150 V<sub>GS</sub> = 4V 3.3V 3V 2.5V

× 2V

30

Draiin Voltage (V)

Boundary of SOA

50

60

40

#### ドリフト領域「50%比例縮小」

■ 20-40V 動作における広SOAの確保

20

10

0

0

| ドリフト領域                                       | 縮小なし                   | 50%比例縮小                |  |  |

|----------------------------------------------|------------------------|------------------------|--|--|

| 電流増大なしの領域<br>(at 最大定格電圧 V <sub>GS</sub> =4V) | 0≦V <sub>DS</sub> ≦40V | 0≦V <sub>DS</sub> ≦22V |  |  |

| 電流増大なしの領域<br>(at 動作電圧 V <sub>GS</sub> =3.3V) | 0≦V <sub>DS</sub> ≦45V | 0≦V <sub>DS</sub> ≦25V |  |  |

■ 特性オン抵抗 R<sub>on</sub>A :提案型 ⇒ 40.9 mΩ·mm² (at V<sub>GS</sub>=3.3V, V<sub>DS</sub>=0.6V) (従来型 ⇒ 44.8 mΩ·mm² と比べて提案型は約10%低減)

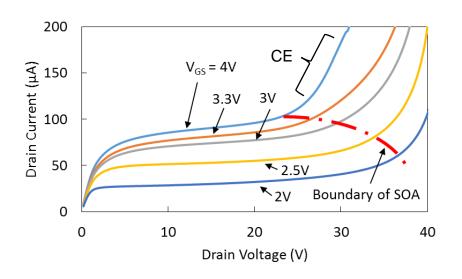

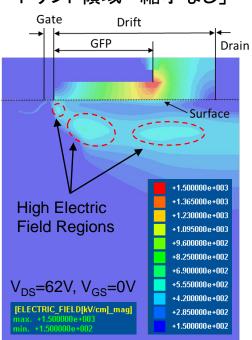

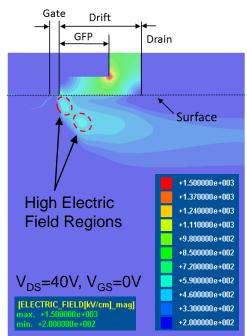

#### ブレークダウン特性

■ ブレークダウン電圧BV<sub>DS</sub>:

ドリフト領域「縮小なし」 ⇒ 62V (at I<sub>DS</sub>=10<sup>-13</sup>A) 「50%比例縮小」⇒ 40V

20-40V 動作に対して余裕あり

#### ドリフト領域「縮小なし」

#### ドリフト領域「50%比例縮小」

#### ブレークダウン時の電界強度分布

■ ドリフト領域の縮小「あり」「なし」の構造で ブレークダウンはバルクで発生

電子・正孔による ゲート酸化膜、界面への影響を抑制

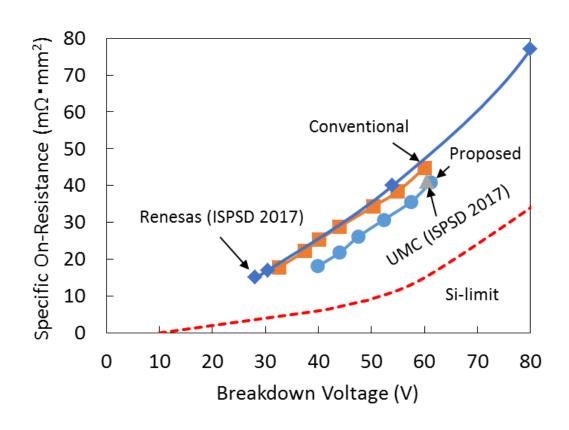

## 特性オン抵抗-ブレークダウン電圧特性

■ 提案型のR<sub>on</sub>A-BV<sub>DS</sub>特性 ⇒ { UMC社 (ISPSD 2017 で発表) と同等の性能 先端レベル

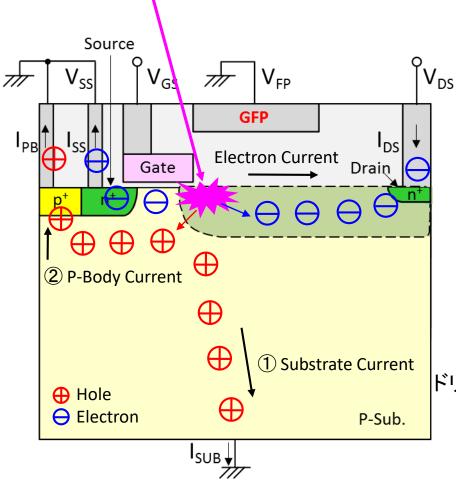

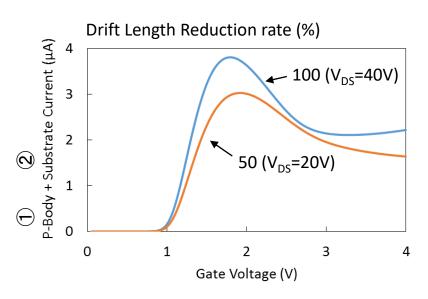

## ホットキャリア耐性

ホットキャリア: 熱平衡状態よりも高いエネルギー状態になった電子

インパクトイオン化:電子が結晶格子と衝突し、電子・正孔を発生

大電流が流れる

・電子がゲート酸化膜ヘトラップしてしきい値の上昇

ドリフト領域「縮小なし」「50%比例縮小」で正孔電流を抑制

ホットキャリア耐性を得ると考える

- 研究背景•目的

- ・ 従来型・提案型LDMOSトランジスタ構造

- シミュレーション結果

- I<sub>DS</sub>-V<sub>GS</sub>特性

- I<sub>DS</sub>-V<sub>DS</sub>特性

- ブレークダウン特性

- 特性オン抵抗-ブレークダウン電圧特性

- ホットキャリア耐性

- まとめ

## まとめ

#### 車載用 20-40V 動作 のLDMOSトランジスタを提案

広SOAの確保

```

「ドリフト領域「縮小なし」 \Rightarrow V_{DS} \leq 40V ドリフト領域「50%比例縮小」 \Rightarrow V_{DS} \leq 22V で電流増大(CE)の発生なし (at ゲート最大定格電圧 V_{GS}=4V)

```

- ホットキャリア耐性の確保

- 特性オン抵抗-ブレークダウン電圧特性は先端レベル

- 20-40V 動作で複数のLDMOSトランジスタをレイアウトのみ変更し、 製造プロセスコストを上げることなく1チップ上に作製可能 ⇒回路設計の自由度が上がる

## 謝辞

本研究を進めるにあたり、3D TCADを貸していただいたアドバンスソフト社に深謝いたします。

この3D TCADは、国立研究開発法人科学技術振興機構A-STEPプログラムの助成を受けてアドバンスソフト社で開発されています。

## 付録

## まとめ

| 項目                                       | 従来型  | 提案型                                                                      |  |  |

|------------------------------------------|------|--------------------------------------------------------------------------|--|--|

| ドレイン電流増大(CE)<br>(at V <sub>GS</sub> =4V) |      | ドリフト領域「縮小なし」V <sub>DS</sub> ≦40V CE発生なし<br>「50%比例縮小」V <sub>DS</sub> ≦22V |  |  |

| $R_{on}A (m\Omega \cdot mm^2)$           | 44.8 | 40.9                                                                     |  |  |

| BV <sub>DS</sub> (V)                     | 60   | 62                                                                       |  |  |

| ブレークダウンの箇所                               | バルク  | バルク                                                                      |  |  |

| $FOM(=R_{ON}\times Q_g) (m\Omega nC)$    | 141  | 48.2                                                                     |  |  |

| スイッチング損失                                 |      | 高周波数帯で小さい                                                                |  |  |

## 3D TCADシミュレータ

3D TCADシミュレータ ・・・ Advance/DESSERT(サンプル版) アドバンスソフト株式会社

・実物に近いモデルの使用

高精度

\*実物を作らなくても良い

短時間で多くの構造の開発・評価

シミュレータ画面

### 従来型・提案型のLDMOSトランジスタ構造

#### 埋込p層(デュアルRESURF構造)

- ・PBL1⇒ゲート側ドリフト端のRESURF強化(高ホットキャリア耐性)、CE抑制

- ・PBL2⇒ドリフト層全体のRESURFに有効

- ・ドレイン下のPBL2開口⇒ブレークダウン電圧低下防止

#### ドリフト層(3層構造)

- ・NBL1(深い領域)⇒ドリフトの基本層

- ・NBL2(浅い領域)⇒CE抑制、特性オン抵抗低下

- ・NBL3(浅い領域:ゲート側ドリフト端領域除く)⇒CE抑制を強化(広SOA)、特性オン抵抗より低下

#### フィールド・プレート

・フィールド・プレート(接地)⇒ミラー容量低減(スイッチング損失低減)、RESURF補助

## 提案型LDMOSトランジスタの構造

#### 0.18μm CMOS プロセスベース

| Name             | Impurity | Maximum<br>Concentration<br>(cm <sup>-3</sup> ) | Peak<br>Location<br>(nm) | Standard<br>Deviation<br>(nm) | Uniform<br>Distribution<br>(cm <sup>-3</sup> ) | Lateral<br>Diffusion<br>Coeffient | Diffusion | Window (nm) |

|------------------|----------|-------------------------------------------------|--------------------------|-------------------------------|------------------------------------------------|-----------------------------------|-----------|-------------|

| Gate             | Р        | 0.00E+00                                        | 0                        | 0                             | 1.00E+20                                       | 0.7                               | Blanket   | 700-880     |

| Source n+        | As       | 1.00E+20                                        | 0                        | 80                            | 0                                              | 0.7                               | Stripe    | 250-500     |

| Source n-        | Р        | 3.70E+18                                        | 0                        | 45                            | 0                                              | 0.7                               | Stripe    | 300-700     |

| Drain n+         | As       | 1.00E+19                                        | 0                        | 50                            | 0                                              | 0.7                               | Stripe    | 3530-3930   |

| n-drift 1        | Р        | 7.00E+16                                        | 0                        | 400                           | 0                                              | 0.7                               | Stripe    | 880-3930    |

| n-drift 2        | Р        | 8.50E+16                                        | 0                        | 200                           | 0                                              | 0.7                               | Stripe    | 880-3930    |

| n-drift 3        | Р        | 3.50E+16                                        | 0                        | 150                           | 0                                              | 0.7                               | Stripe    | 1650-3930   |

| p-well           | В        | 2.00E+16                                        | 0                        | 1000                          | 1.00E+15                                       | 0.7                               | Blanket   | 0-3930      |

| p-body           | В        | 5.00E+18                                        | 300                      | 150                           | 0                                              | 0.7                               | Stripe    | 0-650       |

| p+ pickup        | В        | 1.00E+20                                        | 0                        | 80                            | 0                                              | 0.7                               | Stripe    | 0-250       |

| Vt               | В        | 1.30E+18                                        | 0                        | 50                            | 0                                              | 0.7                               | Stripe    | 0-760       |

| p-buried layer 1 | В        | 3.00E+17                                        | 700                      | 150                           | 0                                              | 0.7                               | Stripe    | 0-1230      |

| p-buried layer 2 | В        | 3.00E+16                                        | 800                      | 150                           | 0                                              | 0.7                               | Stripe    | 0-2530      |

## **Q&A**

#### 羽賀先生より

Q. シミュレーションはどんな解析法を用いている?

A. ポアソンと電流連続の式。ポアソンは電界・電圧を、電流連続は電流を求める。 ラプラスの式では電界が含まれていない。

Q.11ページで、電界が直角に表示されているが、それでよいのか?実際は丸びを帯びているのではないか?

A. シミュレーション上の関係で直角に表示される。また、ブレークダウンがバルク内で発生していることが重要であり、構造の上部は影響はほとんどないと見る。