# 単位セル並び替えと巡回選択方法を用いた Δ Σ DA 変換器の高線形化

串田 弥音\* 小島 潤也 村上 正紘 小林 春夫(群馬大学)

High Linearization of  $\Delta\Sigma$ DA Converter Using Unit Cell Reordering and Cyclic Selection Method Nene Kushita\*, Jun-ya Kojima, Masahiro Murakami, Haruo Kobayashi (Gunma University)

キーワード: Δ Σ 変調, マルチビット DA 変調器, 単位セル並び替え、単位セル巡回選択法 (Delta Sigma DAC, Multi-bit DAC, Unit Cell Reordering, Unit Cell Cyclic Selection)

## 1. はじめに

自然界に存在する物理量をつなぐものとしてアナログデジタル/デジタルアナログ変換器(ADC/DAC)が必要不可欠である。その中でもデルタシグマ( $\Delta\Sigma$ )変調に基づく DA変換方式は大部分がデジタル回路で構成されており直流信号や低周波信号を高分解能,高線形に生成できるための DA変換器としてよく利用されている。高性能化のためデジタル変調器の後段にセグメント型マルチビット DA変換器を用いると、それぞれの単位セル回路(電流源または容量)がもつ素子ばらつきにより  $\Delta\Sigma$  DA変調器全体の線形性が劣化する問題がある。この影響は素子巡回選択方法で DAC素子を順番に選択し、それぞれの素子の使用回数を平均化することで軽減されることが知られている。[1]

本論文ではさらに比較器を用い単位セル回路の大きさの順番を測定し、その情報をもとに(ソフト的に)並び替えてその後巡回選択方法を実行することでさらに  $\Delta \Sigma DA$  変調器の線形性が向上することを示す。

## 2. Δ Σ DA 変調器(デジタル変調器)

## 〈2·1〉 Δ Σ DA 変調器の構成

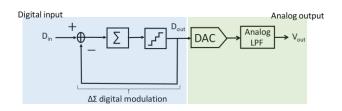

$\Delta \Sigma DA$  変換器は図 1 で示すように前段はデジタル  $\Delta \Sigma$  変調回路で構成され、後段はアナログ回路で構成されている。  $\Delta \Sigma DA$  変調器は積分器とデジタル量子化器のフォードバック構成であり、すべてデジタル回路で実現される。変調器内ループではすべての信号はデジタルであり、ループ内での信号処理制度は高く、ループの挙動を予測する際にはアナログのような不完全性を考慮する必要がない。この回路では、オーバーサンプリングした入力信号を積分器で累積し、デジタル量子化器で上位ビットのみを取り出し、後段のDACへ入力する。デジタル量子化器は $\Delta \Sigma$ 変調の出力値となると同時に入力にフォードバックし累積値にMSB 値が加減される。出力信号を高速フーリエ変換(FFT)すると量子

化ノイズがサンプリング周波数 f<sub>s</sub>より低い周波数で量子化 誤差が減衰し、高周波帯域で増加する。このノイズシェイピ

図1 ΔΣ変調器の構成

Fig. 1. Block diagram of a  $\Delta\Sigma DA$  converter

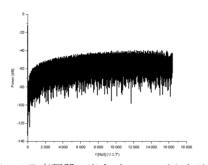

図 2  $\Delta\Sigma$ 変調器の出力パワースペクトラム (入力信号: 振幅 1V, 正規化周波数 1Hz の正弦波) Fig. 2. Power spectrum of the  $\Delta\Sigma$  modulator output

Fig. 2. Power spectrum of the  $\Delta\Sigma$  modulator output (Input sine wave amplitude: 1, normalized frequency: 1)

ング(noise harping)と呼び、確認することができる(図 2) **〈2·2〉セグメント型 DAC の**電流源ミスマッチ

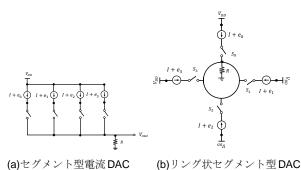

この論文では $\Delta \Sigma$ 変調器に用いられる DAC はセグメント型 DAC で考える。図 3(a)に示すような 5 レベルの分解能を持つセグメント型 DAC を考える。DAC は 4 個の電流源と抵抗から構成される。k 番目の電流源を I(k=0,1,2,3) とすると、理想的にはすべての電流は等しいが、実際には IC

チップ製造上においてはプロセスのばらつきにより電流が異なる。図  $3 \, oe_k$ は電流源のミスマッチ(平均電流からのずれ)であり、DAC においてはシェイピングを受ける「ノイズ」は量子化雑音ではなく DAC レベルのばらつきである。

これまでにミスマッチ誤差シェイピングを実現する多くの手法が提案されている。よく使用されるものとして、「素子巡回選択方法」、「個別レベル平均化」、「ベクトル・ミスマッチングシェイピング」、「ツリー構造素子選択」があげ

図 **3** 電流 DAC

Fig. 3. Current DAC

られる[2]。

# 〈2·3〉素子巡回選択方法

DAC の非線形性によって生じる誤差を低減するため、素子 巡回選択方法、またはデータ重み付け平均化(DWA)[2]を考える。構成はセグメント型 DAC をリング状に配列した形である(図 3(b))。 DAC の電流源に番号をつけ、ON になる電流源の位置を記憶する Pointer を設ける。時刻 n での DAC の Pointer を P(n)とする。DAC 素子を順番に選択しそれぞれの素子の使用回数を平均化することでマルチビット DAC 非線形性誤差はノイズシェイピングを実現する。入力信号 3 の時には電流セル 0,1,2 が ON になり、次に入力データが 1 のときに 3 が ON になり、次に入力データが 1 のときに 3 が ON になり、次に入力データが 1 のときに 3 が ON になり、次に入力データが 1 のときに 1 の ON になる。入力信号が 1 の ON になる。入力信号が 1 のとき電流セルはすべて OFF となる。この動作を行わせるため、Pointer の P(n) に現在の DAC 入力信号を記憶させ次の DAC の動作に反映

図 4 素子巡回選択方法(DWA)

Fig. 4. Selection method of current cells with DWA

する(図 4)。

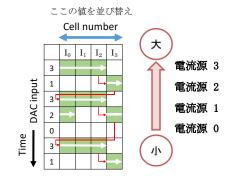

#### 〈2·4〉単位セル回路の並び替え

素子巡回選択方法同様に、DAC の非線形性によって生じる誤差を低減するため、図 5 において、比較器を用いて電流セルの大小関係を計測し、その情報をもとに電流セルの並び替えを(ソフト的に)行う。この並び替え方法として図 3 の $e_k$ は電流源のミスマッチ(平均電流からのずれ)を比較器により小さい順から 0,1,2,3 とする。また、線形性が向上

図 5 単位セル並び替え

Fig. 5. Reordering unit cells

する順列に並び替えを行う。

#### 〈2·5〉 SNDR での評価

DA 変換の性能評価の 1 つに Signal to Noise and Distortion Ratio (SNDR)がある。これは出力での信号成分電力と発生したノイズ電力の比である。ここでは SNDR を用いてシミュレーション結果を評価する。SNDR が向上すれば DA 変換の性能向上を意味する。[1]

## .3. シミュレーションによる検証

# 〈3·1〉シミュレーション回路の構成

本論文では素子巡回選択方法、単位セル回路の並び替えの組み合わせを用いた 2 次  $\Delta$   $\Sigma$  変調器を検討する。最初は電流源 0, 1, 2, 3 を用い、全 24 通りの並び替えのシミュレーションを行い、線形性が向上する並び替えを確認する。また、この回路を 6 通り確認する。

振幅 1.7V 正規化周波数 1Hz の入力信号を与えた。

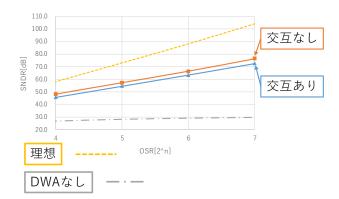

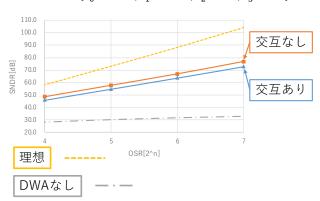

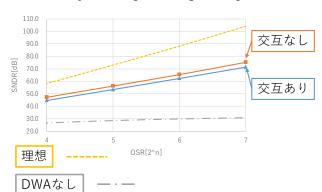

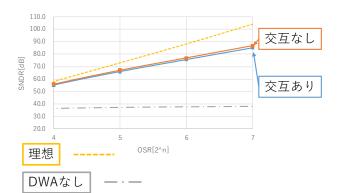

# 〈3·2〉SNDR の向上(2<sup>15</sup>)

入力信号には正規化周波数 1 の正弦波を入力した。素子巡回選択方法、単位セル回路の並び替えの組み合わせを用いた 2 次  $\Delta$   $\Sigma$  変調器の 4 出力では電流源 0, 1, 2, 3 を用い、全 24 通りの並び替えのシミュレーションを行い、結果を図 6 に示す。ばらつきが異なるものを 6 通り用意してシミュレーションを行った。また、これにより得られた結果を表 1 に示す。今回用いたばらつきでは電流源の出力理想値の 1.0 以上のものを 2 つ、1.0 以下のものを 2 つ設定したものを 5 つ。電流源の出力理想値の 1.0 以上のものを 1 つ、

(a) 電流源のミスマッチ  $(e_0 = -0.5, e_1 = -0.2, e_2 = 0.2, e_3 = 0.5)$

(b) 電流源のミスマッチ  $(e_0 = -0.4, e_1 = -0.3, e_2 = 0.2, e_3 = 0.5)$

(c) 電流源のミスマッチ  $(e_0 = -0.5, e_1 = -0.3, e_2 = 0.2, e_3 = 0.6)$

(d) 電流源のミスマッチ  $(e_0=-0.1,e_1=-0.05,e_2=-0.02,e_3=0.17)$

(e) 電流源のミスマッチ  $(e_0 = -0.25, e_1 = -0.23, e_2 = 0.01, e_3 = 0.22)$

(f) 電流源のミスマッチ  $(e_0=-0.2,e_1=-0.13,e_2=0.02,e_3=0.11)$  図 6 シミュレーション結果

Fig. 6. Simulation results of SNDR

1.0以下のものを2つ設定したものを1つ用意した。

シミュレーション結果より、ばらつきが電流源の出力理想値の1.0以上のものを2つ、1.0以下のものを2つであるとき、素子巡回選択方法(DWA)を用い、出力理想値1.0以上のものと出力理想値1.0以下のものの並び替えより、ミスマッチの正負交互なしの組み合わせ回路では線形性向上が確認できる。ばらつきが電流源の出力理想値の1.0以上のものを1つ、1.0以下のものを3つであるとき、素子巡回選択方法(DWA)を用い、ミスマッチの正負交互なしの組み合わせ回路でも同様に線形性向上が確認できる。ミスマッチの正負交互なしの場合素子巡回選択方法を使用しない回路と比べ線形性向上が確認できる。さらにミスマッチ正負交互なしの並び替え選択がより理想的な線形性に近づくことが確認できる。図6では交互なしの16通りを平均したSNDR、交互ありの8通りを平均したSNDRのグラフを示し、表1は図7(b)のシミュレーション結果を示す。

### 表1 シミュレーション結果

Table 1. Simulation results of SNDR

|          |       | 0SR[2 <sup>n</sup> ] |       |       |      |       |       |      |       |

|----------|-------|----------------------|-------|-------|------|-------|-------|------|-------|

|          |       | 0                    | 1     | 2     | 3    | 4     | 5     | 6    | 7     |

| SNDR[dB] | 理想    | 5.6                  | 14.5  | 28.0  | 43.0 | 58. 2 | 73. 2 | 88.4 | 104.4 |

|          | 交互あり  | 5.0                  | 13. 3 | 25. 5 | 36.9 | 45.9  | 54.8  | 63.7 | 72.8  |

|          | 交互なし  | 4.5                  | 12.5  | 22. 3 | 38.0 | 48.6  | 57.8  | 67.0 | 77.0  |

|          | DWAなし | 5.6                  | 13.8  | 21.9  | 25.6 | 28. 1 | 30.1  | 31.6 | 32.8  |

図 7(b)のシミュレーション結果

## 4. まとめ

本論文ではマルチビット AEDA 変換器の線形性向上のために、素子巡回選択方法と単位セル回路の並び替えを用いた組み合わせ回路の並び替えを用いることで、従来よりもSNDR が向上した。単位セル回路の並び替えでは、比較器を用いることでミスマッチの正負交互ありと比べミスマッチが正負で交互なしの場合がより理想的な線形性に近づくことが可能である。これは分解能レベルが上がると、ミスマッチ正負の交互あり、なしの SNDR の差が大きくなると考えられる。

## 5. 課題

今回、用いた DAC は 5 レベルの分解能を持つセグメント型 DAC である。 さらに 9 レベル、17 レベルの分解能を持つセグメント型 DAC でも、5 レベルと同様にミスマッチ正負交互なしの場合に理想的な線形性に近づくかどうかの検討を行なっていく。

#### 文 献

- (1) 小島潤也 村上正紘 小林春夫:「マルチビット ΔΣDA 変換器の線 形性向上アルゴリズムの検討 - DWA, 自己校正およびその組み 合わせ」, 第 7 回 電気学会東京支部栃木・群馬支所 合同研究発表 会 (2017年)

- (2) 和田孝夫, 安田 彰: 「Δ Σ アナログ/デジタル変換器入門」, pp.152-163 (2007 年)

- (3) I. Jang, M. Seo, M. Kim, J. Lee, S. Baek, S. Kwon, M. Choi, H. Ko, S. Ryu.

- $\label{eq:cond-order} \begin{tabular}{ll} \b$

Symposia on VLSI Technology and Circuits, Kyoto Japan, June  $2017\,$

(4) J. Kojima , N. Kushita , M. Murakami and H. Kobayashi, "Linearity Improvement Algorithms of Multi-bit ΔΣDA Converter - DWA, Self-Calibration and Their Combination", International Conference on Mechanical, Electrical and Medical Intelligent System, Kiryu (Nov. 2017) .