The 27th IEEE Asian Test Symposium Oct.15-18,2018,Hefei,Anhui,China Oct. 18, 2018 Session 6B-II Mixed-Signal IC Designs and ATE

# Time-to-Digital Converter Architectures Using Two Oscillators With Different Frequencies

# Kosuke Machida, Yuki Ozawa, Yudai Abe <u>Haruo Kobayashi</u>

**Gunma University**

Investigation of TDC architectures with Verner oscillators

- Analog centric one

Using trigger circuits

Two oscillators with different frequencies

No self-calibration required

Digital centric one

- Digital centric one

Two ring oscillators

with different frequencies

# Outline

Research Background

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

# Outline

<u>Research Background</u>

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

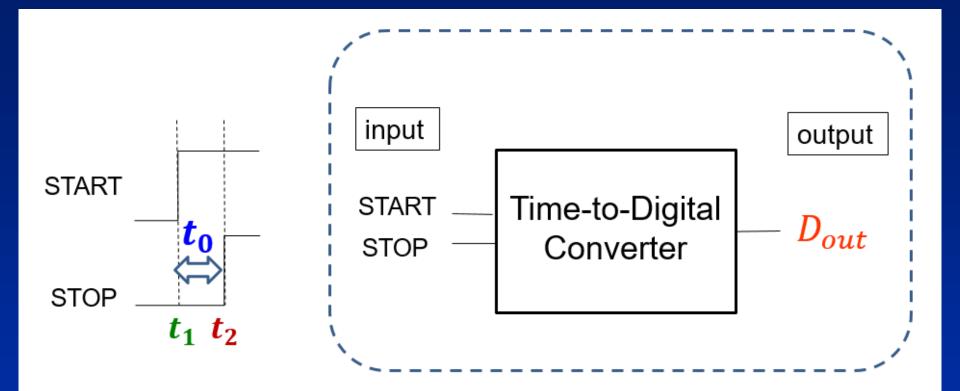

# **Time-to-Digital Converter**

Time-to-digital converter (TDC) measures

timing difference t<sub>0</sub> between t<sub>1</sub>, t<sub>2</sub>

as a digital value D<sub>out</sub>

# **TDC Application Examples (1)**

Inter-vehicular distance measurement

Satellite distance measurement

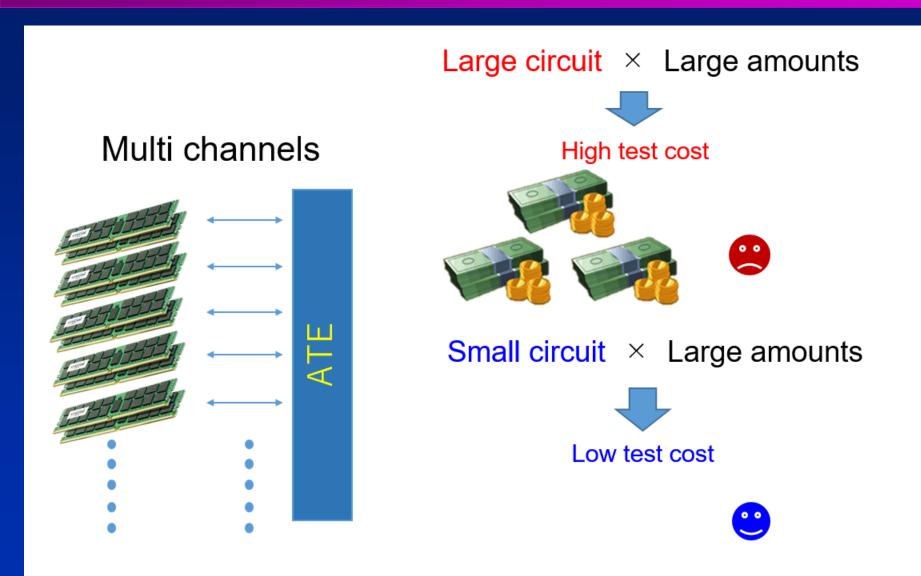

# **TDC Application Example (2)**

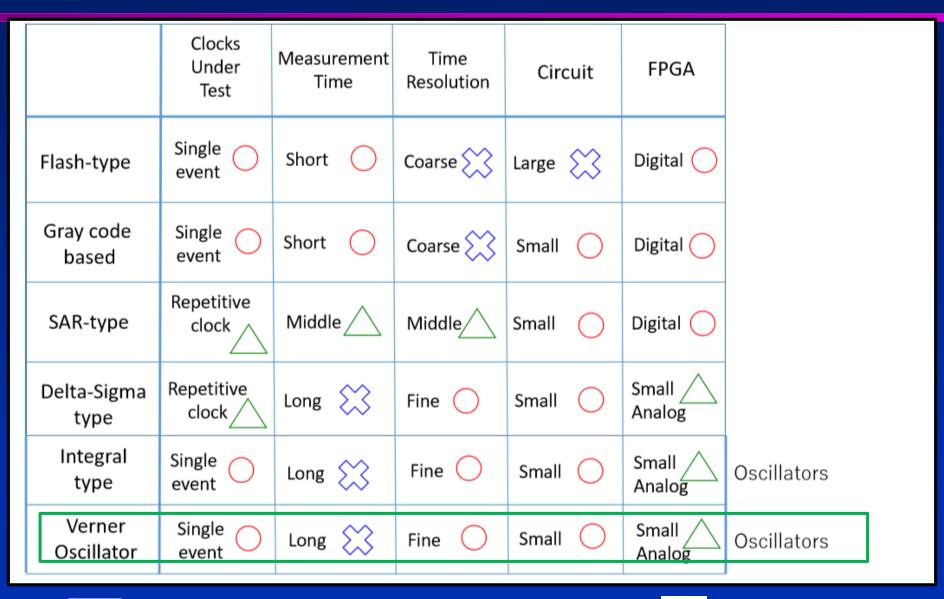

# **Comparison of TDC Architectures**

|                         | Conventional TDC                              | Proposed TDC                                                                                                                                                                                                                                                                                                  |

|-------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Circuit<br>Architecture | START $T$ | $\begin{array}{c} \sin(2\pi f_1 t) \\ \text{START} \\ \text{STOP} \\ \sin(2\pi f_2 t) \end{array} \xrightarrow{f_1} \\ \text{Trigger} \\ f_2 \end{array} \xrightarrow{f_1} \\ \text{Trigger} \\ f_2 \end{array} \xrightarrow{D_1} \\ \text{Logic} \\ \text{Circuit} \\ n_{all} \\ \text{Circuit} \end{array}$ |

| Delay<br>Line           | Necessary 🙁                                   | Not necessary 🙂                                                                                                                                                                                                                                                                                               |

| Self<br>Calibration     | Required 🙁                                    | Not required 🙂                                                                                                                                                                                                                                                                                                |

Delay array have variations → Self-calibration is required

# Outline

Research Background

<u>Measurement Principle</u>

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

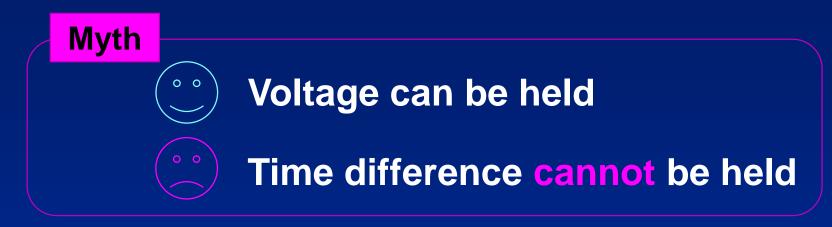

## Myth and Truth of Time Signal

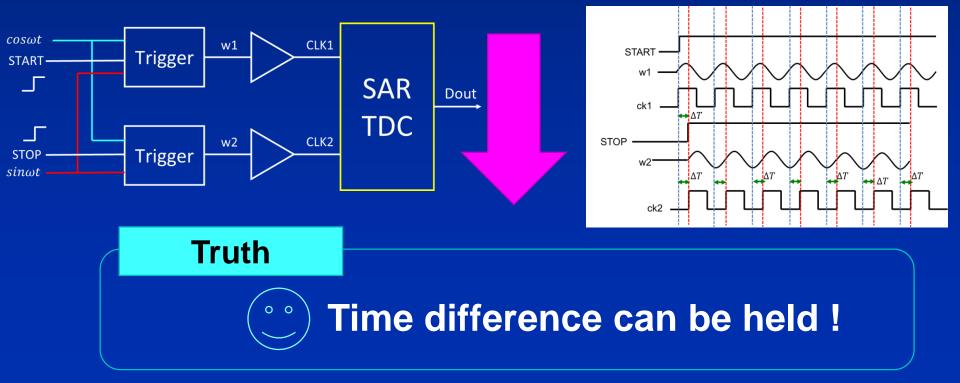

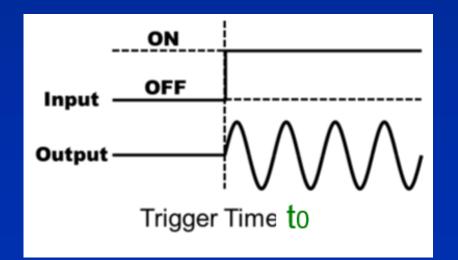

# **Trigger Circuit**

Output starts to oscillate

at rising timing edge of input

Output waveform with no transient change

M. Nelson (Tektronics) "A New Technique for Low-Jitter Measurements Using Equivalent-Time Sampling Oscilloscope", Automatic RF Techniques Group 56<sup>th</sup> Measurement Conference (Dec. 2000).

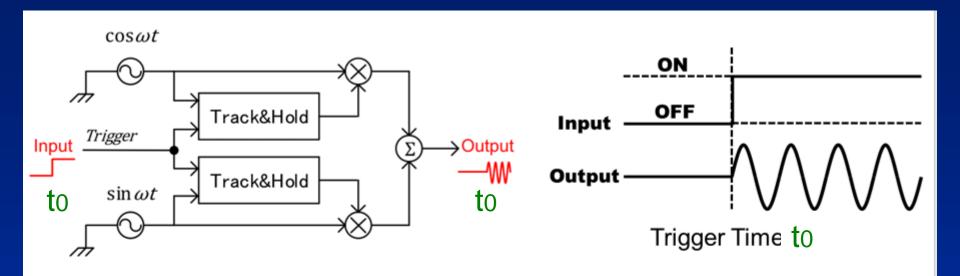

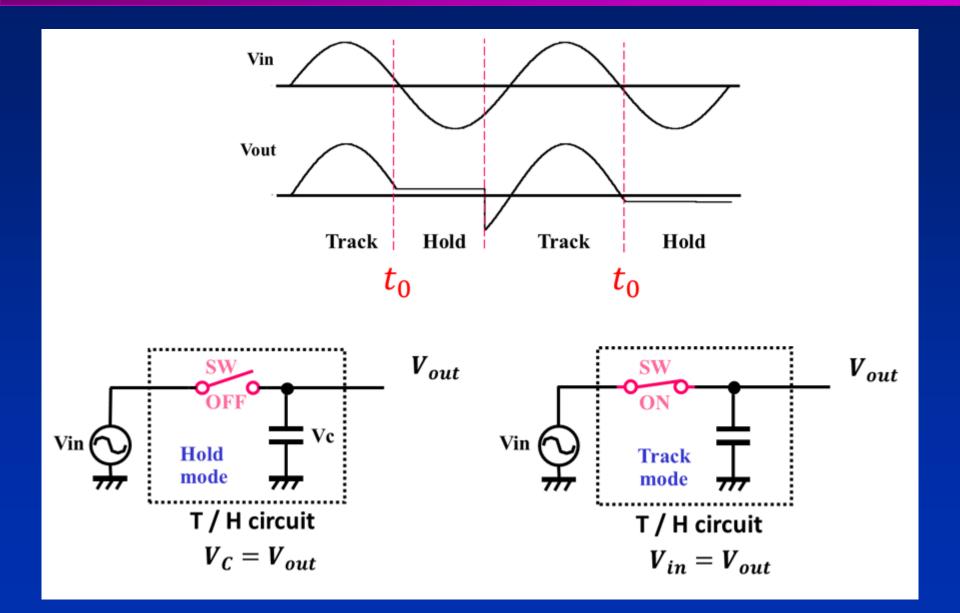

# **T/H Circuit**

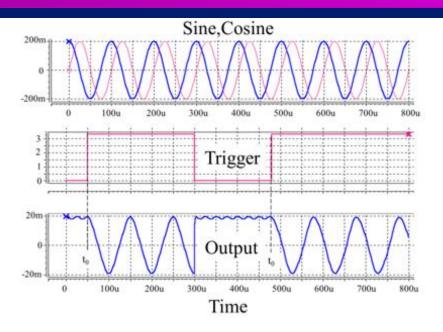

# **Trigger Circuit Waveforms**

13/48

#### T/H circuit

#### track mode

```

Vout=\cos(\omega t) \cos(\omega t) + \cos(\omega t + \pi/2) \cos(\omega t + \pi/2)

=\cos^2(\omega t) + \sin^2(\omega t)

=1

```

#### •hold mode

Vout=  $\cos(\omega t) \cos(\omega t_0) + \sin(\omega t) \sin(\omega t_0)$ = $\cos(\omega(t-t_0))$

\* trigger time:t<sub>0</sub>

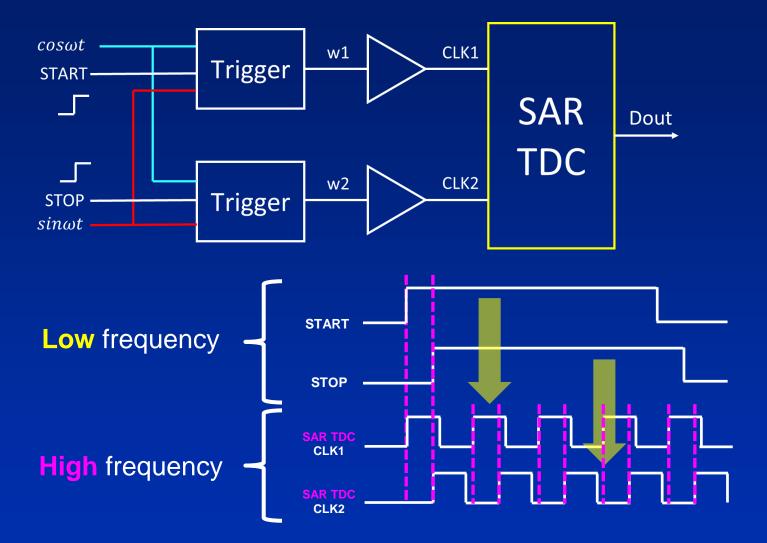

### **One-shot Timing Measurement Using Trigger Circuit**

Proposal

#### Input START, STOP signal

### Oscillate with initial phase at input timing

#### It can hold the time difference using two trigger circuits

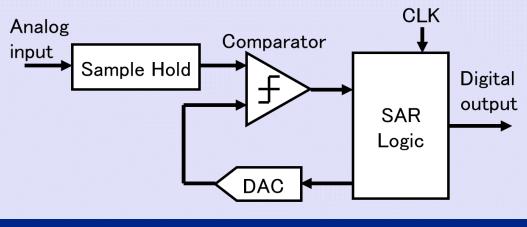

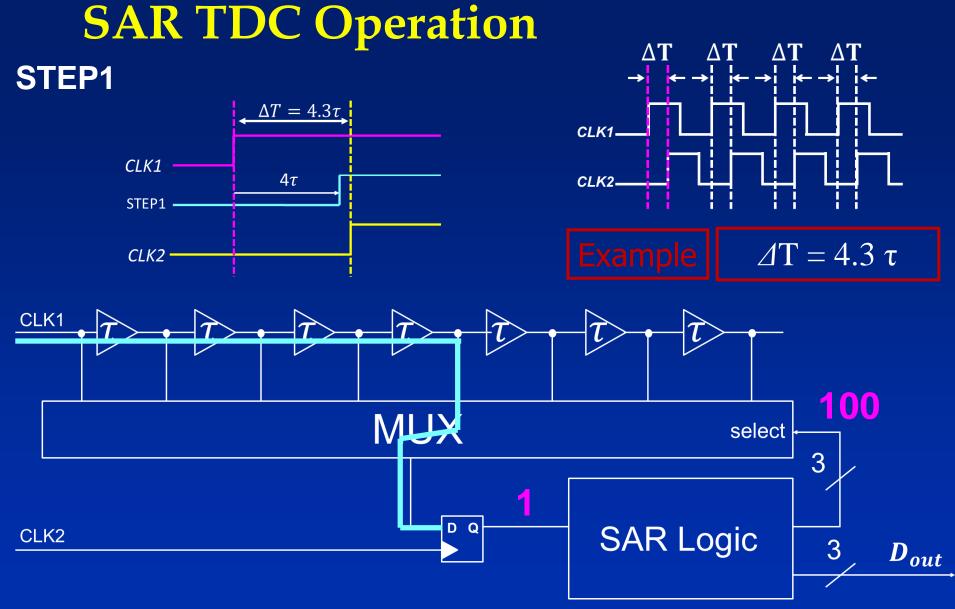

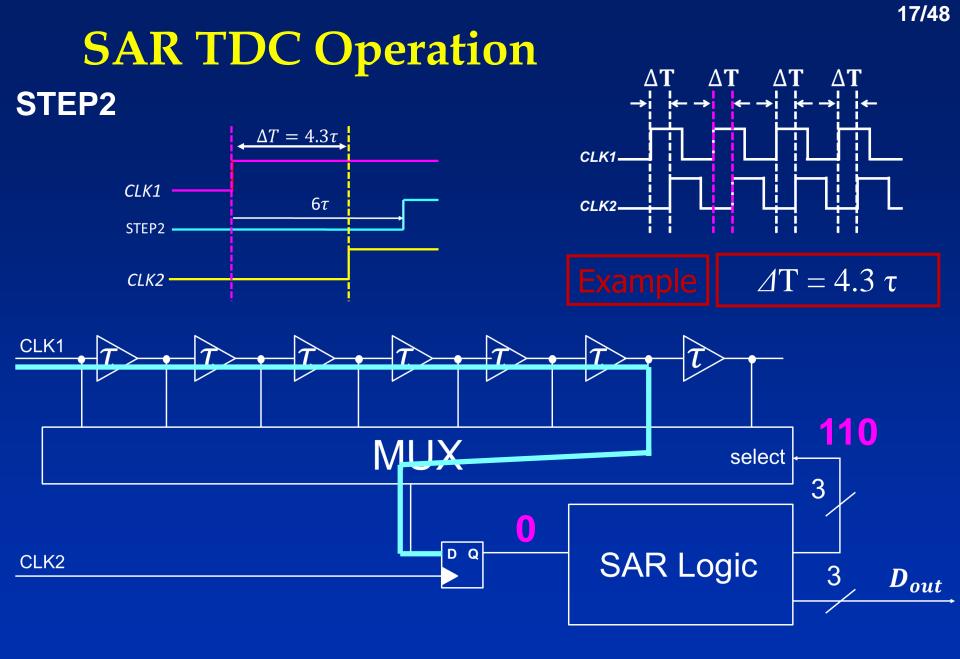

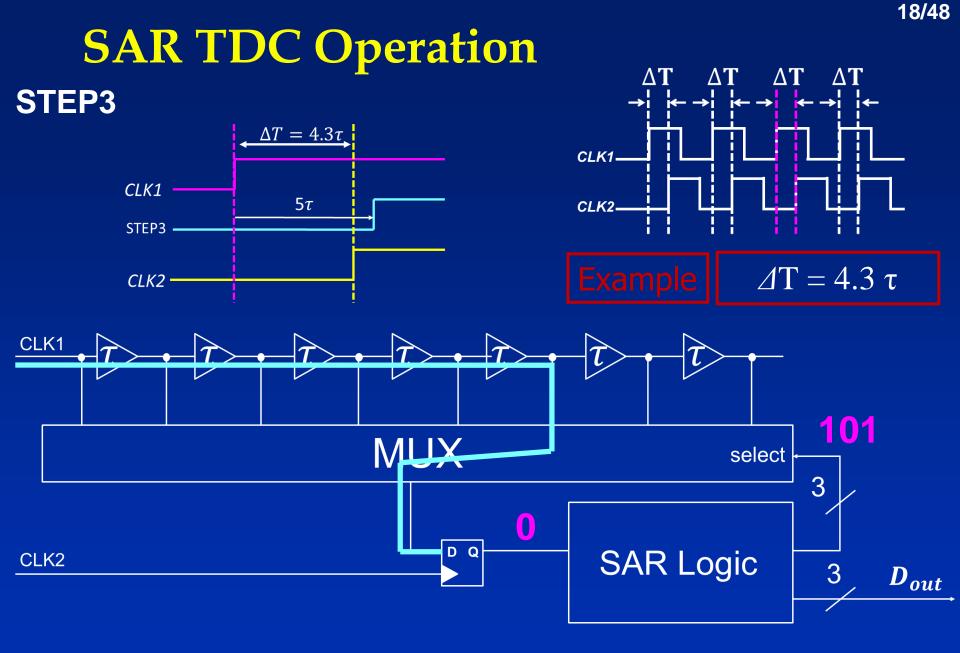

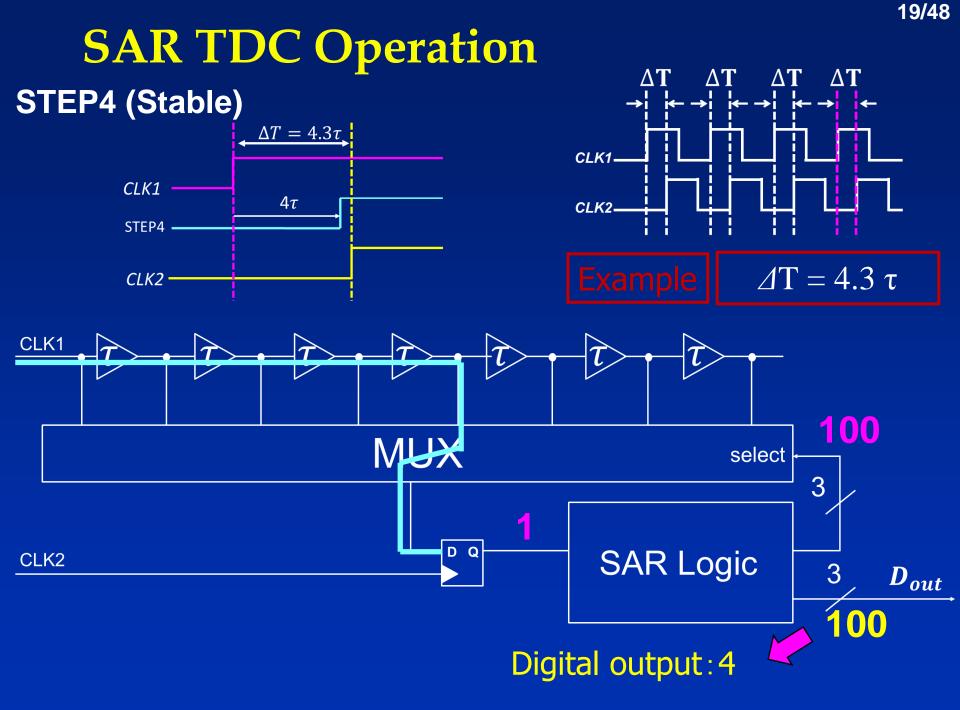

# **SAR-ADC VS. SAR-TDC**

SAR ADC :ComparatorDAC

SAR-ADC

SAR TDC :D-FFDelay line

Y. Ozawa, H. Kobayashi, et. al., "SAR TDC Architecture with Self-Calibration Employing Trigger Circuit," IEEE Asian Test Symposium, Taipei (Nov. 2017).

## Low Frequency Clock Measurement

Short testing time for low frequency repetitive timing

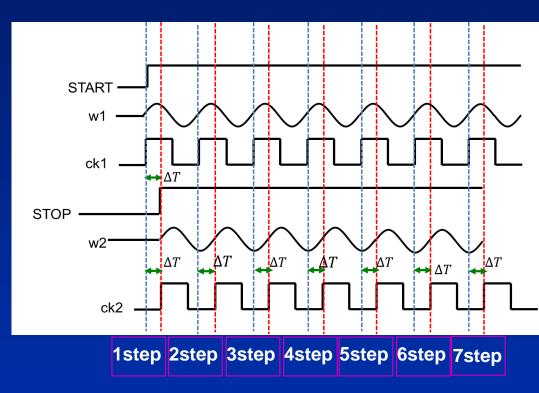

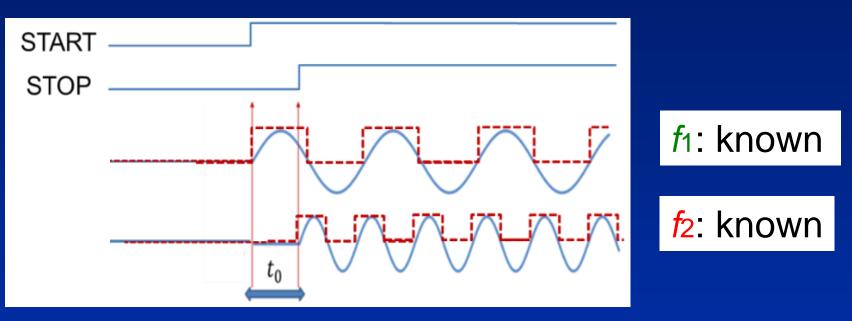

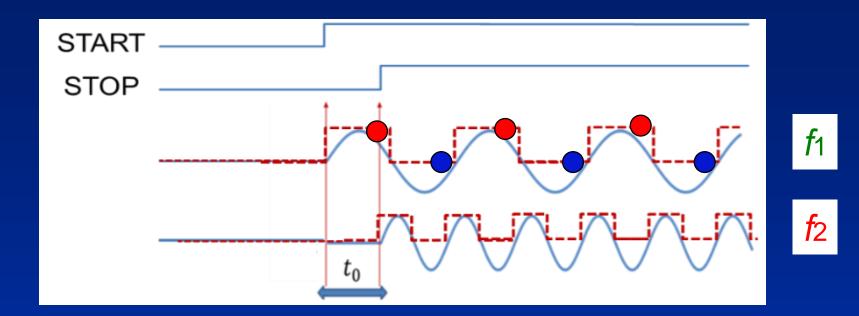

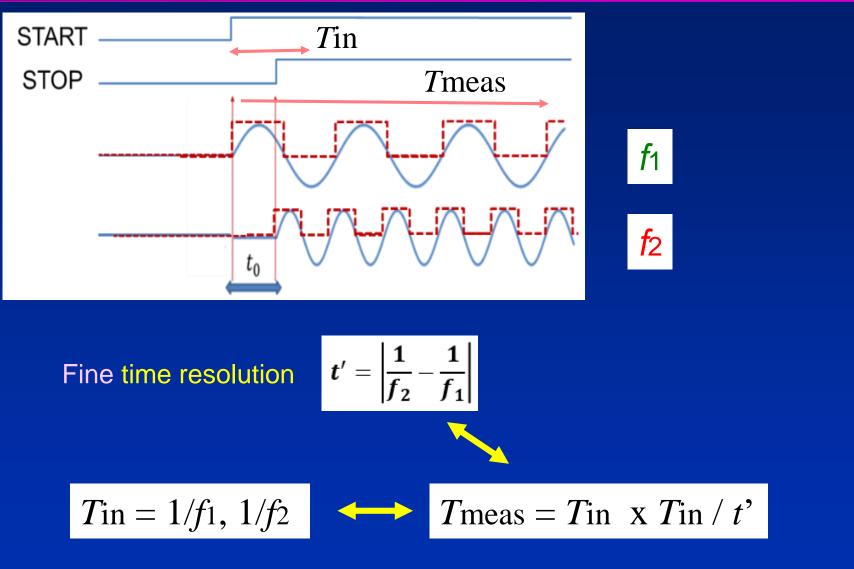

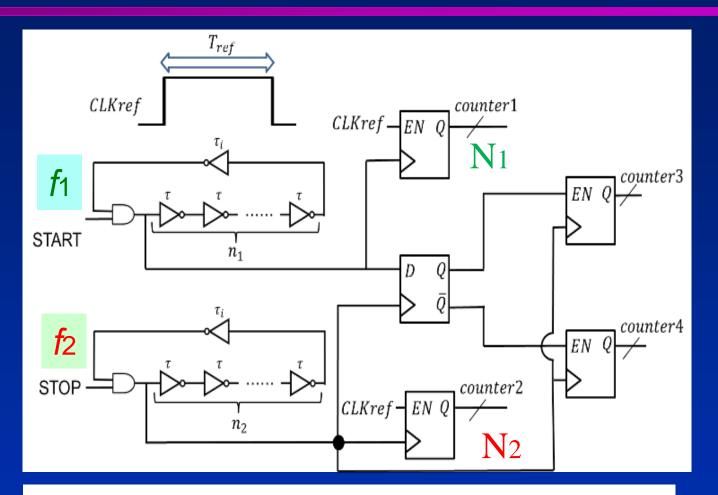

## **Verner Oscillation TDC**

### What about using different frequencies ?

### Start oscillation f1 at START edge f2 at STOP edge

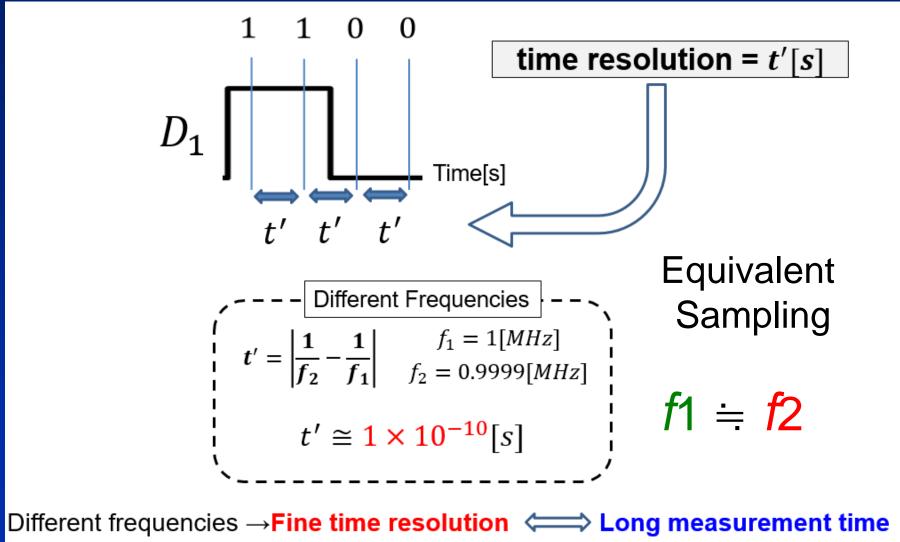

# **Verner Oscillation TDC Operation**

### $t_0 = f(f_1, f_2, \text{number of} \bullet, \bullet, \dots, \text{number of} \bullet, \bullet, \dots)$

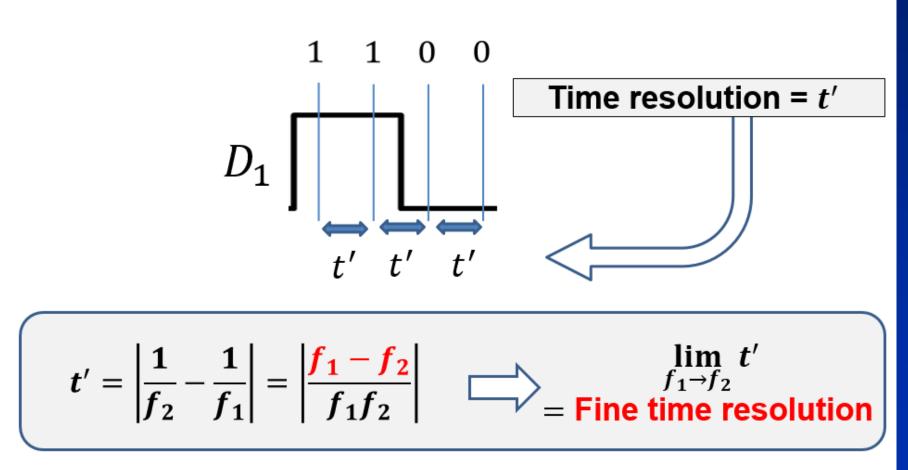

Time resolution

$$t' = \left|\frac{1}{f_2} - \frac{1}{f_1}\right|$$

## **Usage of Different but Close Frequencies**

Trade off

# **Design Tradeoff**

Wide input time range

Long Measurement time

# Outline

Research Background

Measurement Principle

<u>Analog Centric TDC</u>

Digital Centric TDC

Discussion & Conclusion

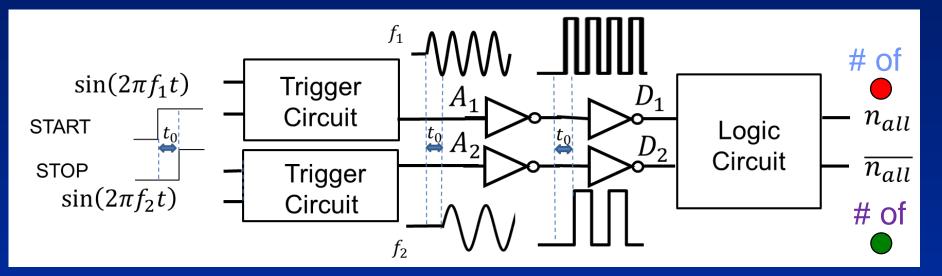

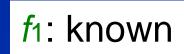

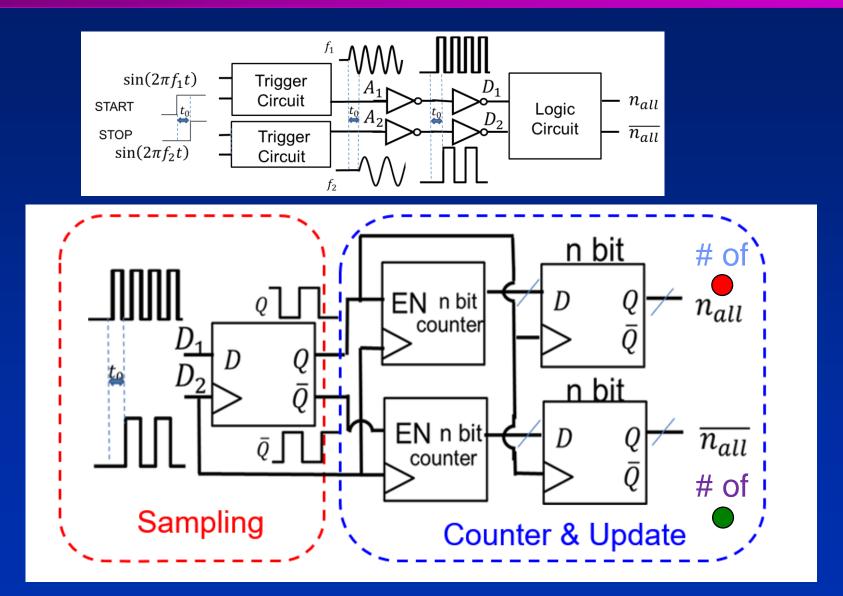

# **Proposed TDC Architecture**

# Logic Circuit for Time Measurement

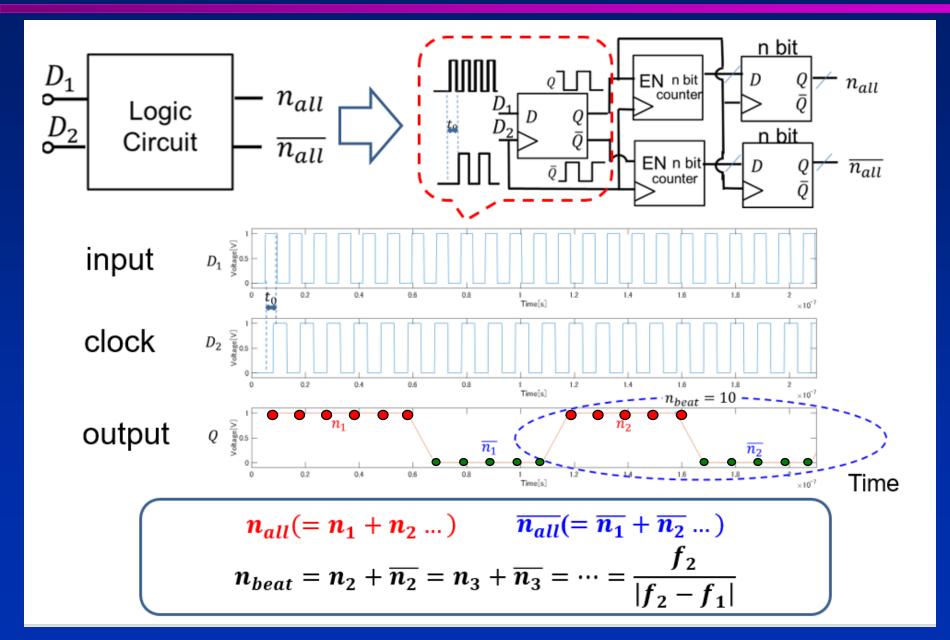

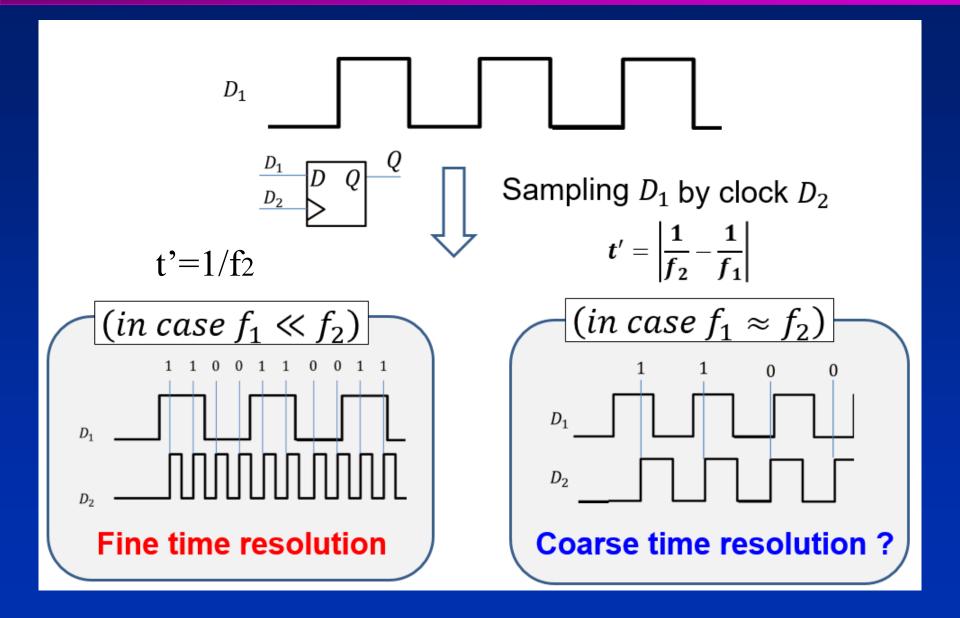

# D1 Sampling by D2

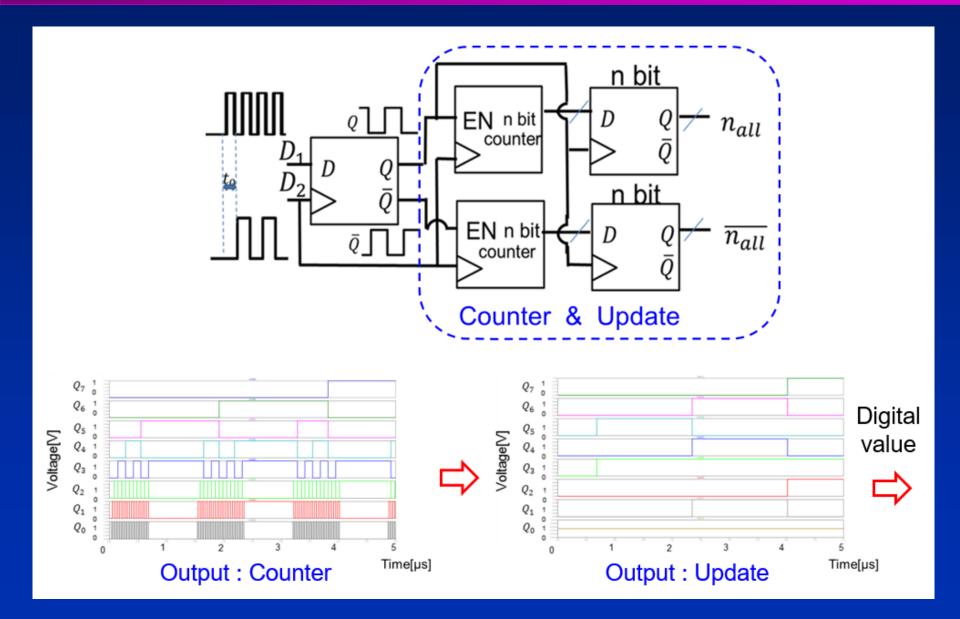

## **Counter & Update**

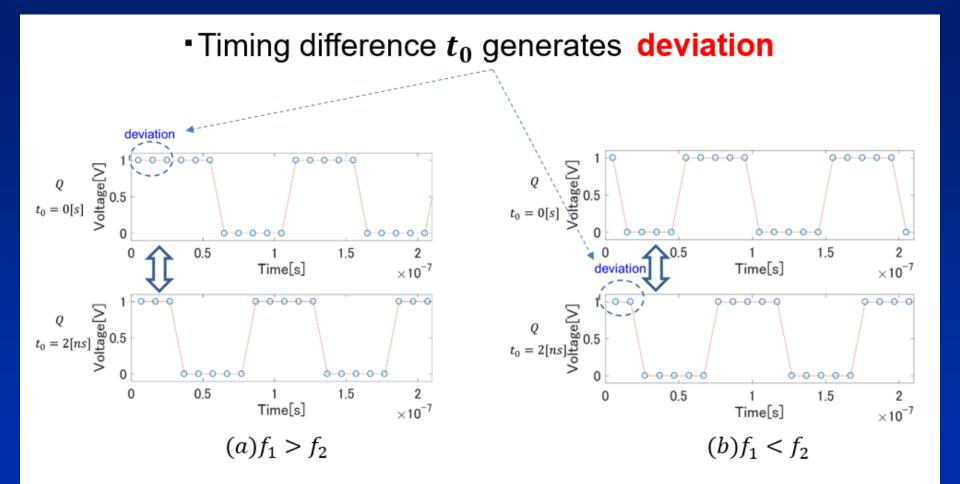

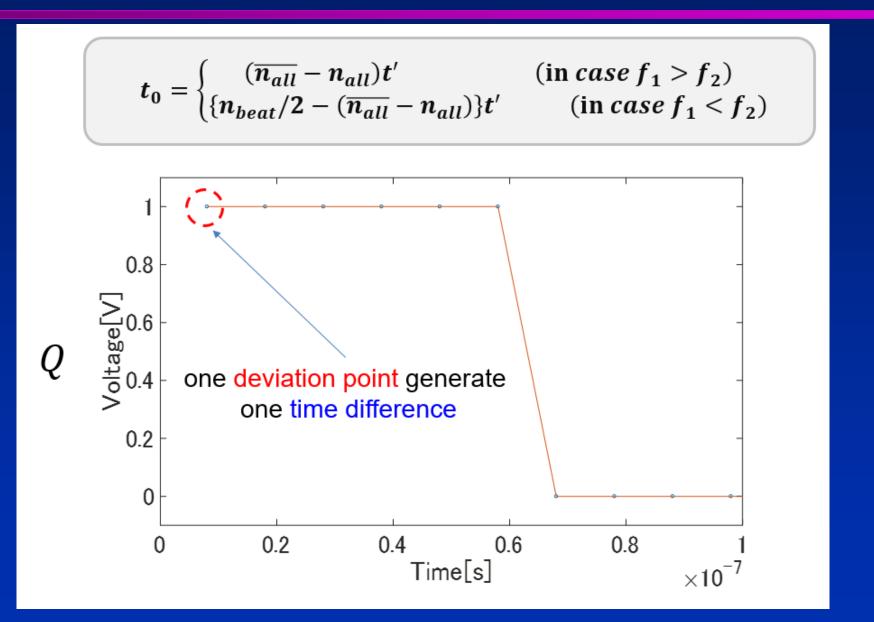

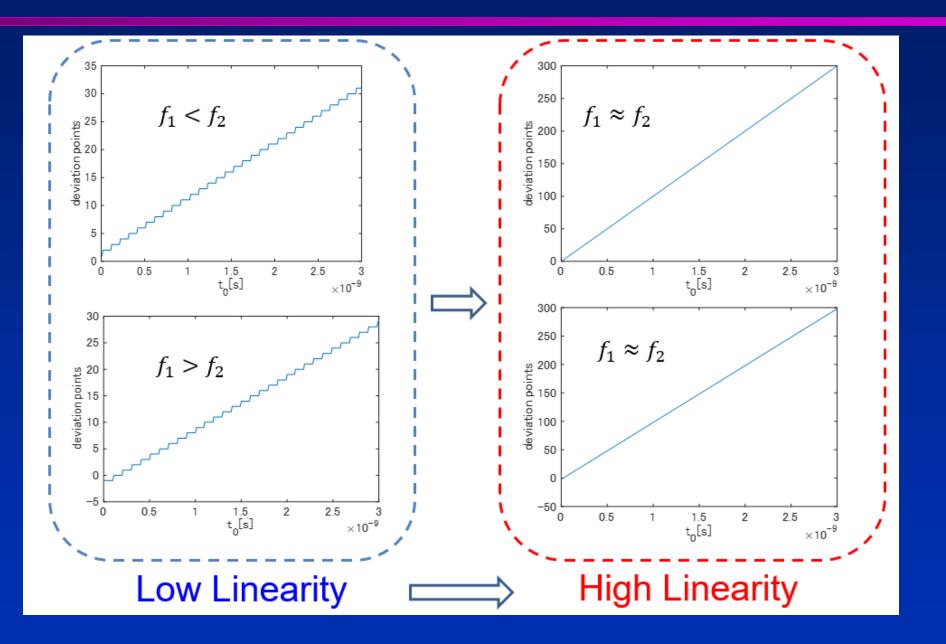

# **Deviation Points by Time Difference** <sup>30/48</sup>

## **Deviation and Time Resolution**

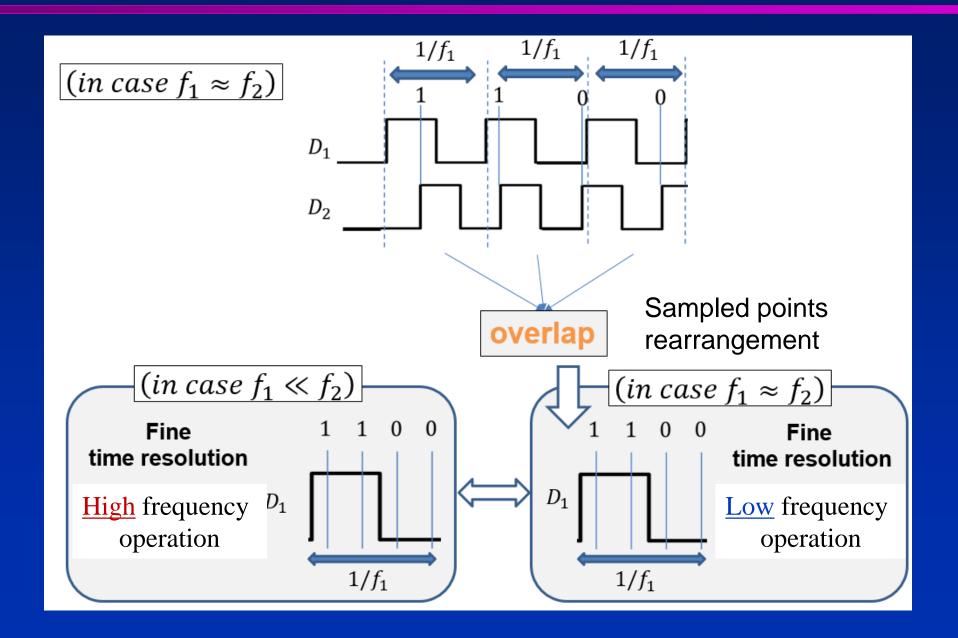

# **Equivalent Time Sampling**

## **Waveform Reconstruction**

## **Measurement Time Resolution**

#### **After overlap** (*in case* $f_1 \approx f_2$ )

# **Proposed TDC Linearity**

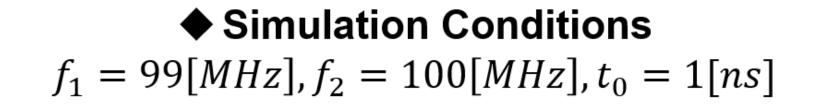

# **Simulation Verification of Proposed TDC** <sup>36/48</sup>

#### Outline

Research Background

Measurement Principle

Analog Centric TDC

<u>Digital Centric TDC</u>

Discussion & Conclusion

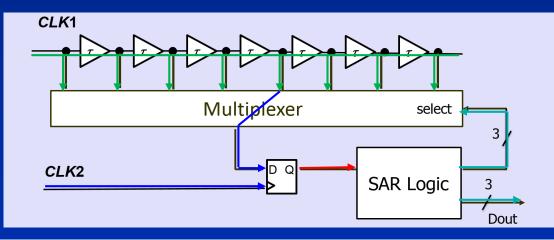

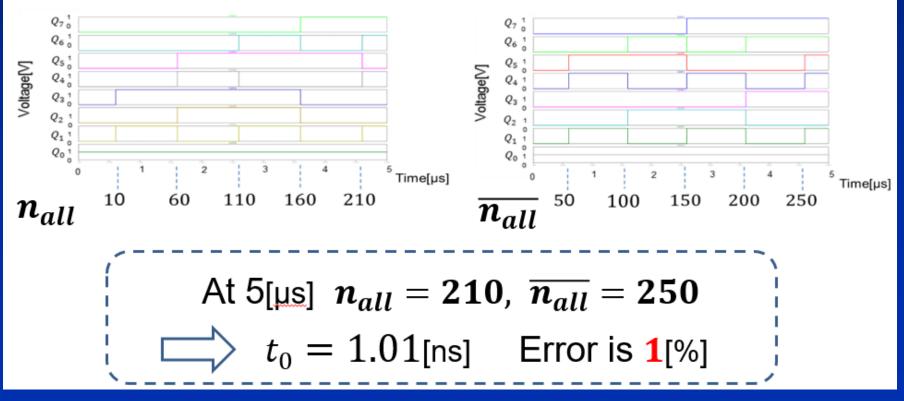

#### **Ring Oscillator with Start**

### **Digital Centric TDC**

#### **Ring oscillator frequencies**

- $f_1 \doteq \text{Counter 1 output N1 / reference time Tref}$

- $f_2 \doteq$  Counter 2 output N2 / reference time Tref

#### Outline

Research Background

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

# **TDC Architecture Comparison**

Good

Bad

41/48

Excellent

# **Comparison of Time and Voltage**

- Dynamic range of time domain signal can be infinite.

- Time flows in one direction.

- Ring oscillator can be often used for time domain signal processing.

- Exact frequency division is possible, whereas exact voltage division is difficult.

- Frequency is a stable signal.

- Jitter is a difficult problem.

- Time as well as voltage can be held.

- Time as well as voltage can be amplified.

- New TDC architectures can be inspired by existing ADC architectures.

#### Conclusion

Verner Oscillator TDC architectures - Analog centric and digital centric ones - Using two oscillators with different frequencies Can be shared among multi-channel TDCs - No delay line - No self-calibration required - Design tradeoff Measurement time **Time resolution** Input time range

#### **Time is very important !**

# 光阴似箭

# Effective executives know that time is the limiting factor of the other resources.

Peter Drucker

# **Appendix : N-Stage Trigger Circuit**

S. Sakurai, H. Kobayashi, et. al., "Study OF Multi-Stage Oscilloscope Trigger Circuit," IEEE ISPACS, Xiamen, (Nov. 2017)

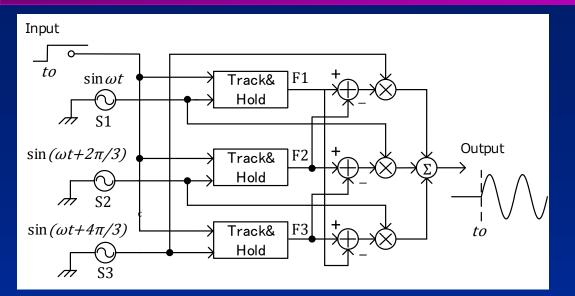

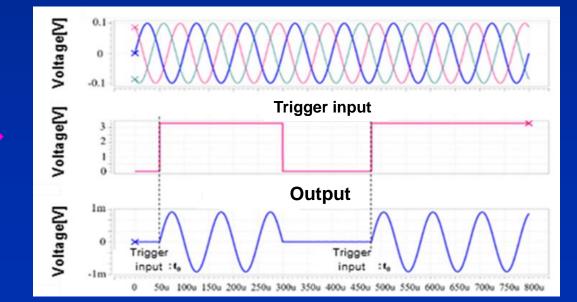

### **Three-stage Trigger Circuit**

#### Analysis of Three-stage Trigger Circuit

Signal source

Source

$$S_1 = \sin \omega t$$

,  $S_2 = \sin \left( \omega t + \frac{2\pi}{3} \right)$ ,  $S_3 = \sin \left( \omega t + \frac{4\pi}{3} \right)$

47/48

Triggered T/H circuit output

$$F_1 = \sin \omega t_0$$

,  $F_2 = \sin \left( \omega t_0 + \frac{2\pi}{3} \right)$ ,  $F_3 = \sin \left( \omega t_0 + \frac{4\pi}{3} \right)$

Track mode

$$Vo_{track} = S_1(S_2 - S_3) + S_2(S_3 - S_1) + S_3(S_1 - S_2)$$

Hold mode

$$Vo_{hold} = S_1(F_2 - F_3) + S_2(F_3 - F_1) + S_3(F_1 - F_2)$$

$$= \frac{3\sqrt{3}}{2}\sin(\omega(t - t_0))$$

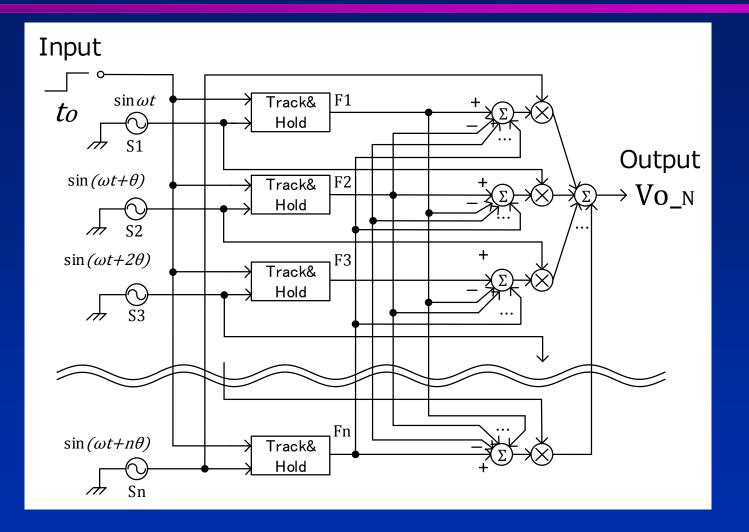

## **N-Stage Trigger Circuit**

Trigger circuit is a key ! Trigger circuit for TDC