# 逐次比較型 TDC の単発信号測定技術の検討

# 小澤祐喜, 姜日晨, 小林春夫

群馬大学 理工学府電子情報部門 〒376-8515 群馬県桐生市天神町 1-5-1

Research on a successive approximation register time-to-digital converter architecture for one shot timing measurement

Yuki Ozawa Conbing Li Haruo Kobayashi

Division of Electronics and Informatics, Graduate School of Science and Technology, Gunma University

#### Abstract

This paper describes a successive approximation register (SAR) time-to-digital converter (TDC) architecture capable of measuring the timing difference between two single-shot signals with full digital FPGA. The SAR TDC is suitable for multi-channel timing built-out self-test (BOST) implementation on an FPGA chip. In order to reduce the number of buffers and DFFs in a conventional Flash TDC or Vernier TDC, the SAR architecture is applied. However, the SAR TDC can measure only the repetitive clock timing, and it cannot measure the single-shot timing signal directly. So first we employ trigger circuits in front of the SAR TDC to measure the single-shot timing, but the trigger circuits include some analog circuits so that its digital FPGA implementation is difficult. Then we present here an SAR-TDC architecture that enables the single-shot timing using ring oscillators, which leads to its full digital FPGA implementation.

キーワード:時間デジタイザ回路,逐次比較,リング発振器,SPICE 回路シミュレーション (Time-to-Digital Converter, Successive-Approximation-Register, Ring Oscillator, SPICE Circuit Simulation)

#### 1.はじめに

近年では半導体の価格は下がる一方であるが、特にアナログ回路部のテストコストは増加傾向にある。また、人命に直結する車載システムへの採用も急速に増加しているためテスト品質の要求も高くなっている。

TDC (Time-to-Digital Converter )は2つのタイミング信号のエッジ間の時間差を測定しデジタル出力を得る回路である[1]-[10]. 微細化が進むにつれ電圧軸での分解能の維持が難しくなっていくが、逆に TDC は微細化によって分解能を向上出来る. TDC はメモリなどの半導体試験装置でのタイミングテストに多用されており、高性能化によってテストコストの削減とテスト品質の向上が可能である. 数ある方式の中でも逐次比較(Successive-Approximation-Register: SAR)型 TDC は他の方式と比べ回路規模が小さく全デジタル構成可能(よって FPGA 実装向き)という利点を持つ[4]. しかし非測定信号が繰り返し信号でなければ測定出来ないためアプリケーションが限定的であった.

本論文では先に提案した, SAR型TDCを単発信号でも測定可能とした回路に対して,シミュレーションによって動作を検証したので報告する.

#### 2.SAR型TDCの構成と動作

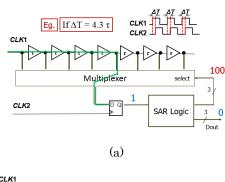

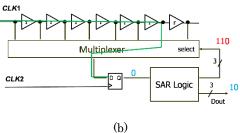

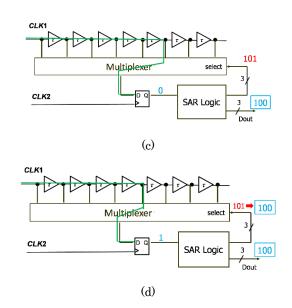

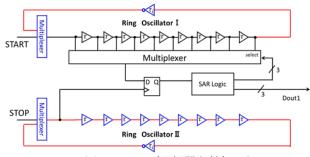

逐次比較型 TDC の構成と動作を図 1 に示す. SAR 型 TDC は CLK1 と CLK2 の時間差の測定を逐次比較の原理でn回に分けて2 進探索することにより行い,デジタル出力する回路である.

分解能ビット数 n が大きい場合の SAR 型 TDC の基本的

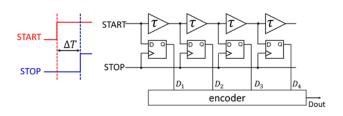

なフラッシュ型 TDC (図 2) に対する得失は次のようになる. - 必要な D フリップフロップ数が激減(よって消費電力も激減する). 即ち(  $2^n-1$ )個からコンパレータと SAR Logic に使う 1+2(n+1)個に大幅減少 .

- 遅延バッファ数は同じ.

- マルチプレクサと SAR Logic は Dフリップフロップ配列に比べ比較的小規模回路

- フラッシュ型は 1回で測定, SAR 型はn回のステップで測定

- フラッシュ型は単発のタイミング信号間測定可 SAR 型は繰り返しタイミング信号のみ測定可

図 1 SAR 型 TDC の構成と動作(a)~(d)

Fig. 1. Example of an SAR TDC in operation (a)~(d)

図 2 フラッシュ型 TDC の構成

Fig. 2. Configuration of a Flash TDC

つまり、SAR型TDCはフラッシュ型TDCに比べてはるかに少ないDフリップフロップ数で同じ機能を果たすことができる[11].しかし、SARロジックは複数回で作動する構造で測定できるタイミング信号が「繰り返し信号」であることに制限されることになる。「電圧」であればキャパシタに保存しておくことが出来るが、単発信号の「時間差」は原理的に保存出来ないと考えられてきたため、従来型のSAR型TDCは繰り返し信号でしか用いることが出来なかった。

## 3.リング発振器を用いた SAR TDC

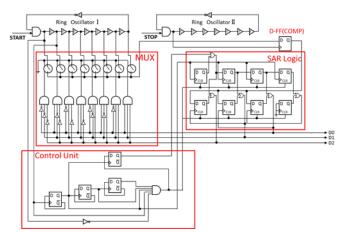

リング発振器を付加した SAR 型 TDC の構成を図 3 に示す. SAR 型 TDC の START 信号と STOP 信号の入力部分にリング発振器を付加した. 従来であれば入力信号 (被測定信号)が「繰り返し信号」である必要があったが,提案回路は単発信号を入力された後,自動的に発振することを利用している. また,元々の SAR 型 TDC にリング発振器を付加したため,全デジタル構成可能で設計ができ,FPGA 実装に適している. 提案回路は,元々の SAR 型 TDC の利点を失うことなく機能を拡張出来る.

図 3. リング発振器を付加した SAR 型 TDC のブロック図

Fig. 3. Proposed digital centric SAR TDC with two ring oscillators

### 3.1.リング発振器の動作

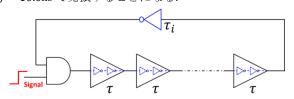

SAR型 TDC に組み込まれているリング発振器は奇数個のインバータで構成されている。遅延素子は偶数個のインバータから成る。図 4.に示すように 1 つの遅延素子の遅延時間は $\tau$ であり、インバータと AND ゲートとの合計の遅延時間は $\tau_i$ である。入力が 0 から 1 に立ち上がると、次の式 1.1 のように表される周期的な時間 $T_{RO}$ で発振を開始する。

$$T_{RO} = 2(n\tau + \tau_i) \tag{1.1}$$

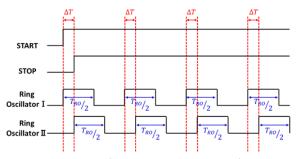

図 5 は 2 つのリング発振器を用いた場合のタイミングチャートである. START 信号と STOP 信号の時間差 $\Delta$ Tが0 <  $\Delta$ T  $\leq \frac{T_{RO}}{2}$ であれば、時間差を保ちながら発振させることが出来る. 例えば 3 ビットの場合では SAR 型 TDC は 7 つの遅延素子と、1 つのインバータを持つため、 $\frac{T_{RO}}{2}$  =  $7\tau + \tau_i$ となる. ここで、もし $\tau$  = 1.0ns, $\tau_i$  = 3.0ns であるなら、分解能は 1.0ns であり、リング発振器は発振周期 $T_{RO}$  =  $2(7 \cdot 1.0 + 3.0)$  = 10.0ns で発振することになる.

図 4. リング発振器の構成

Fig.4. Ring oscillator with an oscillation start signal.

図 5. リング発振器の動作クロック波形

Fig.5. Timing chart of ring oscillators

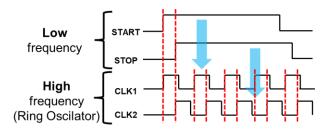

### 3.2.被測定信号が低周波の場合

被測定信号がリング発振器の発振周波数より十分低いクロック周波数であった場合を考えてみる(図 6). 例えば,10ビットの SAR型 TDCに 1kHzのクロックが入力されたとする. この時, 測定に必要な時間は 1ms×10=10ms となり, 被測定信号が低周波数であると測定時間がかかってしまうことになる.

前述のように元々リング発振器を付加した SAR 型 TDC は単発信号を測定する目的で設計した. しかし, 低周波数の被測定信号の場合でも, 測定時間はリング発振器の発振周波数にのみ依存するので被測定信号が低周波数であったとしても測定時間に影響しないメリットを持つ.

図 6. 被測定信号が低周波数の時の入出力波形 Fig.6. Low-frequency repetitive clock timing measurement

# 4.シミュレーションによる検証

図3の提案回路を素子単位で設計した回路を図7に示す. 3 ビットで設計したため、フラッシュ型と比べると回路規模の差は小さいが、実際にはより高ビットでの利用を想定している.シミュレーション条件を下記に示す.

- ▶ シミュレーションソフト:SPICE

- ▶ 分解能:3-bit,8-level▶ 入力時間差:0-8.0ns

- バッファ遅延値(リング発振器)τ:1.0ns

- インバータ遅延値(リング発振器)τ<sub>i</sub>:1.0ns

図 7.リング発振器を付加した SAR 型 TDC のシミュレーション回路

Fig.7. Simulated SAR TDC circuit with two ring oscillators

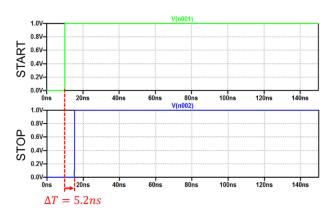

例として $\Delta T = 5.2$ ns の時間差を持った単発信号を入力し、各部位の信号が設計通りであるか評価する。図 7 に入力した START 信号、STOP 信号を示す.

図 8. SAR 型 TDC へ入力する単発信号 Fig.8. Single-shot input signals

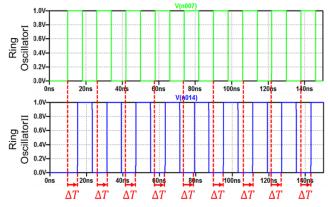

図 9 は入力された START 信号と STOP 信号の時間差  $\Delta T = 5.2 ns$  を保持しながら発振しているリング発振器の波形である. これにより、従来ではできなかった SAR 型 TDC による単発信号の測定が可能となる.

図 9. リング発振器の出力クロック波形

Fig.9. Simulated ring oscillator waveforms

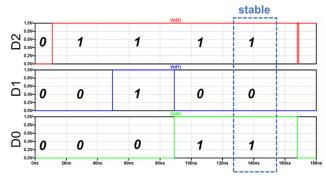

図 10 に SAR 型 TDC の出力波形を示す. 逐次比較の原理に基づき,3 ビットであるので「100:4」  $\rightarrow$  「110:6」  $\rightarrow$  「101:5」と推移している. 結果として START 信号と STOP 信号の時間差 $\Delta T = 5.2$ nsを入力して得られた出力は「101:5」、つまり5.0ns  $\leq \Delta T < 6.0$ nsである. SPICE シミュレーションによる評価により、一連の流れにおいて各部が設計通りに動作したことが確認出来た.

図 10. リング発振器を付加した SAR 型 TDC の出力波形 Fig.10. SAR TDC digital output (Dout)

次に START 信号と STOP 信号の時間差 $\Delta T$  を 0.0ns から 7.8ns まで変化させて入出力の線形性を確認した結果を図 11 に示す. 原理的に量子化誤差は存在するが, 設計通りの動作をシミュレーションによって確認できた.

図 11. リング発振器を付加した SAR 型 TDC の入出力線形性

Fig.11. SPICE simulation results of 3-bit digital centric SAR TDC input-output characteristics

#### 5.まとめ

本論文では比較的小さい回路規模で全デジタル構成可能な SAR型 TDC で単発信号を測定可能とする回路を示し、シミュレーションで動作を検証した。従来では、電圧はキャパシタのような素子に保存しておくことが出来るが、時間差は原理的に保存出来ないと考えられていた。しかし、2つのリング発振器を用いることで単発信号から繰り返し信号の生成を可能としたことで、単発信号でも SAR型 TDC で測定可能となった。今まで限定的であった SAR型 TDC のアプリケーションが飛躍的に広がると期待できる。

今後の課題は FPGA 実装により実際の測定器で評価を行うことや、リング発振器間の発振周波数のミスマッチを補正する方法を開発することである.

- [1] Y. Arai, T. Baba, "A CMOS Time to Digital Converter VLSI for High-Energy Physics", IEEE Symposium on VLSI Circuits (1988).

- [2] J. Lee and Y. Moon: "A Design of Vernier Coarse-Fine Timeto-Digital Converter Using Single Time Amplifier", J. of Semiconductor Technology and Science, vol.12, no. 4 (Dec. 2012)

- [3] G. S. Jovanovi'c, M. K. Stoj'cev: "Vernier's Delay Line Timeto-Digital Converter", Scientific Publications of the State University of Novi Pazar, Ser. A: Appl. Math Inform. and Mech (2009)

- [4] K. H. Prasad, V. B. Chandratre, P.Saxena, C. K. Pithawa: "FPGA based Time-to-Digital Converter", DAE Symp. on Nucl. Phys. (2011).

- [5] T. Chujo, D. Hirabayashi, K. Kentaroh, C. Li, Y. Kobayashi, J. Wang, K. Sato, H. Kobayashi, "Experimental Verification of Timing Measurement Circuit With Self-Calibration", IEEE International Mixed-Signals, Sensors and Systems Test Workshop, Porto Alegre, Brazil (Sept. 2014).

- [6] C. Li, H. Kobayashi, "A Gray Code Based Time-to-Digital Converter Architecture and its FPGA Implementation", IEEE International Symp. on Radio-Frequency Integration Technology, Sendai (Aug. 2015).

- [7] C. Li, J. Wang, H. Kobayashi, R. Shiota, "Timing Measurement BOST Architecture with Full Digital Circuit and Self-Calibration Using Characteristics Variation Positively for Fine Time Resolution", IEEE International Mixed-Signal Testing Workshop, Catalunya, Spain (July 2016)

- [8] S. Ito, S. Nishimura, H. Kobayashi, et al., "Stochastic TDC Architecture with Self-Calibration," IEEE Asia Pacific Conf. Circuits and Systems, Kuala Lumpur, Malaysia (Dec. 2010).

- [9] Y. Ozawa, T. Ida, R. Jiang, S. Sakurai, S. Takigami, et. al., "SAR TDC Architecture With Self-Calibration Employing Trigger Circuit" The 26th IEEE Asian Test Symposium, Taipei, Taiwan (Nov. 2017)

- [10] Y. Ozawa, T. Ida, S. Sakurai, R. Jiang, et al., "SAR TDC Architecture for One-Shot Timing Measurement", IEEE International Symposium on Intelligent Signal Processing and Communication Systems, Xiamen, China (Nov. 2017).

- [11] R. Jiang, C. Li, M. Yang, H. Kobayashi, et al., "Successive Approximation Time-to-Digital Converter with Vernier-level Resolution", IEEE IMSTW, Catalunyna, Spain (July 2016)