# 温度不感MOS定電流源回路とそのスタートアップ回路

Isam Ebisawa Kuswan\*, 山本 颯馬, 阿部 優大, 井田 貴士, 柴崎 有祈子, 築地 伸和 桑名 杏奈, 小林 春夫 (群馬大学)

鈴木 彰, 轟 祐吉, 柿木 利彦, 小野 信任, 三浦 一広 (ジーダット (株))

Temperature-Insensitive MOS Reference Current Source and its Startup Circuit

Isam Ebisawa Kuswan\*, Souma Yamamoto, Yudai Abe, Takashi Ida, Yukiko Shibasaki, Nobukazu Tsukiji,

Anna Kuwana, Haruo Kobayashi (Gunma University)

Akira Suzuki, Yukichi Todoroki, Toshihiko Kakinoki, Nobuto Ono, Kazuhiro Miura (JEDAT)

キーワード:基準定電流源、CMOS アナログ回路、温度特性、スタートアップ回路

(Reference Current Source, CMOS Analog Circuit, Temperature Characteristic, Startup Circuit)

#### 1. はじめに

現在, IoT が急速に進展する中で、電子機器の需要は増加しており、電子製品に対する信頼性の要求レベルが高まっている。電子回路における信頼性の問題は主に PVT (プロセス・電源電圧変動・温度) ばらつきによって生じる。本論文では、PVT ばらつきにおける温度に焦点をあて、筆者らが提案した温度に依存しない MOS 基準電流源回路の動作と、その回路の動作を保証するスタートアップ回路を紹介する。

基準電流源は電子回路に対し常に一定の電流を出力するものであり、アナログ集積回路において重要な役割を果たす.一般的な基準電流源回路には、所望の基準電流が流れる状態で安定となる正常動作点と、電流が流れない状態で安定となる誤動作点が存在する。そこで、誤動作点を消滅させるためにスタートアップ回路が用いられる.

## 2. 温度に依存しない MOS 定電流源のコンセプト

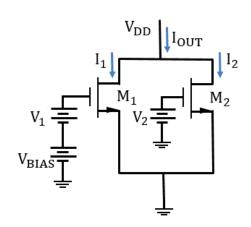

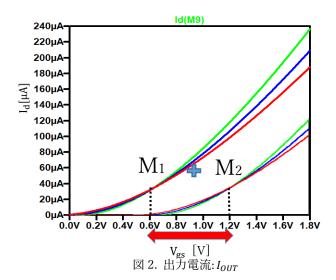

MOS FET には電流電圧特性( $I_D - V_{GS}$ 特性)で温度特性を持たないポイント( $V_p$ )が存在する。また温度特性を持たないポイント( $V_p$ )に対してゲート電圧が低電圧側では低温時と比較し高温時にドレイン電流が多く流れ,一方,高電圧では低温時にドレイン電流が多く流れる。これを基に図 1 に提案する MOS 定電流源のコンセプトを示す。回路構成としては各 MOS のゲートに異なるバイアス電圧を与えるこ

とで、MOS FET の電流の立ち上がり位置を変化させ全体として出力電流の温度依存性をキャンセルする。図 1 のように、 $M_1$ にバイアス電圧 $V_{BIAS}$ を印加し、表 1 の条件で SPICE シミュレーションすると、図 2 の出力電流(:  $I_{OUT}$ )を得る。 $I_1$ の出力電流( $I_D - V_{GS}$ 特性)が M1 となり、 $I_2$ の出力電流 ( $I_D - V_{GS}$ 特性)が M2 となる。図 2 における点線で表される $V_P$ を境に低電圧側と高電圧側で温度によるドレイン電流の優位性が反転することを利用し、赤の矢印で示した範囲で 2 つのドレイン電流の和 Iout の温度依存性をキャンセルすることができる。

図1 提案基準電流源回路のコンセプト

Fig. 1. Concept of proposed reference current source circuit.

### 表1 シミュレーション条件

Table 1. Simulation conditions.

| Parameter                       | Value                         |  |

|---------------------------------|-------------------------------|--|

| V <sub>1</sub> , V <sub>2</sub> | 0.0 ~ 1.8 V                   |  |

|                                 | $(V_1$ には $0.6[V]$ のバイアスをかけてあ |  |

|                                 | る. よって実際V1に印加されている電           |  |

|                                 | 圧は 0.6~2.4[V]である)             |  |

| $V_{DD}$                        | 5.0 V                         |  |

| M <sub>1</sub> , M <sub>2</sub> | W=5 [μm], L=2.0[μm]           |  |

Fig.2. Output c urrent: I<sub>OUT</sub>

図 1 の回路において $V_1$ ,  $V_2$ ,  $V_{BIAS}$ も温度不感のバイアス電圧を生成しなければならない. このために $I_{OUT}$ を PMOS で折り返し,抵抗に流して  $V_1$ ,  $V_2$ ,  $V_{BIAS}$ を生成する自己バイアス生成回路を用いる. このために次の 2 つを考慮する必要がある. 本論文では A を検討した.

- A) スタートアップ回路

- B) フィードバック構成での安定性の確保

## 3. カスコード接続を用いた温度不感型 MOS 定電流源

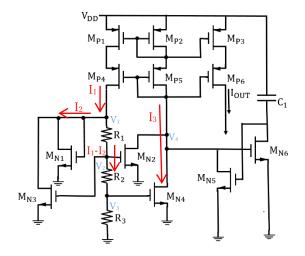

この節では実際に提案した回路を構成し、シミュレーションによる検証を行った。なお、シミュレーションソフトには LTSPICE XVII を用いた。半導体素子はオンセミコンダクタ $0.25\mu m$ プロセスを使用している。 $^{60}$ 図  $^{3}$  が PMOS のカスコード接続を行った提案回路である。カスコード接続を行うことでチャネル調変調効果を抑える構成である。

図3カスコード接続を用いた温度不感型 MOS 定電流源

Fig. 3. Temperature insensitive MOS constant current source using cascode configuration.

図 3 の回路は $M_{N3}$ と $M_{N4}$ が基準 MOS として, $M_{N1}$ と $M_{N2}$  が温度特性校正 MOS となっている.また,抵抗で MOS に かかるゲート電圧を分圧することによって基準 MOS と温度特性校正 MOS に与える電圧を設定することができる.また,この回路は初期状態であると安定状態であるため,スタートアップ回路を用いて回路を動作領域に導く必要がある.図 3 における  $C_1$ ,  $M_{N5}$ と $M_{N6}$ がスタートアップ回路としての役割を持つ.

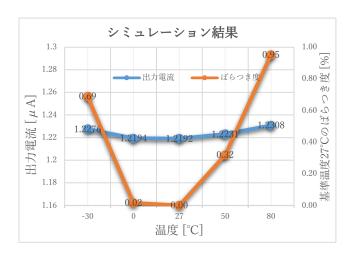

図3の提案回路で、表2の条件でのシミュレーションを 行い、27℃を基準としたときの出力電流と各温度における バラツキ度を図4に示す.

表 2 シミュレーション条件

Table 2. Simulation conditions.

| Parameter            | Value              | Param.   | Value       |

|----------------------|--------------------|----------|-------------|

| $M_{P1} \sim M_{P6}$ | W=800 um, L=2.0 um | $R_1$    | 5000 Ω      |

| $M_{N1}, M_{N3}$     | W=0.1 um, L=2.0 um | $R_2$    | 1610 Ω      |

| $M_{ m N4}$          | W=20 um, L=2.0 um  | $R_3$    | 1500 Ω      |

| $M_{N2}$             | W=200 um, L=2.0 um | $C_1$    | 1 <i>pF</i> |

| $M_{N5}$             | W=4 um, L=2.0 um   | $V_{DD}$ | 5.0 V       |

| $M_{N6}$             | W=0.1 um, L=2.0 um |          |             |

図 4 提案回路の出力電流 I<sub>OUT</sub> と温度によるばらつき度 Fig. 4. Output current I<sub>OUT</sub> and its variation due to temperature in the proposed circuit.

図 4 より、-30℃~80℃の温度において、バラツキを 1%未満で電流を出力することができる。また、バラツキ度は基準温度 27℃時に各ゲート電圧に対して流れる電流と各温度での電流の絶対差であり次式で定義する。

バラツキ度 =

$$\left| \frac{I_{OUT(27^{\circ}\mathbb{C})} - I_{OUT(比較温度)}}{I_{OUT(27^{\circ}\mathbb{C})}} \right| * 100[\%]$$

(1)

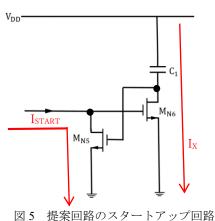

## 4. スタートアップ回路

CMOS のアナログ回路では、基準電流を必要とすることが多い。そこで、誤動作点を消滅させるためにスタートアップ回路が用いられる。図 5 のスタートアップ回路はNMOS トランジスタ  $M_{N5}$ , $M_{N6}$ ,とコンデンサー $C_1$  から構成されている。これらのサイズ比や容量は表 2 に記載した。

凶3 1定条凹鉛のヘクートノック凹鉛

Fig. 5. Startup circuit for the proposed circuit.

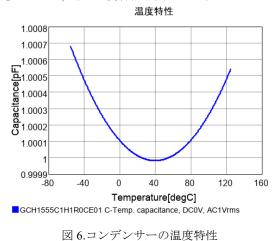

このとき、回路の寄生容量を考慮すると、コンデンサー $C_1$  の値  $0.5\sim1.0[pF]$ のとき、 $M_{NS}$ のゲート電圧 $VG_{(MNS)}\cong V_{dd}$  となる.また、使用しているシミュレーションソフト LTSPICE XVII に標準搭載されているコンデンサーでは、コンデンサーの耐熱性により-30°C $\sim80$ °Cまでのシミュレーションができない.そのため、今回のシミュレーションでは村田製作所の GCH1555C1H1R0CE01 のコンデンサーモデルを利用した.(9このコンデンサーは-55°C $\sim125$ °Cまで対応しており、その温度特性を図 6 に示す.

Fig. 6. Temperature characteristic of capacitor.

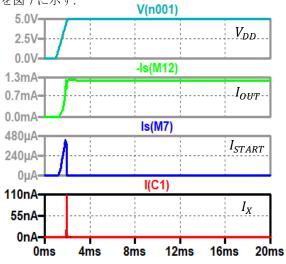

また、図 4 では図 3 の回路の温度における出力電流を確認した。この節では 20ms で transient 解析を行い、出力電流とスタートアップ回路のスタートアップ電流  $I_{START}$  と動作電流  $I_{X}$  を図 7 に示す。

図 7. 図 3 の回路の過渡解析 Fig. 7. Transient Analysis of the circuit in Fig.3.

今回のスタートアップ回路はコンデンサーを用いることで、電源が定常状態の 5V に達したときコンデンサーには電流が流れない.よって、コア電流源回路の通常回路動作後にはスタートアップ回路の動作が止まり、スタートアップ回路の定電流源・動作電流が流れない.また、従来のMOS FET を利用したスタートアップ回路とは違い、消費電力を大きく抑えることができる.

#### 5. まとめ

本論文では、温度不感型 MOS 定電流源回路とそのスタートアップ回路について述べた。スタートアップ部に コンデンサーを用いることで、コア電流源回路が通常動作し定電流出力の動作した後、スタートアップ回路は動作電流ゼロの状態にすることを可能とした。

#### 文 献

- (1) K Ueno, T. Hirose, T. Asai, Y. Amemiya, "CMOS Voltage Reference Based on Threshold Voltage of a MOSFET", *International Conference on Solid-State Devices and Materials*, Tsukuba (2007).

- (2) C. Yoo, J. Park "CMOS Current Reference with Supply and Temperature Compensation", *Electronics Letters*, vol. 43, no.25, pp.1422-1424 (Dec. 2007).

- (3) H. Ikeda, K. Takakubo, H. Takakubo, "Drain Current Zero-Temperature-Coefficient Point for CMOS Temperature Voltage Converter Operating in Strong Inversion", *IEICE Trans. Fundamentals*, Vol. E87-A, No. 2, pp.370-275 (Feb. 2004).

- (4) T. Kajita, Startup Circuit U.S. Patent No. 9,960,762

- (5) T. Ida, "High Performance Time-to-Digital Converter and Temperature Insensitive MOS Constant Current Source", Gunma University, 2018, Master's Thesis.

- (6) ON Semiconductor 0.25µm BCD process technology (https://www.onsemi.jp/PowerSolutions/content.do?id=16683)

- (7) R. J. Baker, CMOS Circuit Design, Layout, and Simulation, Third Edition, (http://cmosedu.com/cmos1/cmosedu\_models.txt)

- (8) Q.A.Khan, S.K.Wadhwa, K.Misri,"Low Power Startup Circuit for Voltage and Current Reference with Zero Stady State Current", International Symposium on Low Power Electronics and Design,

Seoul (2003).

(9) 村田製作所 コンデンサーGCH1555C1H1R0CE01(https://psearch.jp.murata.com/capacitor/product/GCH1555C1H1 R0CE01%23.html)