# 整数論に基づくデジタル・アナログ変換器アーキテクチャ

杜 遠洋, 白 雪妍, 桑名杏奈, 小林春夫(群馬大)久保和良(小山高専)

概要:この論文では整数論に基づくデジタル・アナログ変換器(Digital-to-Analog Converter: DAC)の次の新構成を検討したので報告する. (i) N 角数に基づき, N 個の電流源, N 角数重み付け抵抗ネットワーク,スイッチ配列,デコーダから成る DAC(N=3,4,5,…). (ii) ゴールドバッハ予想に基づき,2 個の電流源,素数重み付け抵抗ネットワーク,スイッチ配列,デコーダからなる DAC. シミュレーションで原理・動作を確認した.

#### キーワード: 整数論, 多角数, 素数, DA 変換器

(Number Theory, Polygonal Number, Prime Number, Digital-to-Analog Converter)

#### 1. 研究背景•目的

DAC はデジタル信号をアナログ信号に変換する回路で、通信機器、電子計測器、オーデオ等で幅広く使用されている。その回路はその名の通りデジタル回路とアナログ回路から構成される。一方整数には面白い性質がたくさんある。それに基づきDAC の新しい構成を検討したので報告する。

### 2. 3 角数 DAC

# <2.1>3 角数とは

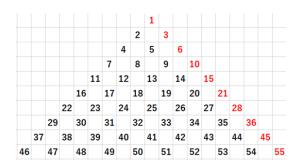

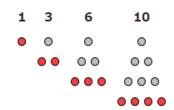

3 角数とは正 3 角形の形に点を並べたときにそこに並ぶ点の総数である(図1の赤数字).

# <2.2>3 角数定理

自然数は高々3つの3角数の和で表せる(図2).

#### <2.3>3 角数を用いた DAC の構成

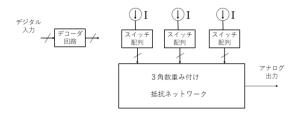

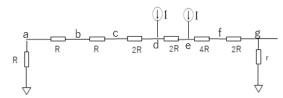

3角数定理による3角数DACを提案する(図3). この3角数DACは,3つ電流源,3角数重み付け抵抗ネットワーク(図4,5),スイッチ配列,デコーダ回路から成る.電流源Iの3角数重み付け抵抗ネットワークに接続されるノードにより,ノード eに3角数重み付け電圧が出力される.重ね合わせの原理と3角数の原理により,任意の整数重み付け電圧がノード eに出力できる.

図1 3角数

| 1:  | 1      | 16: | 1+15    |

|-----|--------|-----|---------|

| 2:  | 1+1    | 17: | 1+1+15  |

| 3:  | 3      | 18: | 3+15    |

| 4:  | 1+3    | 19: | 1+3+15  |

| 5:  | 1+1+3  | 20: | 10+10   |

| 6:  | 6      | 21: | 21      |

| 7:  | 1+6    | 22: | 1+21    |

| 8:  | 1+1+6  | 23: | 1+1+21  |

| 9:  | 3+6    | 24: | 3+21    |

| 10: | 10     | 25: | 10+15   |

| 11: | 1+10   | 26: | 1+10+15 |

| 12: | 1+1+10 | 27: | 1+10+21 |

| 13: | 3+10   | 28: | 28      |

| 14: | 1+3+10 | 29: | 1+28    |

| 15: | 15     | 30: | 1+1+28  |

|     |        |     |         |

図2 3角数定理

図3 3角数を用いた DA 変換器の構成

# <2.4>3 角数 DAC 動作

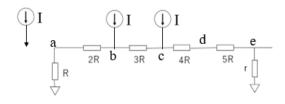

例えば、デジタル入力が9の場合、電流源Iをノードb, c に接続することでアナログ出力(ノードe電圧)が (3+6)Vo=9 Vo を得る(図4).

図4 デジタル入力が9の場合

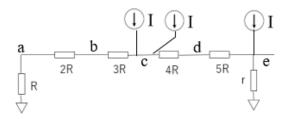

デジタル入力が 27 の場合, 2 つの電流源 I を ノード c に接続し, もう一つのノード電流源 I を ノード e に接続するとアナログ出力が

(6+6+15) Vo=27Vo となる (図 5).

図5 デジタル入力が27の場合

# 3. 多角数 DAC

3 角数 DAC を一般化し多角数 DAC を提案する.

# <3.1> 多角数とは

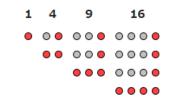

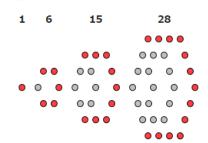

多角数とは、正多角形の形に点を並べたときにそこに含まれる点の総数の自然数である.3 角数,4 角数,6 角数の説明をそれぞれ図 6,7,8 に示す.

# <3.2>多角数定理

すべての自然数は高々 m 個の m 角数の和である

# <3.3>K 番目の N 角数

K番目のN角数は次式で表せる (N=3,4,5,...).

N角数は1番目から次のようになる.

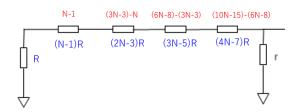

1, N, 3N-3, 6N-8, 10N-15, ···

#### 三角数

図6 3角数の説明

#### 四角数

図7 4角数の説明

#### 六角数

図8 6角数の説明

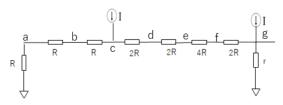

N 角数重み付け抵抗ネットワークを図 9 に提案しする (N=3,4,5,6,...). 重ね合わせの理と多角数定理で任意の整数倍の電圧が出力される. また抵抗が整数値比なので集積化しやすい.

図9 N角数重み付け抵抗ネットワーク

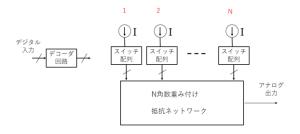

N角数を用いた DAC の構成を図10 に提案する. 提案する N 角数 DAC は, N 個の電流源, スイッチ配

列,N角数重み付け抵抗ネットワーク,デコーダ回路から構成される.

図 10 N角数に基づく DAC の構成

#### 4. 素数 DAC

#### 〈4.1〉素数とは

素数とは、自明な正の因数(1と自分自身)以外に 因数を持たない自然数であり、1でない数である.

素数数列: 2, 3, 5, 7, 11, 13, 17, 19, 23, 29, ......

#### <4.2>ゴールドバッハ予想

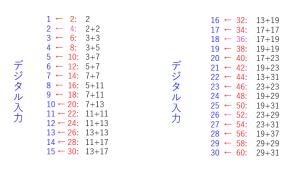

全ての偶数は二つの素数の和で表せる(図11).

| 2:  | 2     | 32: | 13 + 19 |

|-----|-------|-----|---------|

| 4:  | 2+2   | 34: | 17 + 17 |

| 6:  | 3+3   | 36: | 17 + 19 |

| 8:  | 3+5   | 38: | 19+19   |

| 10: | 3+7   | 40: | 17 + 23 |

| 12: | 5+7   | 42: | 19+23   |

| 14: | 7+7   | 44: | 13 + 31 |

| 16: | 5+11  | 46: | 23 + 23 |

| 18: | 7+11  | 48: | 19+29   |

| 20: | 7+13  | 50: | 19 + 31 |

| 22: | 11+11 | 52: | 23 + 29 |

| 24: | 11+13 | 54: | 23 + 31 |

| 26: | 13+13 | 56: | 19 + 37 |

| 28: | 11+17 | 58: | 29+29   |

| 30: | 13+17 | 60: | 29+31   |

|     |       |     |         |

図 11 ゴールドバッハ予想の説明

# <4.3>素数 DA 変換器のデジタル入力との対応

ゴールドバッハ予想は「全ての偶数は二つの素数の和で表せる」であるが、DACのデジタル入力は偶数だけではなく奇数もある. しかし図 12 のように設計すれ全整数に対して対応できる.

図 12 デジタル入力との対応

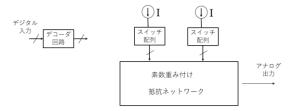

#### <4.4>素数の性質を用いた素数 DAC の構成

ゴールドバッハ予想に基づく素数 DA 変換回路を図 13 に提案する. 提案する素数 DAC は,2 個の電流源,スイッチ配列,素数重み付け抵抗ネットワーク,デコーダ回路から構成される.

図 13 提案する素数 DAC の構成

# <4.5>素数 DA 変換器の動作

例えば、デジタル入力が6の場合、電流源Iを素数 重み付け抵抗ネットワークのノードdに接続し、 もう一つの電流源Iをノードeに接続する。アナロ グ出力(ノードg)電圧が(5+7) Vo=6 (2Vo) にな る (図 14) .

図 14 デジタル入力が 6 の場合

デジタル入力が 8 の場合,電流源 I を素数重み付け抵抗ネットワークのノード c に接続し、もう一

つの電流源 I をノード g に接続する. アナログ出力が (3+13) Vo=8 (2 Vo) となる(図 15).

図15 デジタル入力が8の場合

#### 5. まとめ

角数と素数を用いた新規 DA 変換器回路・アルゴリズムの可能性を検討した. 今度は従来法との得失を検討していく. また整数論を活用したさらなる新構成 DAC を検討していく.

#### 参考文献

- B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw Hill (2016)

- [2] 今野紀雄 「数はふしぎ 読んだら人に話したくなる 数の神秘」サイエンス・アイ新書 (2018 年)

- [3] 渋谷道雄, LTspice で学ぶ電子回路 第3版 オーム社 (2019年)

- [4] M. Higashino, S. N. B. Mohyar, Y. Dan, Y. Sun, A. Kuwana, H. Kobayashi, "Digital-to-Analog Converter Layout Technique and Unit Cell Sorting Algorithm for Linearity Improvement Based on Magic Square", Journal of Technology and Social Science, vol.4, no.1, pp.22-35 (Jan. 2020).

- [5] Y. Kobayashi, S. Shibuya, T. Arafune, S. Sasaki, H. Kobayashi, "SAR ADC Design Using Golden Ratio Weight Algorithm", International Symposium on Communications and Information Technologies, Nara, Japan (Oct. 2015)

- [6] C. Li, K. Katoh, H. Kobayashi, J. Wang, S. Wu, S. N. Mohyar, "Time-to-Digital Converter Architecture with Residue Arithmetic and its FPGA Implementation",11th International SoC Design Conference, Jeju, Korea (Nov. 2014)

[7] C. Li, H. Kobayashi, "A Glitch-Free Time-to-Digital

- Converter Architecture Based on Gray Code", 電気学会論文誌(和文誌 C), vol. 136, no. 1(2016年1月).

- [8] G. Adhikari, R. Jiang, H. Kobayashi, "Study of Gray Code Input DAC Using MOSFETs for Glitch Reduction", IEEE 13th International Conference on Solid-State and Integrated Circuit Technology, Hangzhou, China (Oct.2016)

- [9] M. Hirato, A. Kuwana, H. Kobayashi, "Analog Signal Generator for Irrational Number Approximation Based on Number Theory", 3<sup>rd</sup> International Conference on Technology and Social Science, Kiryu, Japan (May 2019).

- [10] S. Yamamoto, M. Hirai, T. Arai, A. Kuwana, H. Kobayashi, K. Kubo, "Proposal of Ternary Resistor Network DACs", 5th Taiwan and Japan Conference on Circuits and Systems, Nikko, Tochigi, Apan (Aug. 2019).

- [11 M. Hirai, S. Yamamoto, H. Arai, A. Kuwana, H. Tanimoto, Y. Gendai, H. Kobayashi, "Systematic Construction of Resistor Ladder Network for N-ary DACs", 13th IEEE International Conference on ASIC, Chongqing, China (Oct. 2019)