#### Revival of Asynchronous SAR ADC based on Hopfield Network

Zifei Xu, Xueyan Bai, Dan Yao,

Anna Kuwana, Haruo Kobayashi

# Division of Electronics and Informatics Gunma University

- Research Objective and Background

- Binary asynchronous SAR ADC

- Non-binary asynchronous SAR ADC

- Hopfield network and DAC

- Conclusion

- Research Objective and Background

- Binary asynchronous SAR ADC

- Non-binary asynchronous SAR ADC

- Hopfield network and DAC

- Conclusion

#### Value of ADC DAC Research

Analog signals are everywhere

Digital signals are useful for computer processing

Analog-digital interface circuits are important.

### **Hopfield neural net ADC**

Traditional Hopfield neural network ADC.

- Elements of "interest" are used as ADC design with realistic competitiveness. California Institute of Tech.

- Local minima problem

- Sometimes wrong output

- Revisit because of

- Very fast SAR ADC

- Non-binary SAR ADC as well as binary

- Simple design

Prof. John Joseph Hopfield **Princeton University**

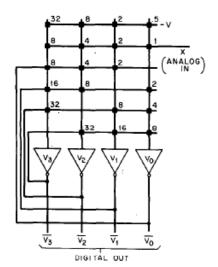

Fig. 2. The 4-bit A/D converter computational network. The analog input voltage is x, while the complement of the digital word  $V_3V_2V_1V_0$ which is computed to be the binary value of x is read out as the 0 or 1 values of the amplifier output voltages.

## Research Objective

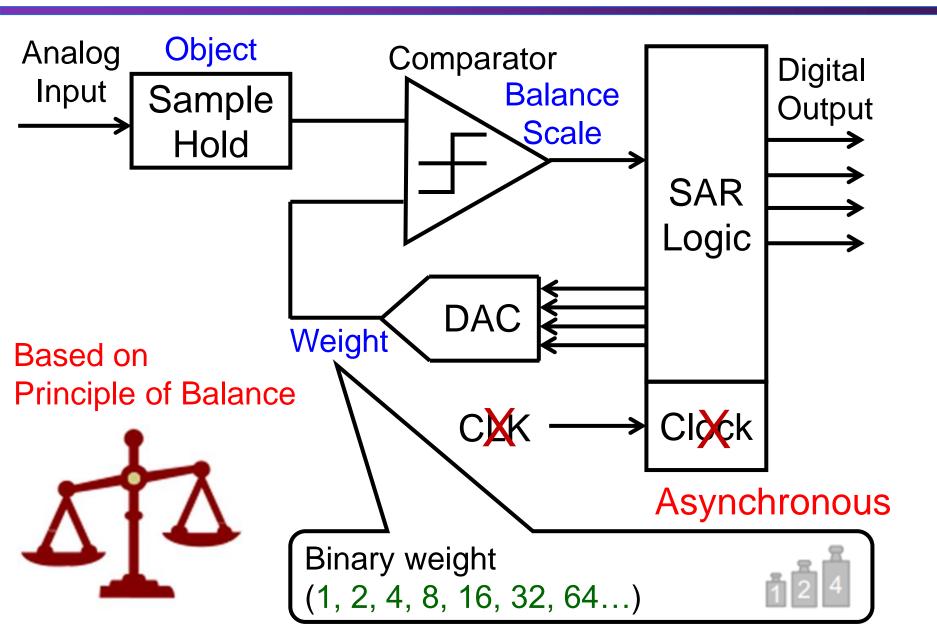

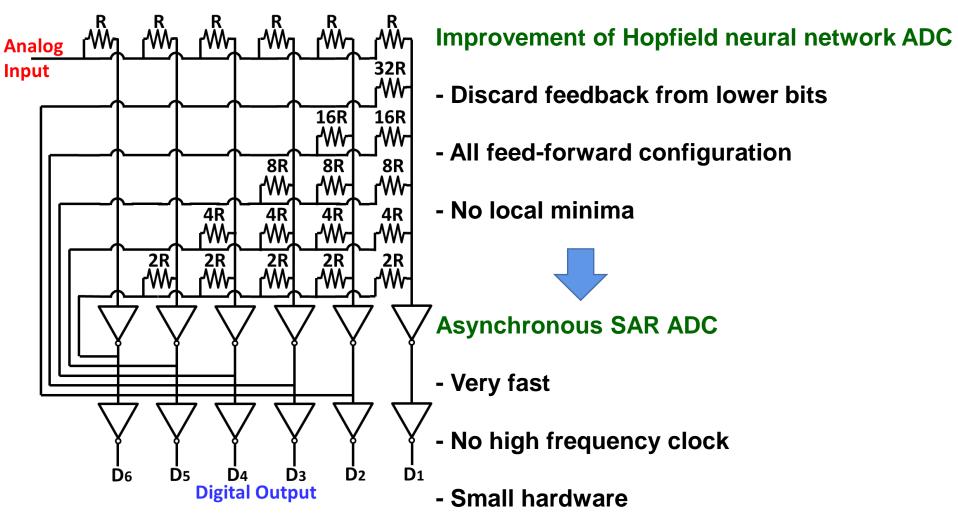

#### Improvement of Hopfield neural network ADC

- Discard feedback from lower bits

- All feed-forward configuration

- No local minima

- Always correct output

- Realization of asynchronous SAR ADC

- Very fast

- No high frequency clock required

- Small hardware

- Proposal of Non-binary asynchronous SAR ADC

- Research Objective and Background

- Binary asynchronous SAR ADC

- Non-binary asynchronous SAR ADC

- Hopfield network and DAC

- Conclusion

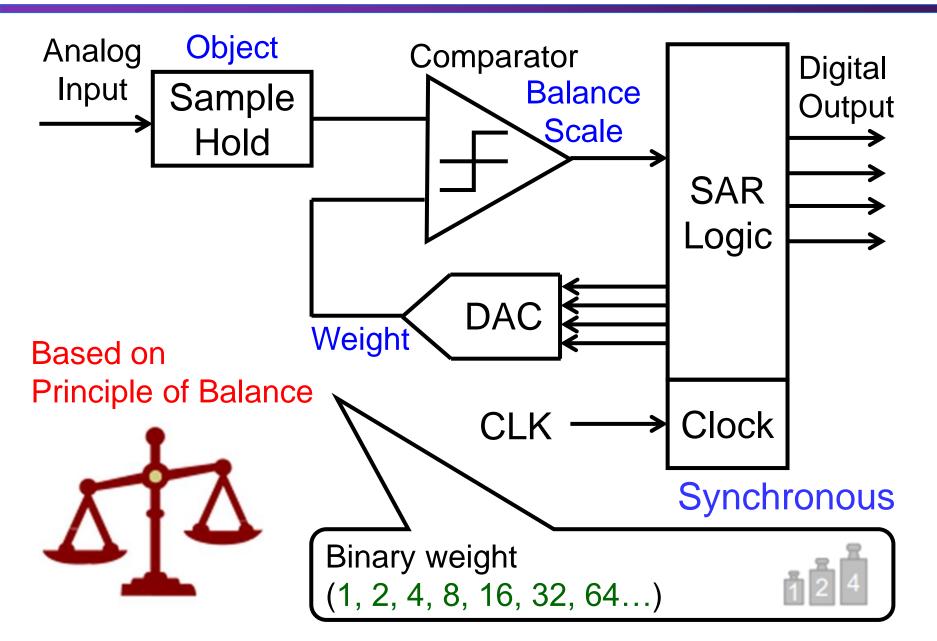

## **Binary Weighted SAR ADC**

### **Asynchronous Binary Weighted SAR ADC**

## **Investigated Network**

6-bit SAR ADC case

### **Correspondence Table**

#### 10-bit binary weighted SAR ADC

| Step   | 1st | 2nd | 3rd | 4th | 5th | 6th | 7th | 8th | 9th | 10th | output |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|--------|

| Weight | 516 | 256 | 128 | 64  | 32  | 16  | 8   | 4   |     |      | Output |

#### Decimal digital output:

Data =

$$(1/R)$$

D<sub>10</sub> +  $(1/R_9)$  D<sub>9</sub> +  $(1/R_8)$ D<sub>8</sub>+ $(1/R_7)$ D<sub>7</sub> +  $(1/R_6)$ D<sub>6</sub> +  $(1/R_5)$ D<sub>5</sub> +  $(1/R_4)$ D<sub>4</sub> +  $(1/R_3)$ D<sub>3</sub>+ $(1/R_2)$ D<sub>2</sub> +  $(1/R_1)$ D<sub>1</sub>

#### Here

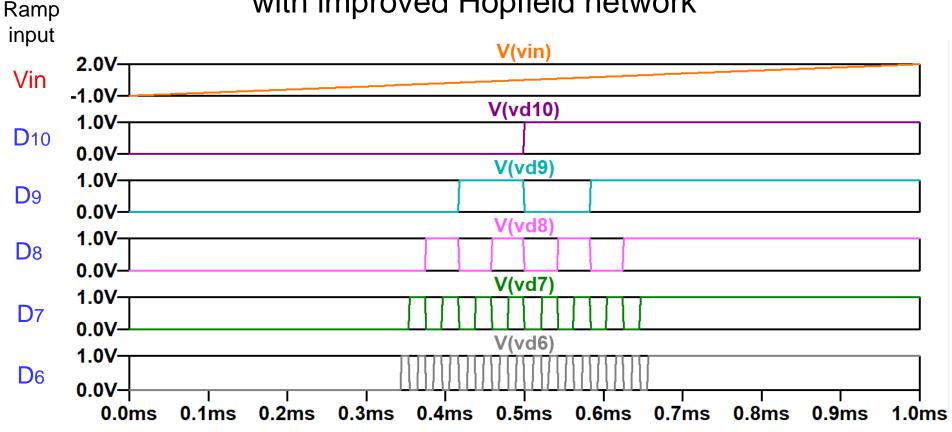

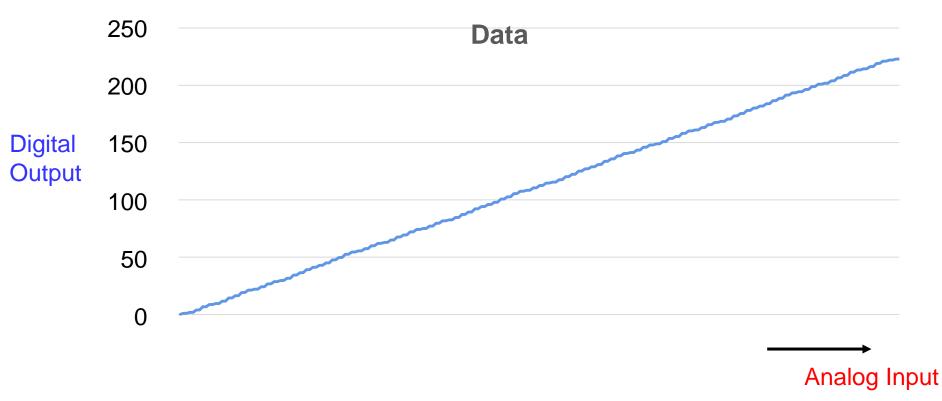

#### **SPICE Simulation Result**

10-bit asynchronous binary-weighted SAR ADC with improved Hopfield network

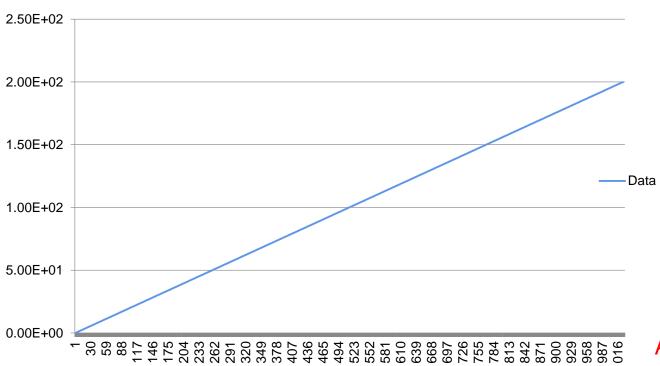

#### **Decimal Data Calculation**

Data =

$$(1/R)$$

D<sub>10</sub> +  $(1/R_9)$  D<sub>9</sub> + $(1/R_8)$ D<sub>8</sub>+ $(1/R_7)$ D<sub>7</sub> + $(1/R_6)$ D<sub>6</sub> +  $(1/R_5)$ D<sub>5</sub> +  $(1/R_4)$ D<sub>4</sub> +  $(1/R_3)$ D<sub>3</sub>+ $(1/R_2)$ D<sub>2</sub> +  $(1/R_1)$ D<sub>1</sub>

#### **Data**

## Digital output

Analog input

- Operation has been confirmed.

- Amazingly simple design can realize a 10-bit SAR ADC

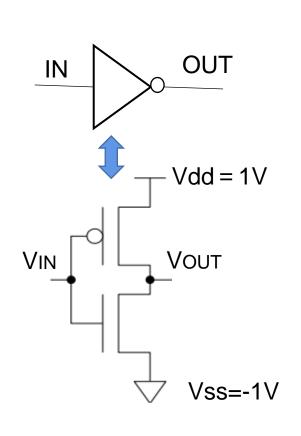

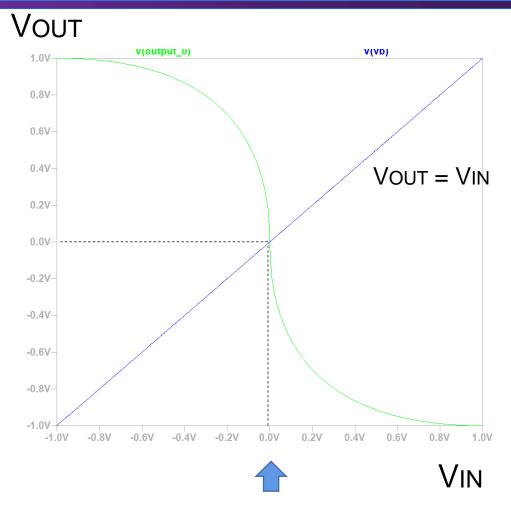

#### **CMOS** inverter

SPICE simulation

#### CMOS inverter threshold voltage

- ⇒ Affected by PVT variation

- ⇒ ADC nonlinearity

### **Application**

Asynchronous SAR ADC with Hopfield network

Advantage: High speed, small chip area

Disadvantage: ADC nonlinearity

due to resistors mismatch, inverter threshold voltage variation

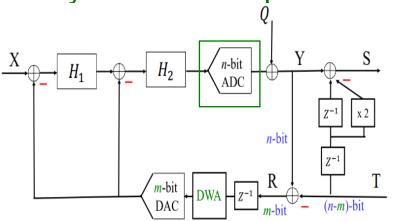

#### Proposed killer application

Usage inside multi-bit  $\Delta\Sigma$  ADC

Currently, 3-bit flash ADC is used.

More than 6-bit Hopfield asynchronous SAR ADC can be used. Its nonlinearity is noise-shaped inside the modulator.

Extended Leslie-Singh Architecture

- Research Objective and Background

- Binary asynchronous SAR ADC

- Non-binary asynchronous SAR ADC

- Hopfield network and DAC

- Conclusion

#### Fibonacci Number

#### **Definition** (n=0,1,2,3...)

$$F_0 = 0$$

$F_1 = 1$

$F_{n+2} = F_n + F_{n+1}$

#### Example of numbers(Fibonacci number)

0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89...

Leonardo Fibonacci (around 1170-1250)

#### **Property**

The closest terms ratio converges to "Golden Ratio"!

$$\lim_{n \to \infty} \frac{F_n}{F_{n-1}} = 1.618033988749895 = \varphi$$

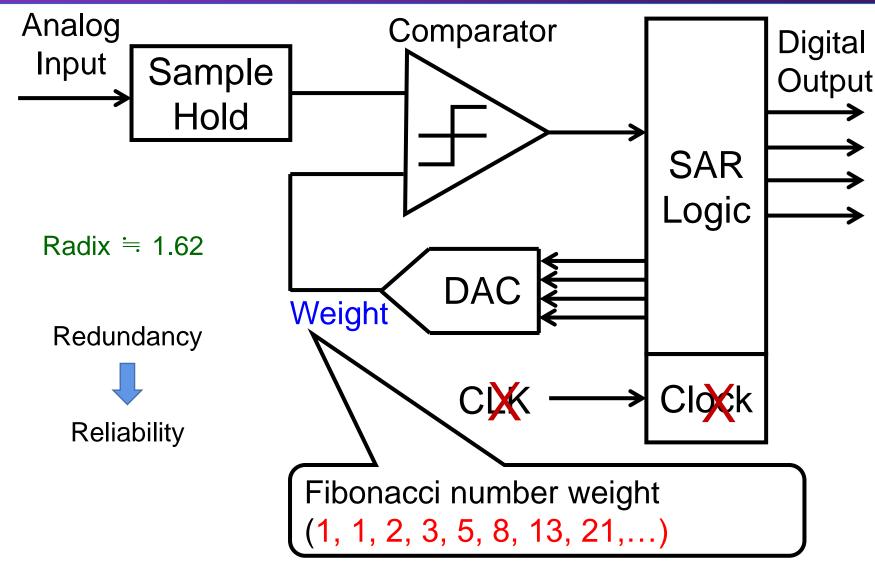

### Fibonacci number weighted SAR ADC

[1] Y. Kobayashi, H. Kobayashi, et. al., "SAR ADC Design Using Golden Ratio Weight Algorithm," ISCIT (Oct. 2015)

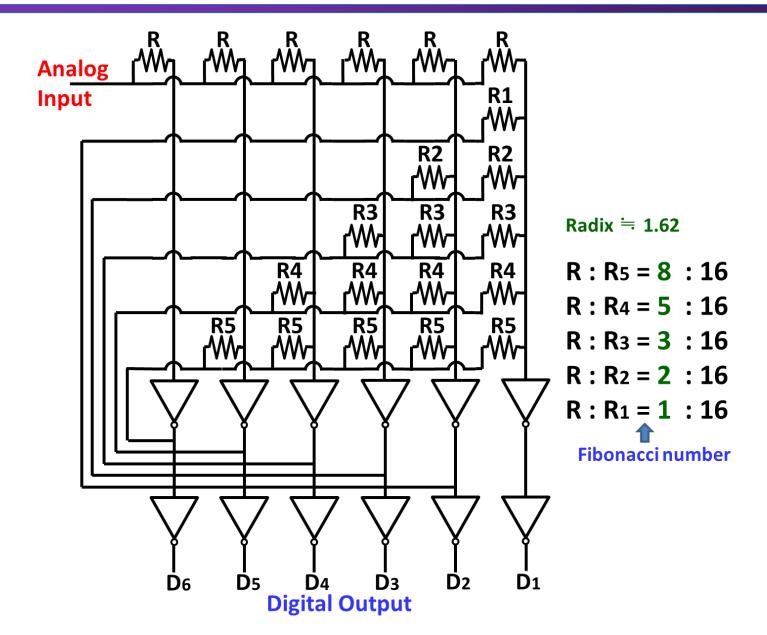

### Fibonacci number weighted SAR ADC

### **Correspondence Table**

#### 10-bit Fibonacci weighted SAR ADC

| Step   | 1st | 2nd | 3rd | 4th | 5th | 6th | 7th | 8th | 9th | 10th | output |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|--------|

| Weight | 89  | 55  | 34  | 21  | 13  | 8   | 5   | 3   |     |      | Output |

#### Decimal digital output:

Data =

$$(1/R)$$

D<sub>10</sub> +  $(1/R_9)$  D<sub>9</sub> +  $(1/R_8)$ D<sub>8</sub>+ $(1/R_7)$ D<sub>7</sub> +  $(1/R_6)$ D<sub>6</sub> +  $(1/R_5)$ D<sub>5</sub> +  $(1/R_4)$ D<sub>4</sub> +  $(1/R_3)$ D<sub>3</sub>+ $(1/R_2)$ D<sub>2</sub> +  $(1/R_1)$ D<sub>1</sub>

#### Here

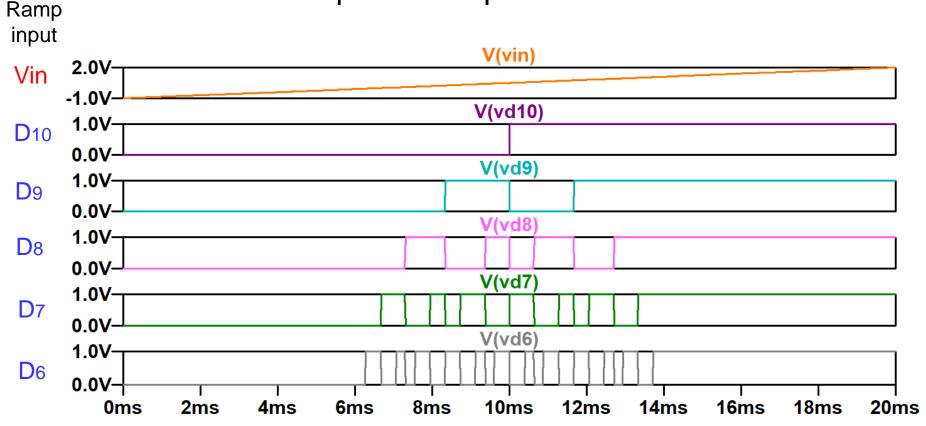

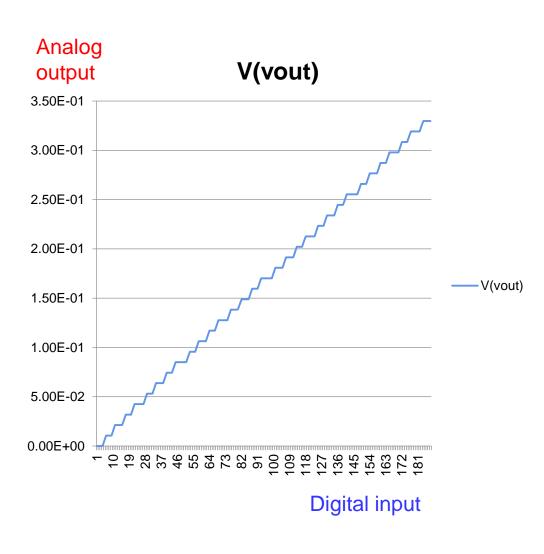

### **SPICE Simulation Result**

10-bit asynchronous Fibonacci number weighted SAR ADC with improved Hopfield network

Higher 5 bits

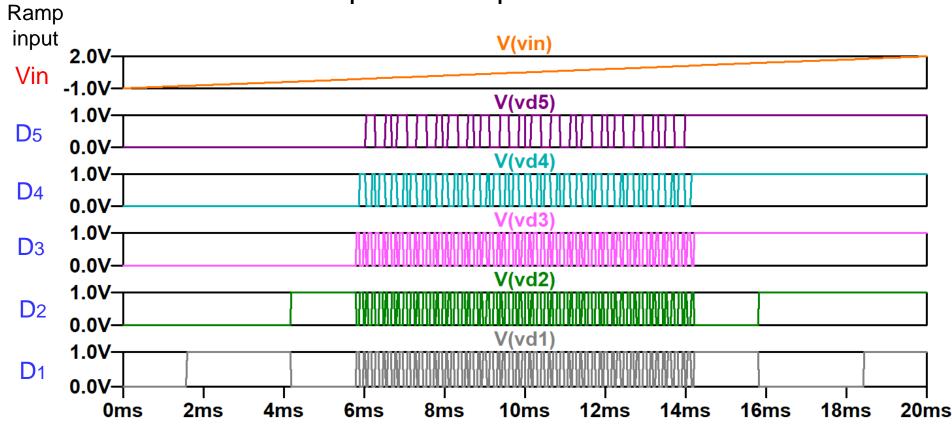

### **SPICE Simulation Result**

10-bit asynchronous Fibonacci number weighted SAR ADC with improved Hopfield network

Lower 5 bits

#### **Decimal Data Calculation**

Data =

$$(1/R)$$

D<sub>10</sub> +  $(1/R_9)$  D<sub>9</sub> + $(1/R_8)$ D<sub>8</sub>+ $(1/R_7)$ D<sub>7</sub> + $(1/R_6)$ D<sub>6</sub> +  $(1/R_5)$ D<sub>5</sub> +  $(1/R_4)$ D<sub>4</sub> +  $(1/R_3)$ D<sub>3</sub>+ $(1/R_2)$ D<sub>2</sub> +  $(1/R_1)$ D<sub>1</sub>

Operation has been confirmed.

- Research Objective and Background

- Binary asynchronous SAR ADC

- Non-binary asynchronous SAR ADC

- Hopfield network and DAC

- Conclusion

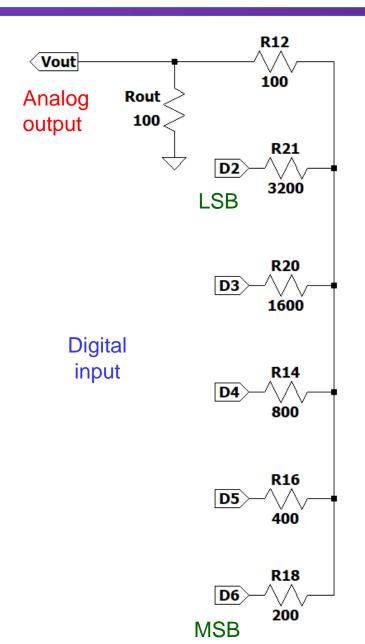

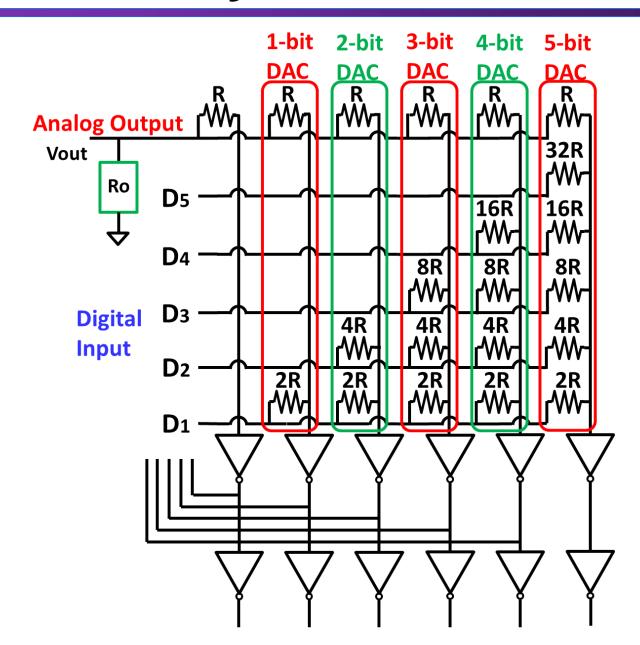

## **DAC** inside Hopfield network

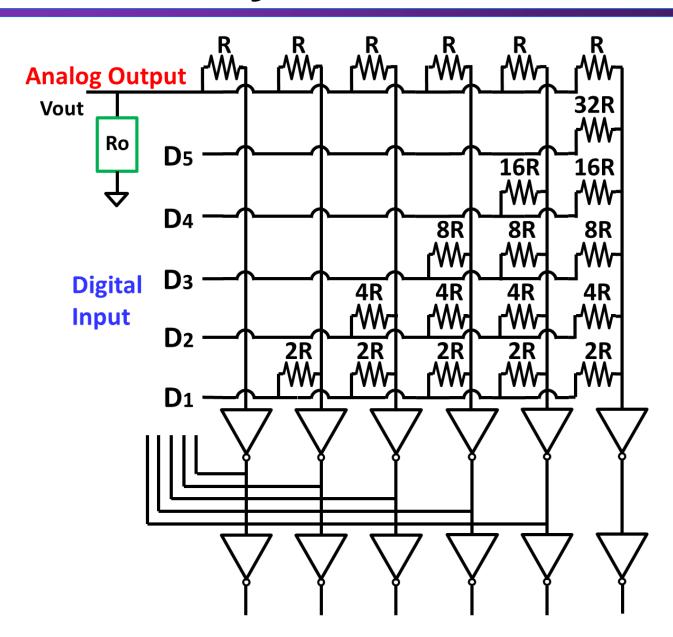

## DAC array inside network

### DAC array inside network

- Research Objective and Background

- Binary asynchronous SAR ADC

- Non-binary asynchronous SAR ADC

- Hopfield network and DAC

- Conclusion

### Conclusion

- Improved Hopfield network ADC

- Asynchronous SAR ADC

- Very fast

- Simple design

- Non-binary as well as binary configurations

- Competitive to state-of-the-art SAR ADC

- Verified by SPICE simulation

- Large resistors with good matching and small chip area

- ⇒ Technology development is expected

## Thank you for listening

## ご清聴ありがとうございました