IEEE 15th International Conference on ASIC Nanjing, China, Oct 27, 2023 15:45-16:15

# Signal Generation Technologies for Analog/Mixed-Signal IC Testing

Haruo Kobayashi

Gunma University

koba@gunma-u.ac.jp

Kobayashi Lab. Gunma University

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- $\Delta\Sigma$  DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

AWG: Arbitrary Waveform Generator ATE: Automatic Test Equipment

#### <u>Objective</u>

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

- To introduce research achievements of

- Author's group

- Signal generation technologies

for analog/mixed-signal IC testing

• To see trend of test signal generation technologies

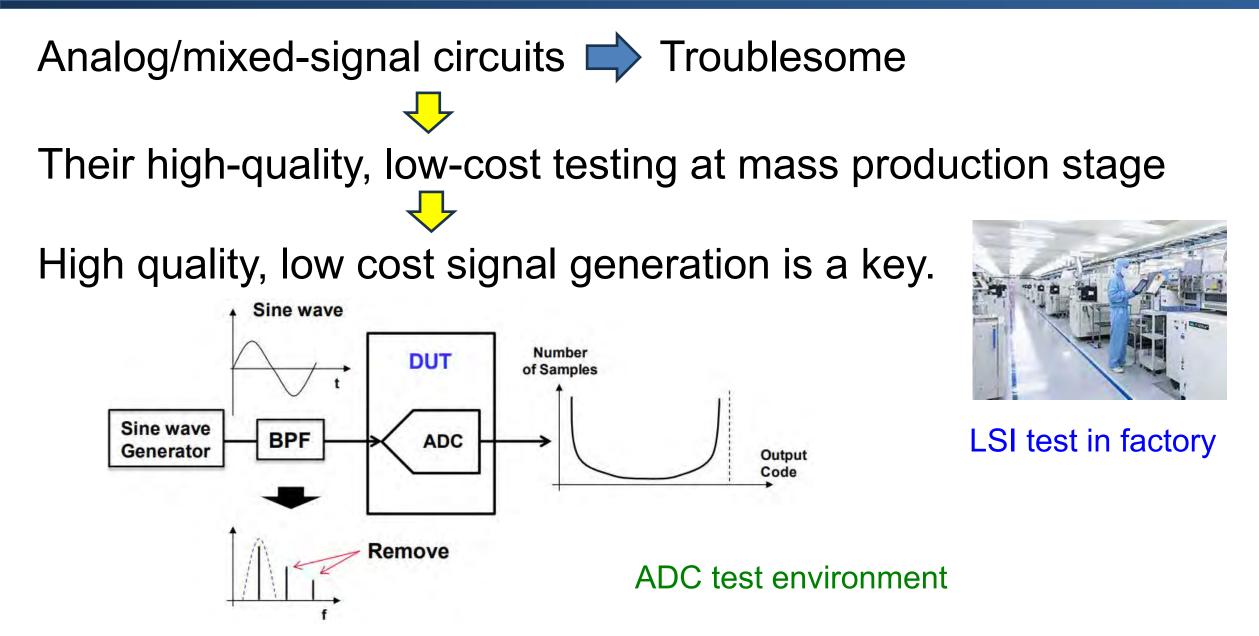

#### **Research Background**

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

AWG: Arbitrary Waveform Generator

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

AWG: Arbitrary Waveform Generator

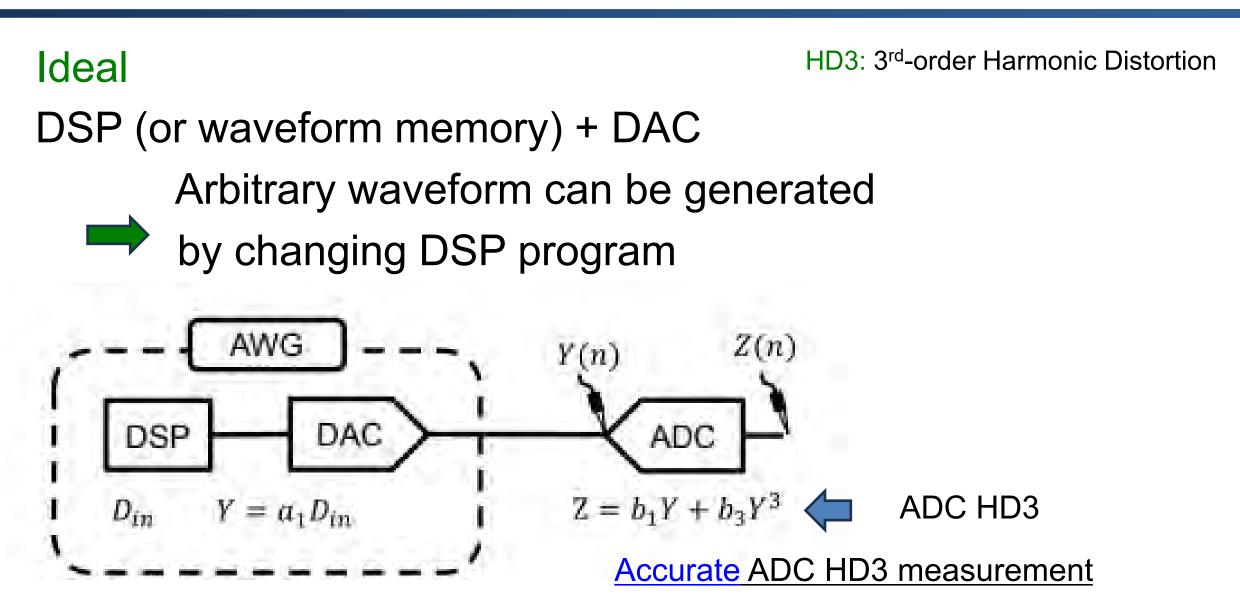

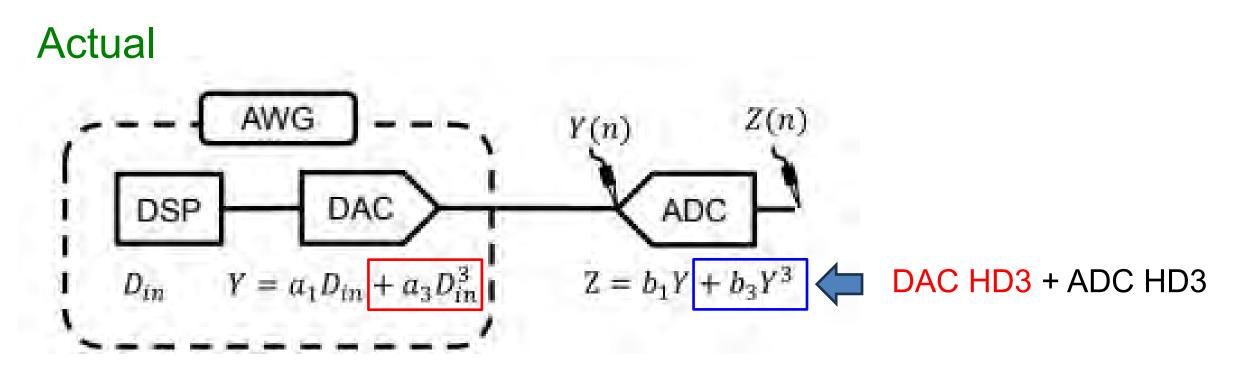

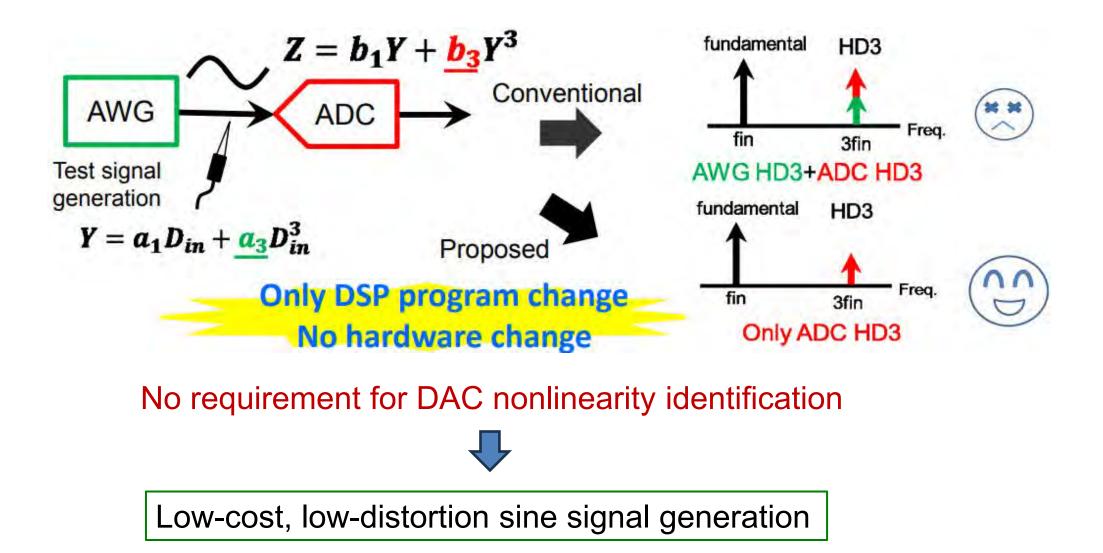

#### Arbitrary Waveform Generator (AWG)

#### Arbitrary Waveform Generator (AWG)

NOT accurate ADC HD3 measurement

DAC nonlinearity is Limit AWG output signal quality

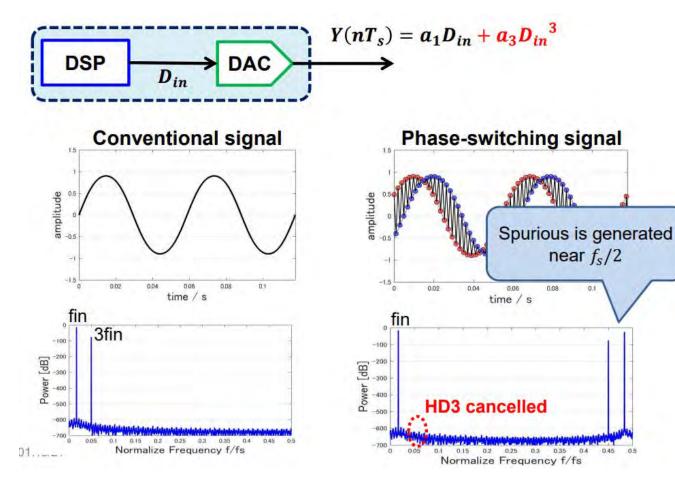

### One-Tone Signal Generation: Phase Switching

[1] "Low-Distortion Signal Generation for ADC Testing," IEEE International Test Conference (Oct. 2014).

10/46

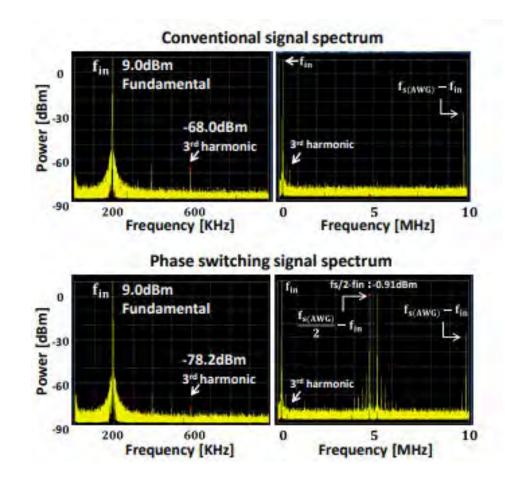

#### **One-Tone: Phase Switching**

$D_{in} = \begin{cases} X_0 = A \sin(2\pi f_{in} nT_s + \pi/6) & n: \text{ even} \\ X_1 = A \sin(2\pi f_{in} nT_s - \pi/6) & n: \text{ odd} \end{cases}$

Measurement Results

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

AWG: Arbitrary Waveform Generator

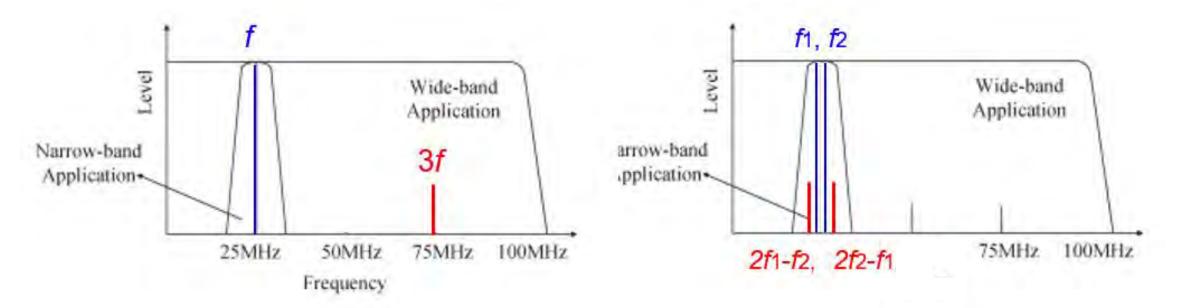

#### Why Two-Tone Testing ?

Linearity testing of narrow-band device with 3<sup>rd</sup> order-distortion Communication applications

Single-tone: HD3 Out of band

HD3: 3<sup>rd</sup>-order Harmonic Distortion

IMD3: 3<sup>rd</sup>-order Intermodulation Distortion

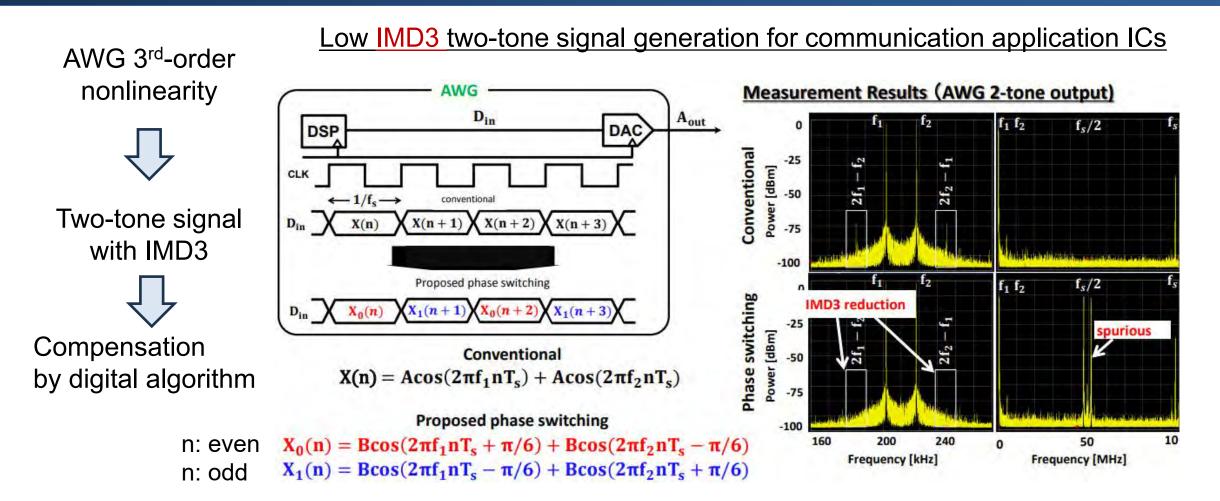

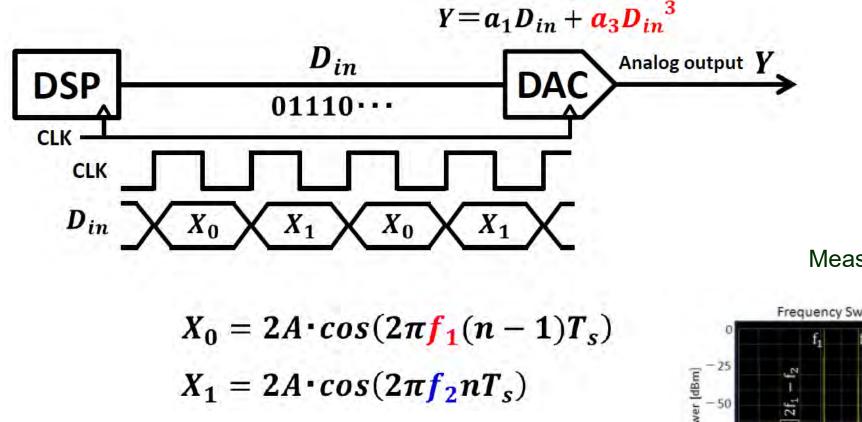

### **Two-Tone Signal: Phase Switching**

[2] "Two-Tone Signal Generation for Communication Application ADC Testing," IEEE Asian Test Symposium (Nov. 2012).

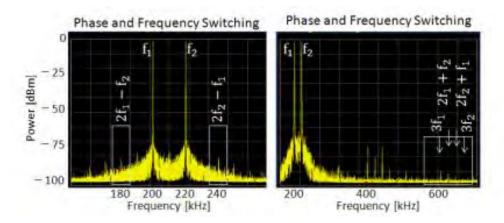

#### Two-Tone Signal: Frequency Switching

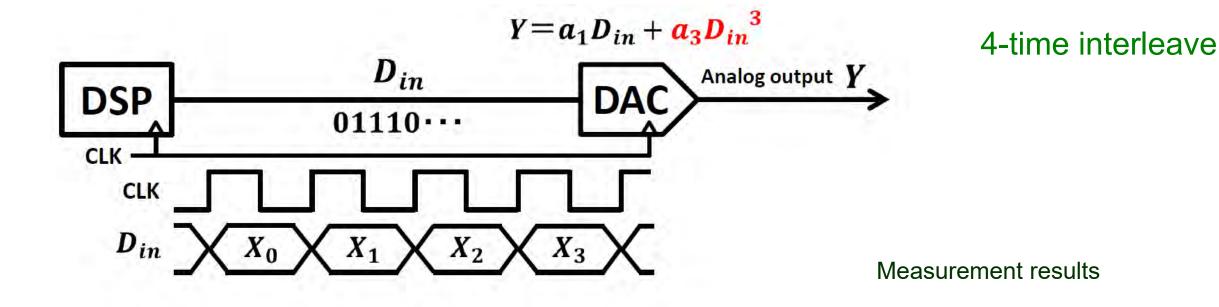

#### Two-Tone Signal: Phase Frequency Switching

$$X_{0} = A \cdot cos(2\pi f_{1}(n-3)T_{s})$$

$$X_{1} = A \cdot cos(2\pi f_{1}(n-2)T_{s} + \pi/3)$$

$$X_{2} = A \cdot cos(2\pi f_{2}(n-1)T_{s})$$

$$X_{3} = A \cdot cos(2\pi f_{2}nT_{s} + \pi/3)$$

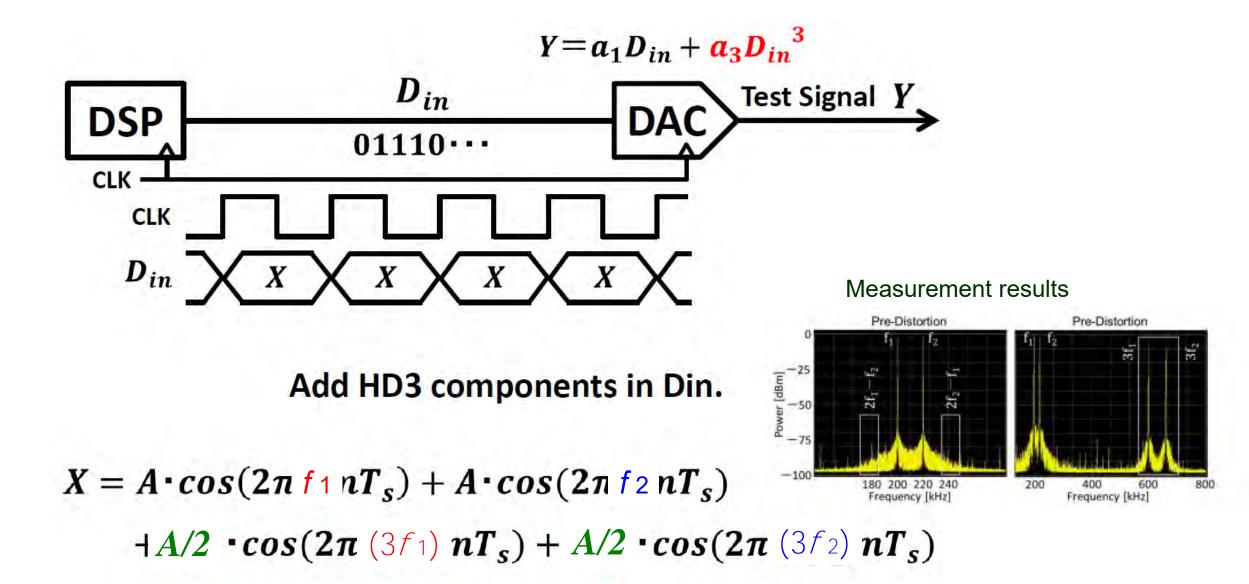

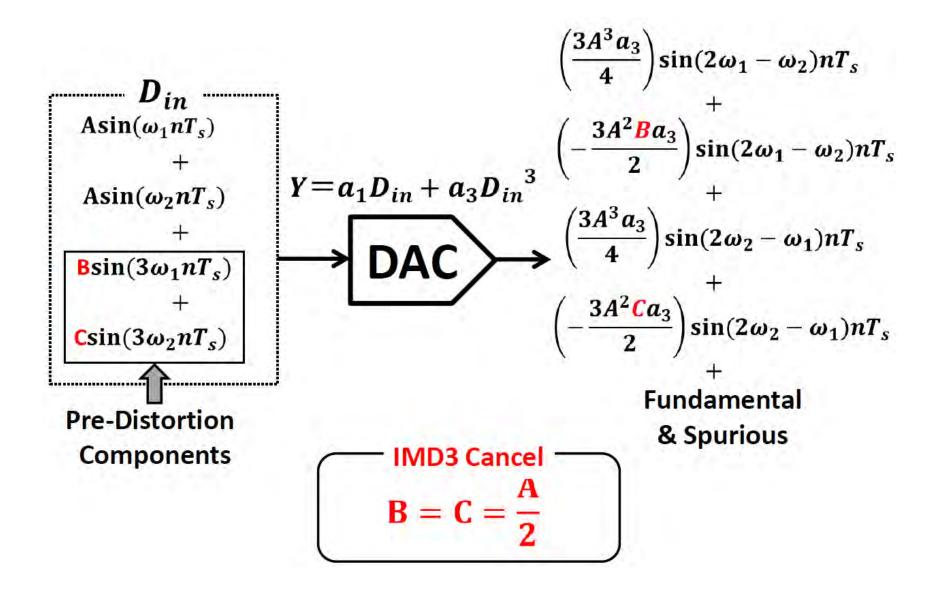

#### **Two-Tone Signal: Pre-Distortion**

17/46

#### Two-Tone Signal: Pre-Distortion Principle

Power Spectrum Map

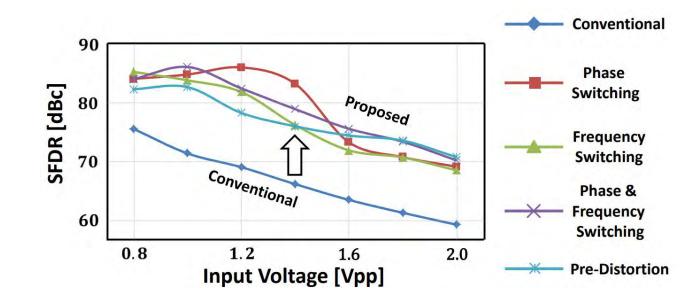

#### **Measurement Results**

| -                          | Disappear                              |                           | Appear                                                                                                      |

|----------------------------|----------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------|

| Conventional               |                                        |                           | $2f_1 - f_2 = 2f_2 - f_1$                                                                                   |

| Phase<br>Switching         | $\frac{2f_1 - f_2}{3f_1}$              | $\frac{2f_2 - f_1}{3f_2}$ | Around $f_s/2$                                                                                              |

| Frequency<br>Switching     | $\frac{2f_1 - f_2}{2f_1 + f_2}$        |                           | Around $f_s/2$                                                                                              |

| Phase & Freq.<br>Switching | $\frac{2f_1 - f_2}{2f_1 + f_2}$ $3f_1$ |                           | Around $f_s/2$ $f_s/4$                                                                                      |

| Pre-Distortion             | $2f_1 - f_2$                           | $2f_2 - f_1$              | $\begin{array}{rrrr} 4f_1 - 3f_2 & 4f_2 - 3f_1 \\ \\ \text{Around} & 3f_1 & 5f_1 & 7f_1 & 9f_1 \end{array}$ |

- Four methods are comparable.

- SFDR improvement by ~10 dB

**SFDR:** Spurious Free Dynamic Range

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

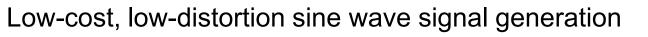

#### One-Tone Signal from Digital Clock

21/46

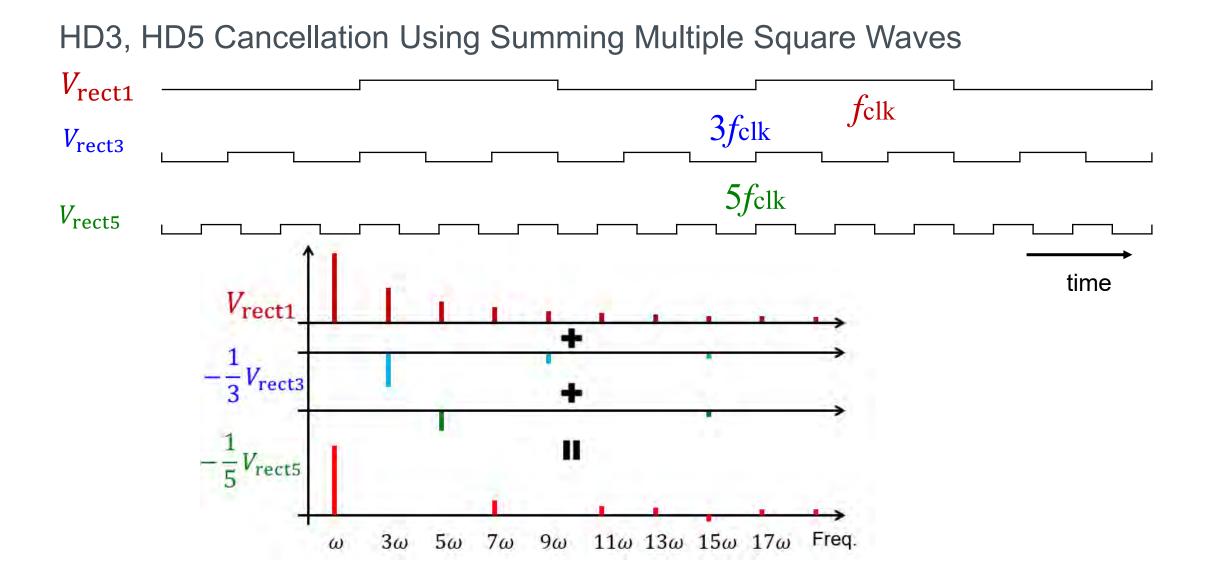

#### **Fourier Series Analysis**

• 100kHz Square Wave  $V_{rect1}(t) = \frac{\sin(\omega t)}{3} + \frac{1}{3} \frac{\sin(3\omega t)}{5} + \frac{1}{5} \frac{\sin(5\omega t)}{7} + \frac{1}{7} \sin(7\omega t) \cdots$ • 300kHz Square Wave

$V_{rect2}(t) = \frac{\sin(3\omega t)}{3} + \frac{1}{3}\sin(9\omega t) + \frac{1}{5}\sin(15\omega t) + \frac{1}{7}\sin(21\omega t) \cdots$

• 500kHz Square Wave  $V_{rect3}(t) = \overline{\sin(5\omega t)} + \frac{1}{3}\sin(15\omega t) + \frac{1}{5}\sin(25\omega t) + \frac{1}{7}\sin(35\omega t) \cdots$

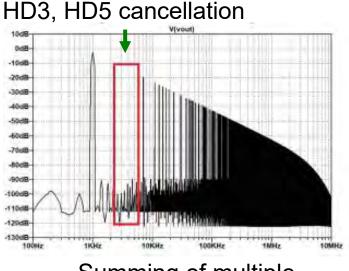

#### Simulated Power Spectrum

Rectangular  $V_{rect1}$

Summing Multiple Square Waves  $f(t) = V_{rect1}(t) - \frac{1}{3}V_{rect2}(t) - \frac{1}{5}V_{rect3}(t)$   $= \frac{\sin(\omega t)}{3} + \frac{1}{3}\frac{\sin(3\omega t)}{3} + \frac{1}{5}\frac{\sin(5\omega t)}{5} + \frac{1}{7}\sin(7\omega t) \cdots$   $- \frac{1}{3}\left[\frac{\sin(3\omega t)}{5} + \frac{1}{3}\sin(9\omega t) + \frac{1}{5}\sin(15\omega t) + \frac{1}{7}\sin(21\omega t) \cdots\right]$   $- \frac{1}{5}\left[\frac{\sin(1\omega t)}{5} + \frac{1}{3}\sin(15\omega t) + \frac{1}{5}\sin(25\omega t) + \frac{1}{7}\sin(35\omega t) \cdots\right]$   $= \frac{\sin(\omega t)}{5} + \frac{1}{7}\sin(7\omega t) + \frac{1}{11}\sin(11\omega t) + \cdots$

$\uparrow \underline{\sin(3\omega t)}$  and  $\underline{\sin(5\omega t)}$  are cancelled

Summing of multiple

#### Implementation with very simple circuits

[3] "Low Distortion Sine Wave Generator with Simple Harmonics Cancellation Circuit and Filter for Analog Device Testing," IEICE Electronics Express (Jan. 2023)

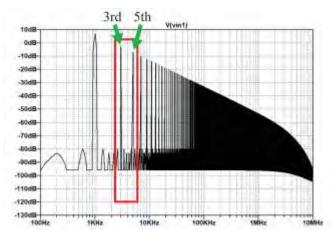

#### **Measurement Results**

-79.6 dBm

• RBW: 300 Hz • SWT: 55.6 s

M2 M4

VBW: 300 Hz Trig: Free Run • Detect: RMS

401 587

Ref: -10.0 dBm

101.4965 kHz 101.587 kHz -15.3 dBm

301 587 kHz

Att: 20 dB

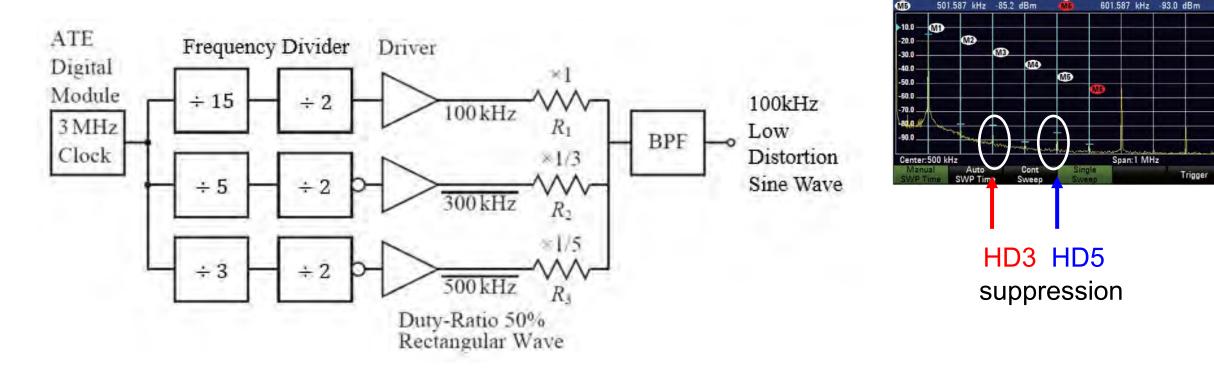

#### Combination with Digital Predistortion

# (i) Measure HD2, HD3(ii) Add their 180-degree shifted signals by function generators

Low-distortion signal generation for 16-bit ADC test

[4] "Low Distortion Sinusoidal Signal Generator with Harmonics Cancellation Using Two Types of Digital Predistortion", IEEE International Test Conference (Oct. 2023)

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

ATE: Automatic Test Equipment

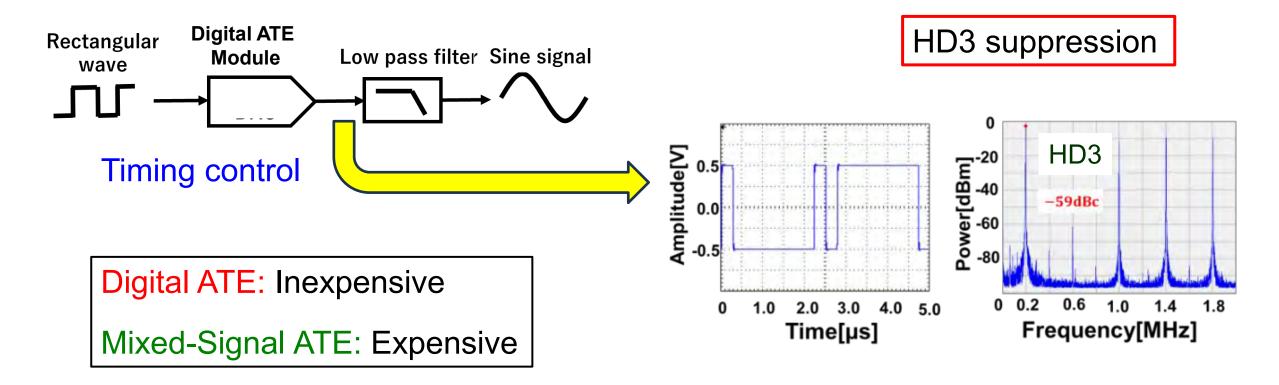

# One-Tone Signal from Digital ATE Module

Proposed sine signal generation

[5] "Low-Distortion Signal Generation for Analog/Mixed-Signal Circuit Testing Using Digital ATE," IEEE International Test Conference in Asia (Sept. 2017).

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

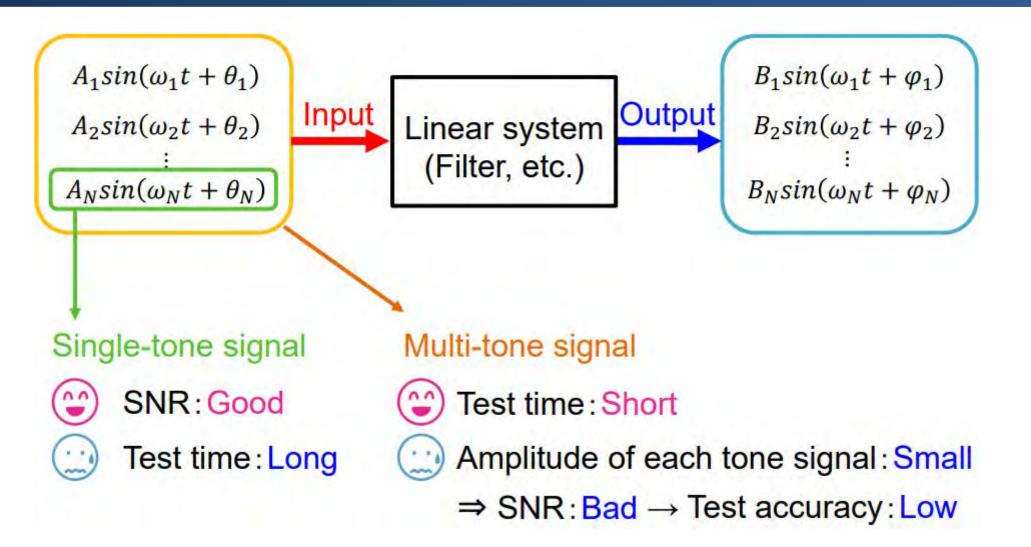

### Use of Multi-Tone Signal for Analog IC Test

[6] "Analysis and Design of Multi-Tone Signal Generation Algorithms for Reducing Crest Factor", IEEE Asian Test Symposium (Nov. 2020).

28/46

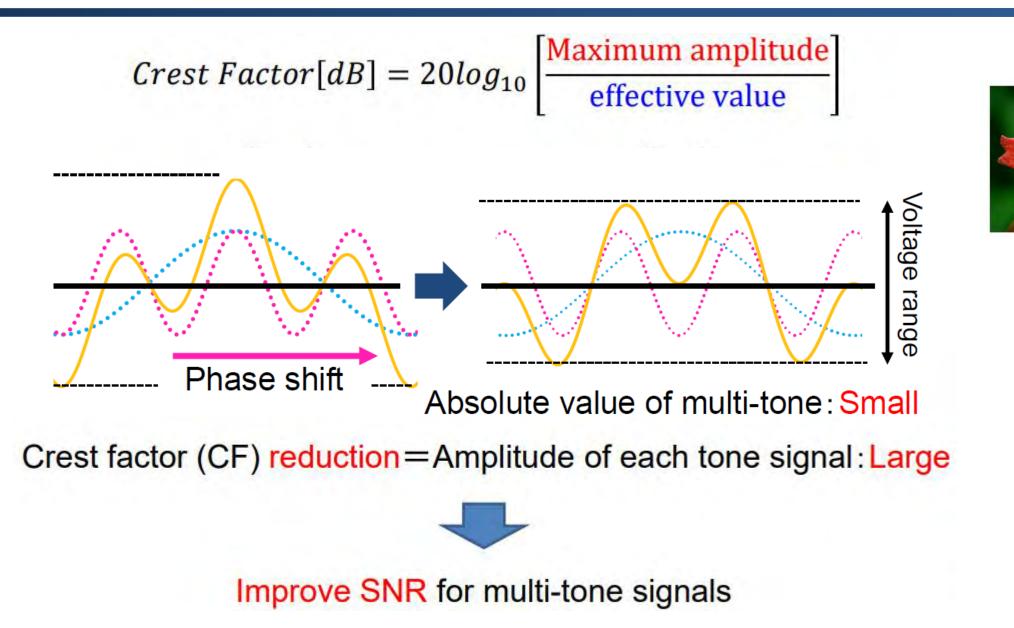

#### What is Crest Factor ?

29/46

Crest

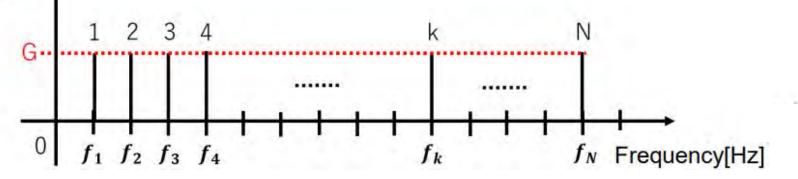

### Multi-Tone Signal: Crest Factor Reduction

Basic

equation :

$$s(t) = G \sum_{k=1}^{N} cos(\frac{2\pi f_k t}{T} + \theta_k)$$

N : number of tones T : resolution of 1 cycle

| Newman Phase    | $\theta_k = \frac{\pi}{N}(k-1)^2$      |  |

|-----------------|----------------------------------------|--|

| Kitayoshi Phase | $\theta_k = \frac{\pi}{N}k(k+1)$       |  |

| Schroeder Phase | $\theta_k = -\frac{\pi}{N}k(k-1)$      |  |

| Narahashi Phase | $\theta_k = \frac{\pi}{N-1}(k-1)(k-2)$ |  |

We showed these are equivalent for crest factor reduction

Amplitude

Crest factor  $\Rightarrow \sim 1.6$

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

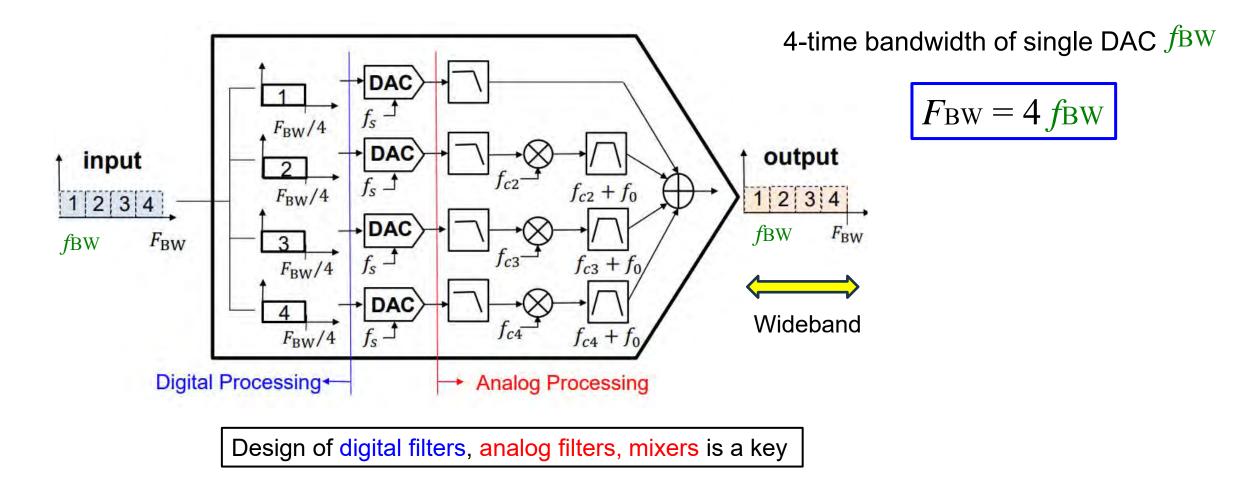

### Wideband Signal: Bandwidth Interleaved DAC

[7] "Frequency Interleaved DAC System Design: Fundamental Problems and Compensation Methods," 8th International Congress on Information and Communication (Feb. 2023)

- Research Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

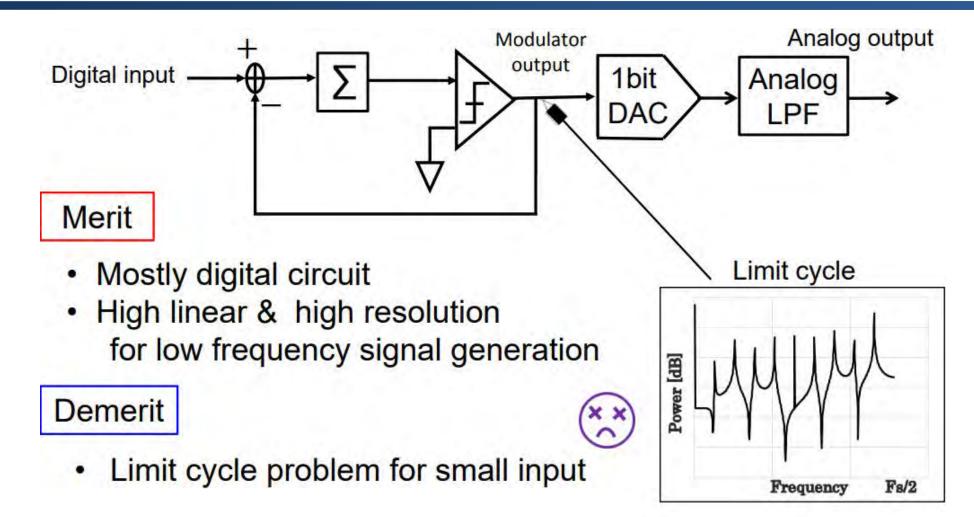

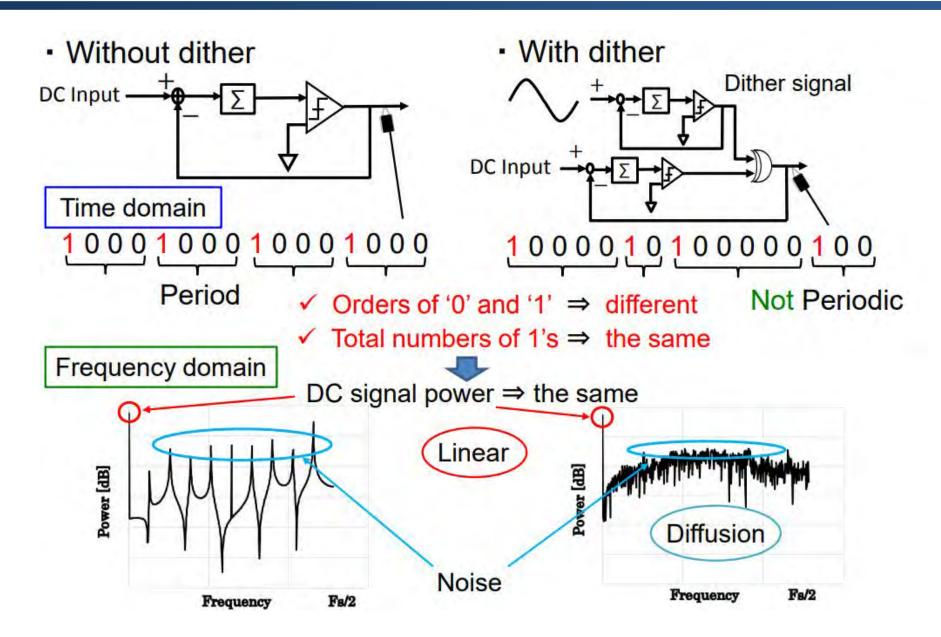

# ΔΣ DAC: Limit Cycle

[8] "Limit Cycle Suppression Technique Using Digital Dither in Delta Sigma DA Modulator", IEEE International Conference on Solid-State and Integrated Circuit Technology (Oct. 2016).

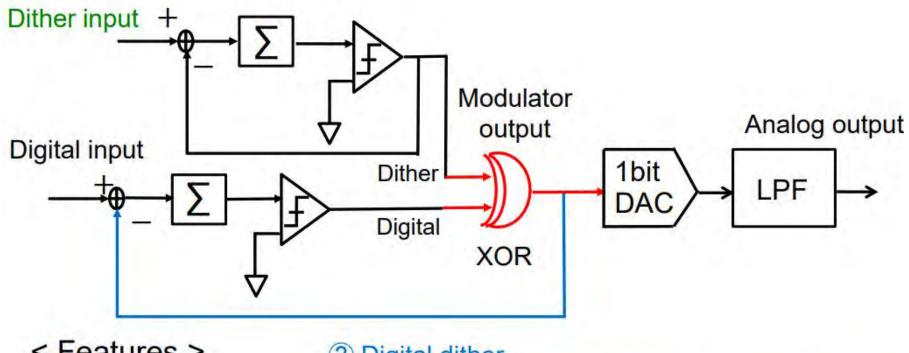

#### ΔΣ DAC: Digital Dither Usage

< Features >

1-bit output

2 Digital dither

⇒ NOT affect output signal, thanks to feedback

③ Easily generated digital dither

Digital signal "1" reverses comparator output with XOR

# ΔΣ DAC: Limit Cycle Suppression with Dither

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- <u>Clock Jitter Reduction</u>

- Analog Filter

- Conclusion

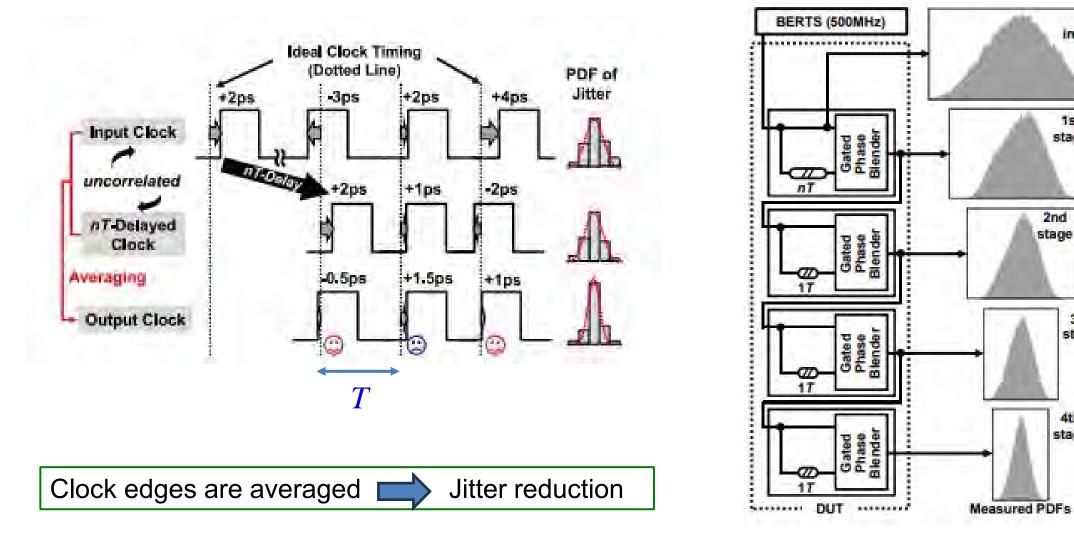

### **Clock Jitter Reduction: Phase Blending Method**

38/46

Input

1st

stage

2nd

stage

3rd stage

4th stage

[9] "A Clock Jitter Reduction Circuit Using Gated Phase Blending Between Self-Delayed Clock Edges," IEEE Symposium on VLSI Circuits, Honolulu (June 2012).

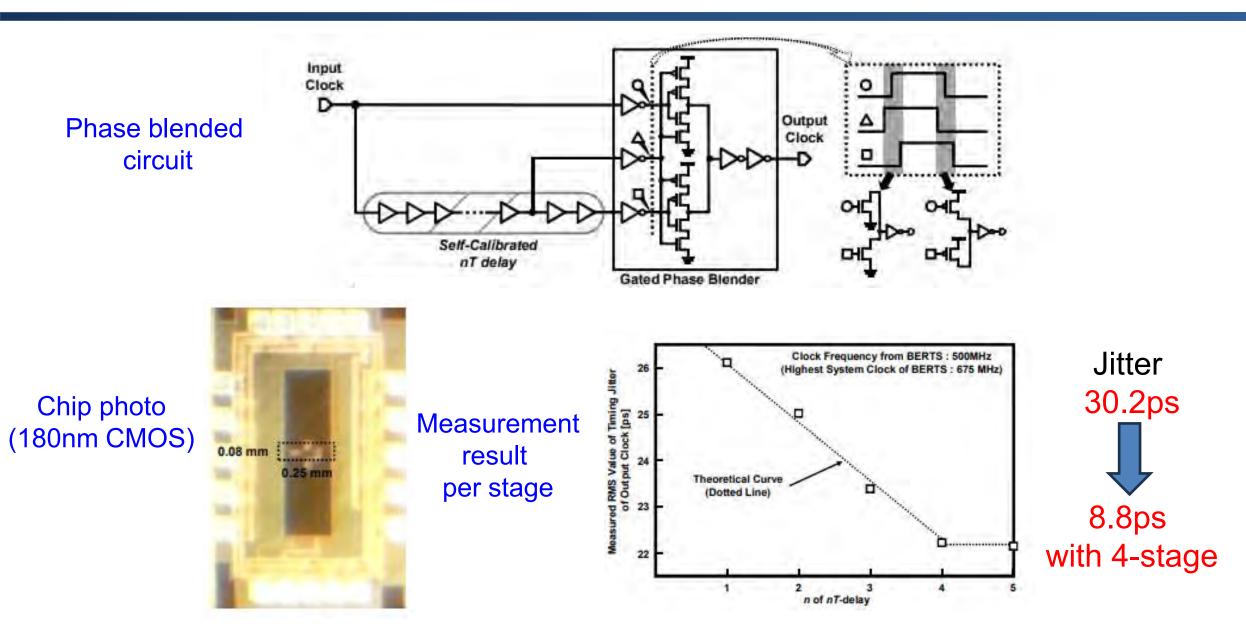

#### **Circuit, Measurement Results**

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

- Conclusion

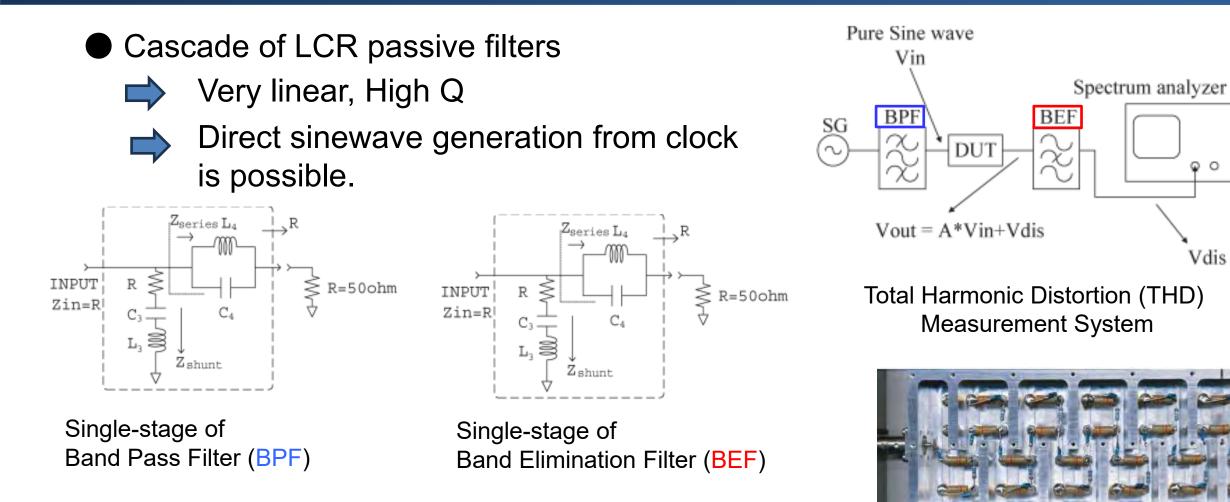

# High Performance Analog Filter

[10] "Total Harmonic Distortion Measurement System for Electronic Devices up to100MHz with Remarkable Sensitivity" IEEE Trans. Instrumentation and Measurement (Dec. 2007).

41/46

Q 0

Vdis

20-stage BPF:

Integration of discrete components

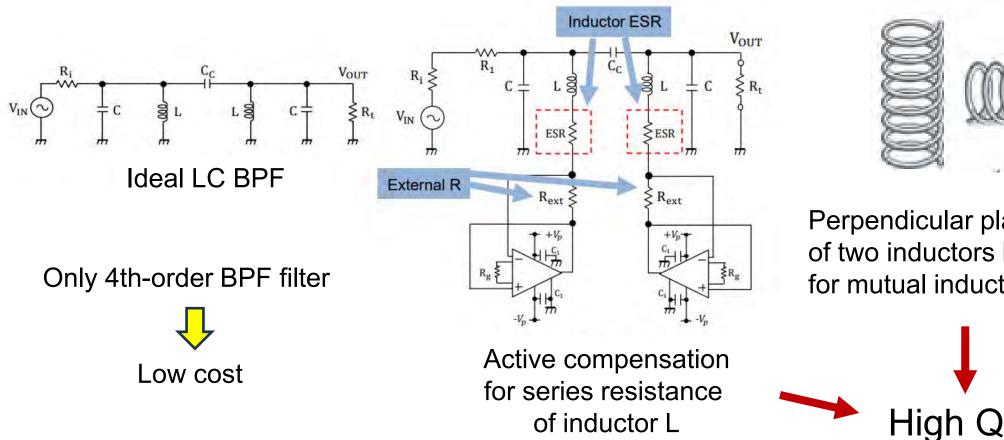

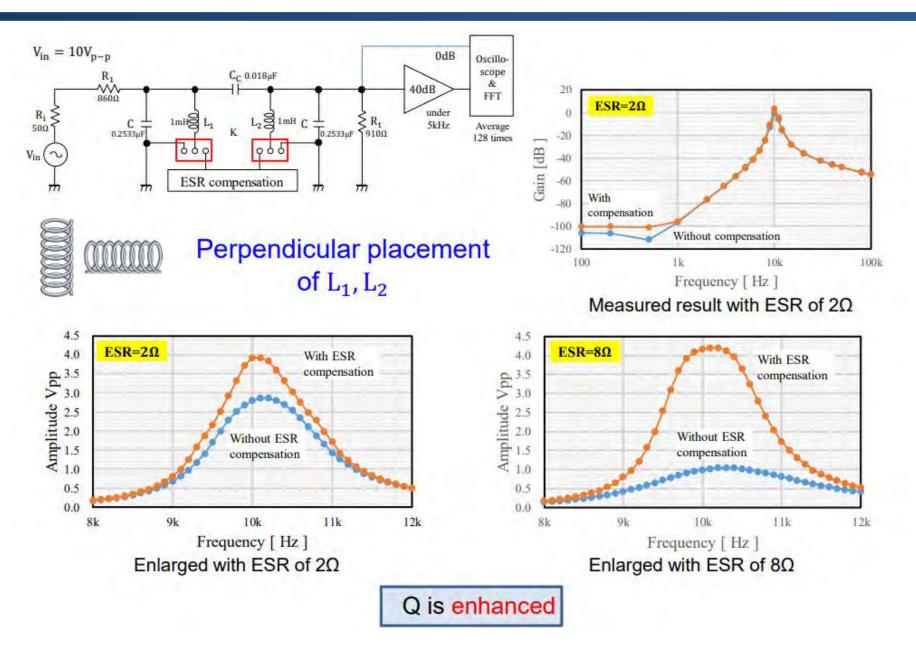

#### Low Cost Analog Filter

Perpendicular placement of two inductors L for mutual inductance M reduction

[11] "Design Consideration for LC Analog Filters: Inductor ESR Compensation, Mutual Inductance Effect and Variable Center Frequency"

8th International Congress on Information and Communication (Feb. 2023)

#### **Measurement Verification**

- Objective

- One-Tone and Two-Tone Signal Generation with AWG

- One-Tone Signal Generation from Digital Clock

- One-Tone Signal Generation with Digital ATE

- Multi-Tone Signal Generation Algorithm

- Wideband Signal Generation

- ΔΣ DAC Limit Cycle Suppression

- Clock Jitter Reduction

- Analog Filter

#### <u>Conclusion</u>

### Conclusion

#### • Explained research achievements

- Author's Group

- Signal generation technologies for AMS IC testing

- Trend is found:

- Digital-oriented methods become more employed

- Often the analog circuit is a key

for very high performance.

Kobayashi laboratory members and research associates, especially O. Kobayashi, K. Asami, K. Niitsu, T. Nakatani, K. Sato, M. Kawabata, T. Komuro and P. Sarson