# on Fundamentals of Electronics, Communications and Computer Sciences

DOI:10.1587/transfun.2023GCI0002

Publicized:2023/12/07

This article has been accepted and published on J-STAGE in advance of copyediting. Content is final as presented.

A PUBLICATION OF THE ENGINEERING SCIENCES SOCIETY

The Institute of Electronics, Information and Communication Engineers Kikai-Shinko-Kaikan Bldg., 5-8, Shibakoen 3 chome, Minato-ku, TOKYO, 105-0011 JAPAN

## How the Author's Group Came Up with Ideas in Analog/Mixed-Signal Circuit and System Area

Haruo Kobayashi<sup>†</sup>, Senior Member

SUMMARY This article reviews the author's group research achievements in analog/mixed-signal circuit and system area with introduction of how they came up with the ideas. Analog/mixed-signal circuits and systems have to be designed as well-balanced in many aspects, and coming up ideas needs some experiences and discussions with researchers. It is also heavily dependent on researchers. Here, the author's group own experiences are presented as well as their research motivations.

*key words:* Circuit and system research, Waveform sampling, ADC, DAC, TDC, Analog IC test

#### 1. Introduction

This article reviews the author's group research achievements in analog/mixed-signal (AMS) circuit and system area with introduction of how they came up with the ideas as well as the research motivations. Many of their approaches are based on signal processing algorithms, control theory and mathematics, which are different from other AMS IC design researchers, though their practical industry applications are taken into account in many cases. AMS circuits and systems have to be designed as wellbalanced in many aspects, and design trade-off is an important concept. Coming up ideas needs some experiences and discussions with researchers both in academia and industry. It is also heavily dependent on researchers themselves. Here, the author's group own experiences are presented as well as their research motivations [1-7].

In Section 2, circuits related to resistor and capacitor networks are shown. In Sections 3, 4, waveform sampling technologies and Nyquist-rate DAC are introduced respectively. In Sections 5, 6, 7, successive-approximation-register (SAR) ADCs with redundancy, time-interleaved ADCs, and time-to-digital converters (TDCs) are described. In Sections 8, 9,  $\Delta\Sigma$  ADC/DAC/TDC and dynamic element matching techniques are shown, while in Section 10, other research results are summarized. Section 11 concludes the paper.

All of the cited references in this paper are from the author's group and for the technical details, the reader can refer to them.

#### 2. Resistor and Capacitor Networks

2.1 Spatial and Temporal Dynamics of Active Resistor Network

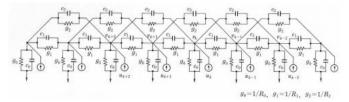

A long time ago, the author was involved in the research for an analog image processing neuro-chip or vision chip which consisted of positive and negative resistors (i. e., active resistors) (Fig. 1) [8, 9, 10], and the following circuit theorem was derived [11, 12]:

"For uniform active networks, the spatial and temporal stability conditions are equivalent."

Its generalization to non-uniform networks is discussed in [13, 14].

Triggered by this research, the author became interested in the resistor network, and his group were involved in extension and non-ideality analysis of R-2R ladder DAC and Hopfield network. Also, the research for the circulant active resistor network dynamics in [12] leads to the RC polyphase filter because it has the circulant structure.

Fig. 1 Active resistor network with positive and negative resistors [9].

## 2.2 General Resistor Network DAC

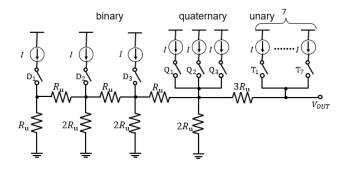

We have performed design and analysis of DACs based on the non-uniform current division resistive ladder, and came up with a new configuration DAC with segmentation of binary, quaternary and unary resistive-ladders, which enables two times gain with equivalent chip area and current sources to the conventional DAC (Fig.2). Also, our simulation showed that the DNL deviation of the proposed one is a little better than the conventional one [15, 16].

<sup>&</sup>lt;sup>†</sup>The author is with Gunma University, Kiryu, Gunma, 376-8515 Japan.

Further, we investigated a systematic configuration method of resistor ladder networks for N-ary DACs, by generalizing the configuration of the conventional R-2R DAC [17].

Notice that the capacitor-type DAC is popular due to low power, but still the resistor-type DAC is advantageous in some applications, such as programmable DC voltage generator thanks to no requirement for switching.

Fig. 2 Proposed resistor ladder DAC with binary, quaternary and unary combination [15] © IEEE.

#### 2.3 RC Polyphase Filter and Hilbert Filter

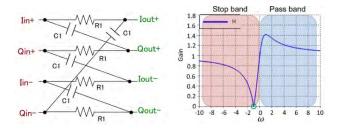

About 20 years ago, the author heard a presentation from Katholieke Universiteit Leuven group at ISSCC; there an RC polyphase filter and its curious behavior were shown. Then he analyzed it using complex signal processing and circulant matrix theories [7, 18, 19].

After several years, an adjunct professor of Gunma University introduced a digital Hilbert filter at his class, and then the author had an intuition that the RC polyphase filter has characteristics as a complex analog Hilbert filter. We found that phase characteristics of the RC polyphase filter have the same as those of the Hilbert filter. Also, its gain characteristics can be approximated as the Hilbert filter; as its order becomes higher, its gain characteristics become closer to the ideal Hilbert filter (Fig. 3)[20].

As far as the author investigated, the RC polyphase filter can be the best approximated to the Hilbert filter, compared to other complex analog filters.

Fig. 3 First-order RC polyphase network (left) and its gain characteristics (right) [20] © IEEE.

2.4 Explicit Transfer Function Derivation of High-Order RC Polyphase Filter

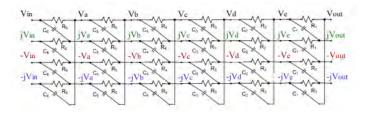

The direct derivation of the transfer function of a high-order RC polyphase filter is very complicated with hand calculation. However, one of Ph. D. course students did it relatively easily [21, 22]. Its point is to denote internal node voltages V, *j*V, -V, -*j*V instead of VI+, VQ+, VI-, VQ- in general form (Fig. 4).

Fig. 4 High-order RC polyphase network [21] © IEEE.

2.5 Resistor and Capacitor Hopfield Network Asynchronous SAR ADCs

The Hopfield network was proposed a long time ago, but it has not been widely used in practice. On the other hand, recently an asynchronous SAR ADC becomes popular. These motivated us to revisit the Hopfield network. Then we came up with an asynchronous SAR ADC with parallel comparators and switched capacitor configuration based on asymmetric Hopfield network [23]. In principle, the original asymmetric Hopfield resistor network can realize an ADC. However, it requires many resistors with giga or even teraorder  $\Omega$ . Hence, we investigated to replace the huge resistors with switched capacitor circuits (Fig. 5).

The proposed N-bit SAR ADC uses N comparators operating in parallel and asynchronously without SAR logic and an internal high-frequency clock. Each lower-bit comparator can operate by look-ahead of its higher-bit comparator results for high speed, and its AD conversion latency is only one or two clock cycles.

Fig. 5 Asymmetric Hopfield network with resistors (left) and switched capacitor circuit (right) [23].

## 3. Waveform Sampling Technologies

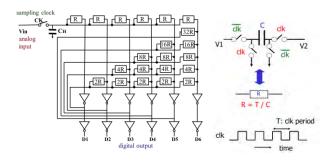

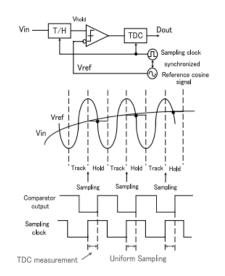

The author was involved in the research for wideband measurement and test systems, and his group investigated wideband waveform sampling technologies (Fig. 6). In this section, their research results are introduced [1].

Fig. 6 Waveform sampling.

## 3.1 Residue Sampling

ADC and DAC are considered as division and multiplication operations. On the other hand, waveform sampling causes spectrum folding which is similar to but different from division operation in frequency domain.

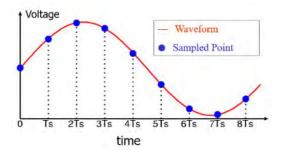

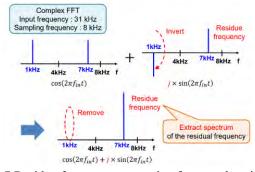

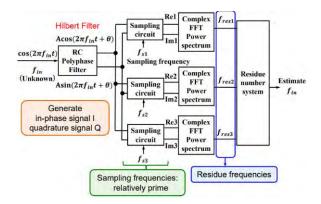

The author's group found that sampling of a complex sinusoidal signal ("cosine + j sine" signal) can realize "frequency division" operation (Fig. 7), and we came up with a high-frequency signal estimation circuit using multiple low-frequency sampling circuits following an analog Hilbert filter (RC polyphase filter) and ADCs (Fig. 8) [24, 25]; here the sampling frequencies are relatively prime.

A sinusoidal signal with high frequency is provided as an input signal. Then cosine and sine signals with the same frequency are generated with an analog Hilbert filter and they are fed into sampling circuits with different and low sampling frequencies. Their analog outputs are AD converted and for their digital outputs, complex FFTs are performed. The input signal frequency can be estimated from the residue frequencies and the residue number theory: the property of one-to-one mapping between the original number and its residue numbers obtained by division of relatively prime numbers is the key.

The frequency estimation resolution becomes finer as the number of FFT data is increased. Also, we investigated its application to AMS IC testing by collaborating with an automatic test equipment (ATE) manufacturer [26].

Fig. 7 Residue frequency generation for complex signal  $\cos(2 \pi t) + j \sin(2 \pi t)$  using sampling [25] © IEEE.

Fig. 8 Residue sampling system [25] © IEEE.

## 3.2 Golden Ratio and Metallic Ratio Sampling

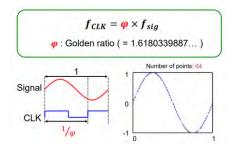

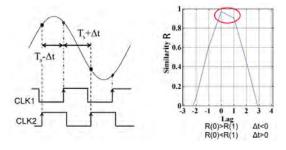

The author learned "waveform missing phenomena" in equivalent-time sampling systems, such as sampling oscilloscopes. Then he tried to find the efficient waveform acquisition condition of the relationship between the sampling clock frequency and the sinusoidal input frequency, which does not cause the phenomena. One of his students found by extensive simulations that the golden ratio (1.6180..) is the most efficient for avoiding the waveform missing phenomena (Fig. 9), and we analyzed its effectiveness in theory and simulation [27].

As its extension, we investigated metallic ratio sampling of the sampling frequency and the input frequency, which also realizes efficient waveform acquisition. Further several interesting properties of the metallic ratio sampling in the view point of the integer theory were found [28].

These results can be utilized in several LSI testing applications such as ADC histogram test [29] because there the sampling clock and the input signal can be controlled intentionally. Also, the golden ratio and metallic ratio sampling techniques can be used for pseudo random signal generation targeted for Monte Carlo simulations [30].

Fig. 9 Golden ratio sampling and uniform distribution of its sampling points [28] © IEEE.

#### 3.3 Non-ideality Analysis of Waveform Sampling

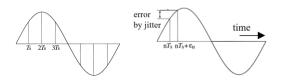

Sampling jitter is a serious problem for wideband waveform acquisition (Fig.10), and high-frequency electronic measurement instrument companies are interested in this issue. Our study on the jitter effect was motivated to realize a high-speed track-hold circuit such as in [31].

Exact noise power ( $P_j$ ) and SNR degradation due to sampling jitter are derived in Eqs. (1), (2) assuming that the jitter ( $\varepsilon$ n) follows the Gaussian distribution of N (0,  $\sigma$ j) and the input is a sinusoidal signal of a frequency *f*in [32, 33].

$$P_j = A^2 \left[ 1 - \exp\left(-2\pi^2 f_{in}^2 \sigma_j^2\right) \right]$$

(1)

$$SNR = -10 \log 2[1 - \exp(-2\pi^2 f_{in}^2 \sigma_j^2)] \text{ [dB]}.$$

(2)

It was impressive that the third author of [33] knew and used the following formulae (3), (4) for derivation of Eqs. (1), (2):

$$E[\cos(\omega \varepsilon_n)] = \exp\left(-\frac{\omega^2 \sigma_j^2}{2}\right)$$

(3)

$$E[\sin(\omega \,\varepsilon_n)] = 0. \tag{4}$$

Notice that in actual sampling circuit, jitter distribution is often not Gaussian.

It is widely believed that sampling jitter effect is the fundamental limitation of the ADC performance. But the author considers that the continuous-time  $\Delta\Sigma$  ADC can overcome this problem; jitter effects for internal ADC are noise-shaped and those for internal DAC can be reduced by jitter insensitive DAC design (such as RF DAC) [34, 35].

Fig. 10 Jitter effects to waveform sampling [33].

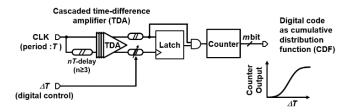

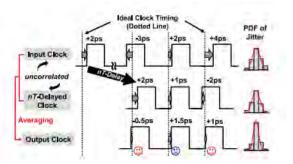

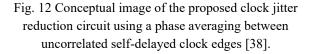

Our jitter measurement circuit and jitter reduction circuit are shown in Figs. 11, 12 respectively [36, 37, 38], developed by their first author.

Fig. 11 Jitter measurement circuit [36] © IEEE.

Further we investigated input-dependent sampling-time error effects in MOS samplers [39] and finite aperture time affects in sampling circuit (Fig. 13) [40] as well as timing error effects for DAC [41] and CMOS ADC nonlinear input capacitance for input differential amplifier array [42]; these were done to understand the AMS circuits and systems well.

Fig. 13 Sampling circuit with aperture time  $\tau$  [40]  $\bigcirc$  IEEE.

#### 4. Nyquist-Rate DAC

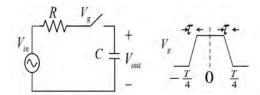

#### 4.1 Relaxation DAC with HPF

The author considers that differentiation or high-pass filter is interesting. Also, he taught two's complement in his basic circuit course. Then he came up with HPF usage for a relaxation DAC (ReDAC) (Fig. 14) and found that it produces with positive and negative polarity output for digital input in two's complement format [43]. The proposed ReDAC with HPF is an extension of the original ReDAC using LPF which generates an analog output with only positive polarity.

Fig. 14 Relaxation DAC with HPF [43].

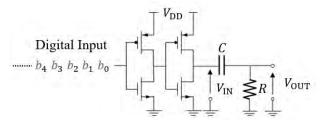

## 4.2 Gray-code Input DAC

When the author started to study ADC design, he realized that Gray-code is frequently used there because it is robust compared to the binary code. Gray code is a binary numeral system where two successive values differ in only one bit, and the conversion between binary-code and Gray-code can be easily realized by XOR circuits (Table 1).

Then he wondered why it is not used for DAC; if it is used, the glitch can be reduced. DAC glitch is a serious problem such as in graphic display applications. He asked the authority of ADC/DAC design, who answered that the Graycode input DAC configuration had not been invented even though many researchers tried.

The author taught at his circuit class that Gray code and binary code are converted using EXOR logic. Then his group came up with three types of Gray code input DACs (current-steering, charge-mode and voltage-mode DACs) which use analog switch matrices equivalent to EXOR (Fig. 15) [44].

| Table 1. Binary code and Gray code |

|------------------------------------|

|------------------------------------|

| Decimal | Binary | Gray |

|---------|--------|------|

| Number  | Code   | Code |

| 0       | 0000   | 0000 |

| 1       | 0001   | 0001 |

| 2       | 0010   | 0011 |

| 3       | 0011   | 0010 |

| 4       | 0100   | 0110 |

| 5       | 0101   | 0111 |

| 6       | 0110   | 0101 |

| 7       | 0111   | 0100 |

| 8       | 1000   | 1100 |

| 9       | 1001   | 1101 |

| 10      | 1010   | 1111 |

| 11      | 1011   | 1110 |

| 12      | 1100   | 1010 |

| 13      | 1101   | 1011 |

| 14      | 1110   | 1001 |

| 15      | 1111   | 1000 |

Fig. 15 Gray-code input current-mode DAC [44] © IEEE.

#### 4.3 DAC Architectures Based on Number Theory

Integers have many interesting properties such as polygonal number theorem and Goldbach conjecture of prime numbers, and we considered to use these for new DAC architectures as curiosity-driven university research: polygonal number DAC and prime number DAC [45]. We showed that each consists of a few current sources, a resistor network, switch arrays and a decoder circuit. Properties of these DACs are positioned between binary and unary DAC ones.

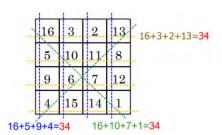

4.4 DAC Linearity Improvement Algorithm With Unit Cell Sorting Based on Magic Square

The author enjoyed introductory mathematical books which describe about Magic Square (Fig. 16), Latin Square and Knight Tour. These were intellectually interesting but their effective applications were not found. Then he considered whether they can be applied to AMS IC design; this is curiosity-driven research. We proposed to use Magic Square, Latin Square and Euler Knight Tour as unit cell selection order algorithms of 2D pseudo random number sequences to cancel systematic mismatch effects among unit cells of a unary DAC and improve its linearity (Fig. 17) [46, 47, 48].

Fig. 16 4x4 Magic square and its constant sum characteristics.

Fig. 17 Magic square layout of unit cells for a unary DAC which cancels their linear/quadratic gradient errors

We also investigated an algorithm called 3-stage current sorting in half-unary weighted current cells to improve the linearity of a current-steering DAC [49].

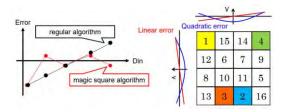

4.5 Unit Cell Mismatch Scrambling Method for High-Resolution Unary DAC based on Virtual 3D Layout We proposed a unit cell mismatch scrambling method for a high-resolution unary DAC based on virtual 3D layout, to improve its Spurious Free Dynamic Range (SFDR) [50]. This can be implemented with simple interconnections and scrambling circuits, compared to that based on the 2D layout.

It is to care for the static characteristics mismatches using the Dynamic Element Matching (DEM) for the unary DAC. We consider here the signal bandwidth of the DAC is from DC to half of the sampling frequency or higher frequency, so that the DEM technique only needs to spread the spectrum of the spurious tones caused by the mismatches in the entire signal band uniformly without need for mismatch shaping; this is called as mismatch scrambling. However, direct implementation circuit of such mismatch scrambling for the high-resolution unary DAC becomes complicated. We investigated a more hardware efficient method by considering a virtual 3D case, considering X-, Y- and Zdecoders (Fig. 18).

The author came up with this idea from magic cube (or 3D magic square) and an intuition that logic of binary-to-thermometer decoder circuit has some regularity.

Fig. 18 X, Y, Z-decoders and unit cells with virtual 3D layout for 6-bit unary DAC [50].

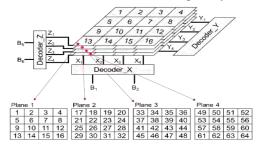

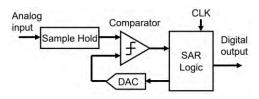

## 5. Successive Approximation Register Analog-to-Digital Converter (SAR ADC)

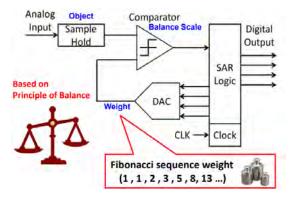

We considered that some redundancy of the SAR ADC (Fig. 19) can relax the requirements for its internal component requirements; there the error is corrected digitally without its measurement. Then the overall performance of the circuit can be improved. The redundancy can be classified into two categories:

(i) Operation redundancy (temporal redundancy): If operation, such as number of SAR steps has some redundancy, the overall AD conversion time can be reduced as well as its reliability is improved.

(ii) Circuit redundancy (spatial redundancy): If redundant hardware, such as multiple SAR comparators is used in an SAR ADC, its overall conversion time can be smaller.

We have investigated both of them. It would be interesting that quantum computer needs redundancy and error correction.

5.1 General SAR ADC Algorithm with Operation Redundancy and Digital Error Correction

We generalized the algorithm for SAR ADCs with overlapping steps that allow comparison decision errors (due to, such as DAC incomplete settling and sample-hold circuit incomplete settling) to be digitally corrected [51]. We generalized this non-binary search algorithm, and clarified which decision errors can be digitally correct. The algorithm requires more SAR ADC conversion steps than a binary search algorithm, but the sampling speed of an SAR ADC using this algorithm can be faster than that of a binary-search SAR ADC; this is because the latter must wait for the settling time of the DAC and the sample-hold circuit inside the SAR ADC.

Fig. 19 SAR ADC configuration [51].

## 5.2 Fibonacci-Sequence Weighted SAR ADC

The author learned from an introductory number theory book that a Fibonacci sequence has many interesting properties and even now new ones are being found. It is widely applied successfully to many areas. Then we considered to apply it to an operation redundancy SAR ADC algorithm. The Fibonacci sequence is defined as follows:

Definition (n=0,1,2,3...)

$$F_0 = 0$$

$F_1 = 1$

$F_{n+2} = F_n + F_{n+1}$

Fibonacci number

$0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55 ...$

Fibonacci sequence weighted SAR approximates the redundant SAR ADC of the radix 1.6 with integer weights, using digital error correction (Fig. 20). Then we found that it is well balanced and fast operation configuration when the settling time of the internal DAC is taken care of. The beautiful characteristics of its "error correction range" were shown. Also, several related results were found [52, 53].

Fig. 20 Fibonacci-sequence weighed SAR ADC.

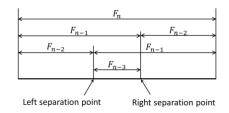

5.3 Fibonacci Sequence Weighted SAR ADC as Fibonacci Section Search

The author learned the Fibonacci section search algorithm (Fig. 21) and had an intuition that this is related to the Fibonacci sequence weighted SAR ADC. The Fibonacci section search algorithm is used for finding effectively the extreme value of the unimodal function. Then we found the equivalence between the Fibonacci sequence weighted SAR ADC and the SAR ADC based on the Fibonacci section search algorithm using the unimodal function obtained by the absolute value of the difference between the ADC input voltage and the internal DAC output [54].

5.4 Fibonacci Sequence Weighted DAC

We came up with also Fibonacci sequence weighted DAC using R-R resistor networks (Fig. 22) [55]; their termination resistors are important. This can be used inside the Fibonacci sequence weighted SAR ADC.

Fig. 22 Fibonacci-sequence weighted DAC [55] © IEEE.

5.5 Pseudo Silver Ratio Weighted SAR ADC

It is well known that when the binary number is 1-bit leftshifted, it is equivalent to multiplication by 2. It is interesting that when it is represented with radix of  $\sqrt{2}$ , 2-bit left-shift is equivalent to multiplication by 2 and 1-bit left-shift is to multiplication by  $\sqrt{2}$ .

The sliver ratio ( $\sqrt{2}$ ) is popular especially in Japanese cultures and one of the students considered the (pseudo) silver ratio weighted SAR ADC and found: this method can realize high speed SAR AD conversion when taking account into the internal DAC incomplete settling and using two internal clocks of different periods [56].

Notice that the pseudo silver ratio SA weights are given by

1, 1, 1, 2, 2, 4, 4, 8, 8, 16, 16, 32, 32, 64, 64, 128, 128 ...,

while the binary ones are

1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, ...

5.6 Binary SAR ADC with Three Comparators and Digital Error Correction

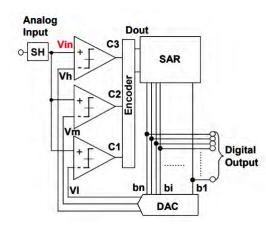

One of research associates invented an SAR ADC algorithm using three comparators operating in parallel, instead of just one as in conventional SAR ADCs (Fig. 23) [57, 58, 59]; this is classified into the circuit redundancy SAR ADC. This comparator redundancy enables higher resolution, potentially faster operation, higher reliability and comparator-error correction. We investigated and derived its error-correction algorithm.

Fig. 23 SAR ADC with three comparators [57].

We investigated the design method of an SAR ADC with redundant circuit (two or three comparators) and redundant number of steps, together with digital error correction [60, 61]. Their error correction ranges were clarified. This is the generalization of our previous SAR ADC with 3 comparators but without step redundancy and the one with redundant number of steps using one comparator.

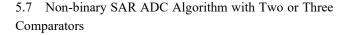

5.8 Design for Testability That Reduces Linearity Testing Time of SAR ADCs

We developed an SAR ADC chip whose SA weights and number of steps are programmable [62]. As its application we came up with design-for-testability (DFT) of SAR ADC that significantly reduces the testing time of its DC linearity with the ramp input signal (Fig. 24). There are only a limited number of successful ADC DFTs, and this is our trial.

Fig. 24 Operation of SAR ADC with DFT ; number of SA steps can be reduced from 4 to 2 in DC linearity test mode by preadjusting the reference voltage corresponding to the known value of the analog input Vin [62].

## **Remarks:**

(i) Other testing related technologies of the SAR ADC with redundancy are discussed in [63, 64].

(ii) Non-binary two-comparator charge-sharing SAR ADC with digital compensation for comparator offset effects is shown in [65].

(iii) We should notice that single-comparator SAR ADC with operation redundancy increases the number of steps so that the dynamic power consumption increases compared to the binary one without redundancy.

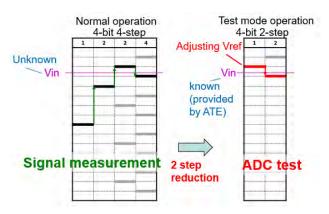

## 6. Time-Interleaved ADC

6.1 Explicit Analysis of Channel Mismatch Effects in Time-Interleaved ADC Systems

The author was involved in an ultra-high-speed ADC research project and reviewed several related papers in Hewlett Packard Journals; one of them was about time-interleaved ADC issues, which inspired him a lot.

A time-interleaved ADC system is an effective way to implement a high-sampling-rate ADC with relatively slow circuits (Fig. 25). In the system, several channel ADCs operate at interleaved sampling times as if they were effectively a single ADC operating at a much higher sampling rate. However, mismatches such as offset, gain, bandwidth mismatches among channel ADCs as well as timing skew of the clocks distributed to them degrade SNDR of the ADC system as a whole. We analyzed their effects in time and frequency domains [66].

#### **Remarks:**

- (i) Linearity mismatch issues are described in [67, 68].

- (ii) Notice that the time-interleaved ADC architecture is used for low-power in consumer electronics as well as high-speed-sampling in measurement instruments.

- (iii) We investigated a bandwidth-interleaved DAC [69].

- (iv) We learned that multi-path (such as time-interleaved, bandwidth interleaved and I, Q-path) and multi sampling clocks in AMS circuits have mismatch problems.

Fig. 25 Time-interleaved ADC [66] © IEEE.

6.2 Digital Compensation Method for Timing Mismatches in Time-Interleaved ADC

The most serious mismatch effect for a wideband timeinterleaved ADC is the timing skew among channel ADCs. Many compensation methods for it have been proposed which have their own advantages and disadvantages. We targeted for ATE system applications and there its digital calibration is desirable instead of analog one. Then we came up with combining correlation method and fine-delay digital filter for its calibration (Fig. 26) [70].

We use cross-correlation among channel ADC outputs to detect channel timing skew, and do successiveapproximation timing adjustments using our proposed linear-phase-digital delay filter to compensate for the timing skew. It was found that using multi-tone input signals with cross-correlation of outputs provided a more robust way of detecting timing skew than using a single tone.

Fig. 26 Cross-correlation for timing skew detection in twochannel interleaved ADC [70] © IEEE.

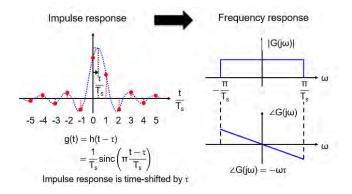

#### 6.3 Digital Filter for Fine Time Delay

We came up with the idea of an FIR digital filter for fine time delay adjustment, by considering the *sinc* function sampling in time domain (Fig. 27). Our digital filter can set its group delay with the arbitrary fine time resolution while it maintains the linear phase characteristics [71, 72]; this can be used such as for the timing skew adjustment of the timeinterleaved ADC sampling clocks described above.

## 7. Time-to-Digital Converter (TDC)

Time domain analog circuits such as TDCs are now popular at international conferences in AMS circuit and system area. However, notice that handling the circuit dynamics (timing, bandwidth, slew-rate) is often difficult and troublesome, compared to the voltage signal handling circuit. Also notice that TDCs have been used especially in ATE systems for timing measurement in practice.

Fig. 27 Sampling timing shift can maintain the linear phase characteristics. Impulse response, and gain, phase [71] © IEEE.

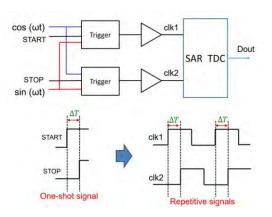

## 7.1 SAR TDC with Trigger Circuit

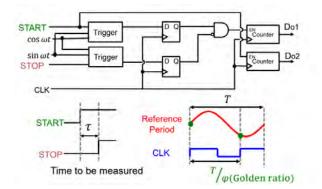

There are many interesting analog circuits for electronic measurement instruments. A long time ago, Tektronix presented a paper about the trigger circuit in an oscilloscope in an international conference on measurement technologies (Fig. 28). Then later, a TDC became popular and the author came up with its application to an SAR TDC (Fig. 29).

Using the trigger circuits, the rising-edge timing difference between two input timing signals can be held. This enables the SAR TDC to measure the timing when two timing inputs are single-shot as well as repetitive two clocks [73].

It was pointed out at an international conference that an oscillator consumes some amount of power. However, for multi-channel usage of TDCs, it can be shared among them.

Fig. 28 Trigger circuit [73] © IEEE.

Fig. 29 SAR TDC with trigger circuits [73] © IEEE.

#### 7.2 Integral-type TDC

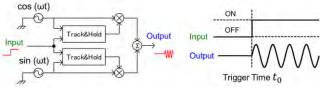

We came up with an integral-type TDC, inspired by an integral-type ADC was investigated (Fig. 30) [74]. It can achieve fine time measurement resolution as its measurement time becomes longer and it does not need delay lines. It employs two counters and a repetitive timing signal with a stable frequency clock as well as external reference sine and cosine signals. The input timing difference is measured by a statistical Monte Carlo method.

We found that the golden-ratio relationship between the reference sine/cosine signal frequency and the sampling clock frequency is desirable [75, 76].

Fig. 30 Integral-type TDC with trigger circuits [74] © IEEE.

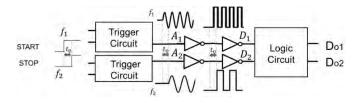

7.3 TDC Using Two Oscillators with Different Frequencies

As modification of the integral-type TDC, we came up with TDC architectures using two asynchronous oscillators with different frequencies [76]; each starts oscillation with different frequencies from the rising timing of the corresponding input timing signal. By counting their oscillation start phase difference using digital counters, a highly linear stable TDC can be realized.

We came up with two architectures using this principle: analog centric one and digital centric one. The analog centric one uses oscilloscope trigger circuits and the digital centric one uses ring oscillators. For analog centric one, its operation is stable but two external asynchronous sine signals are required (Fig. 31). For digital centric one, all TDC circuits including the calibration can be implemented with full digital circuit.

Fig. 31 Analog centric TDC using two oscillators with different frequencies [76] © IEEE.

## 7.4 Residue Arithmetic TDC and Gray code TDC

We came up with a TDC architecture with residue arithmetic architecture from the motivation of applying the number theory to the AMS circuit design [77]. It can reduce the hardware and power significantly compared to a flash type TDC while keeping comparable performance. But later it was found that it generates a glitch.

Then we came up with a glitch-free TDC based on Gray code, which is an improved version of the residue arithmetic TDC (Fig. 32) [78]. It also keeps advantages of the residue arithmetic TDC.

Fig. 32 Gray-code TDC architecture in 6-bit case [78] © IEEE.

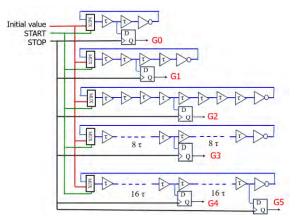

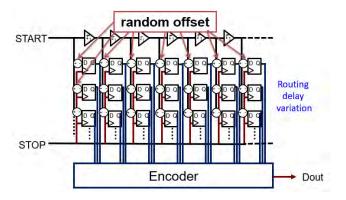

## 7.5 Stochastic TDC Architecture

Proactive use of variations leads to fine time resolution TDC with full digital circuit was investigated. The author had some knowledge of both the TDC linearity self-calibration with the histogram method and the stochastic TDC. Then he came up with combining them (Fig. 33), and the invented TDC architecture has the following: (1) Encoder circuit that ensures monotonic characteristics. (2) Self-calibration circuit with the histogram method for linearity improvement. (3) Stochastic architecture for fine time resolution with proactive use of MOSFET characteristics and routing variations [79, 80, 81].

Fig. 33 Stochastic TDC with linearity self-calibration [79] © IEEE.

7.6 TDC Linearity Calibration with Metallic Ratio Equivalent-Time Sampling

We implemented a linearity self-calibration TDC with the histogram method using an analog FPGA. This is a foreground calibration, where the normal operation is stopped, the circuit itself measures its own error and then it is compensated by the circuit itself. We performed its experiment, but its linearity accuracy was saturated even if a long calibration time was taken. At that time, its reason was not clear. Later we came up with usage of the metallic ratio sampling, which was successful [82].

## 7.7 ADC Architecture Using TDC

The first author in [83] developed an ADC architecture using TDC for ATE applications (Fig. 34). Since a flash-type TDC is realized with full digital circuits, this ADC can be implemented with mostly digital circuits, which is suitable for fine CMOS implementation. In other words, this ADC performance becomes better as the CMOS technology becomes advanced even though the supply voltage is reduced. This demonstrated that time domain analog signal processing is suitable for fine CMOS technology.

Also note that this ADC performs *non-uniform* sampling because the sampling timing depends on the input voltage value, and digital signal processing to convert *non-uniform* sampling data to *uniform* one is required.

Fig. 34 Time-domain ADC architecture and its operation. It employs a TDC and performs non-uniform sampling [83].

## 8. ΔΣ ADC, DAC, TDC and DC-DC Converter

The author has a strong belief that  $\Delta\Sigma$  techniques are applicable to many fields, which always lead to success.

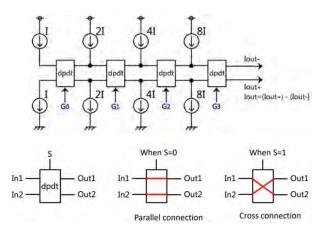

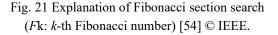

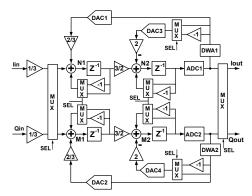

8.1 Complex Bandpass  $\Delta\Sigma$ AD Modulator Without I, Q-Path Crossing Layout and Complex BP DWA Algorithm

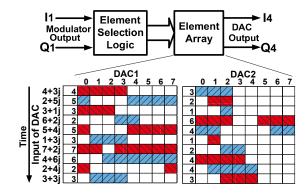

We have designed, fabricated and measured a second-order multibit switched-capacitor complex bandpass  $\Delta\Sigma AD$ modulator which had our new architecture and algorithm [84, 85]. We came up with a complex bandpass filter structure in the forward path with I, Q dynamic matching for the reduction of mismatches between I and Q paths (Fig. 35) [86]. Also we came up with a complex bandpass dataweighted averaging (DWA) algorithm to suppress nonlinearity effects of multibit DACs in complex form to achieve high accuracy (Fig. 36) [87]. The chip employed both of them to evaluate their effectiveness.

Fig. 35 Architecture of our complex bandpass  $\Delta\Sigma AD$ modulator [86].

Fig. 36 Explanation of our complex bandpass DWA algorithm. The unit current cells in the ON state are filled in red for a real part (I-path) and in blue for an imaginary part (Q-path), when the complex input data are sequentially given by 4+3j, 2+5j, 3+j, 6+2j, ... [87].

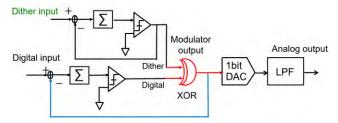

8.2 Limit Cycle Suppression Technique Using Digital Dither in  $\Delta\Sigma$  DA Modulator

We came up with a digital dither technique to suppress limit cycles in a  $\Delta\Sigma$  DA modulator [88]. It uses an XOR gate at the modulator output and the digital dither is generated by another  $\Delta\Sigma$ D modulator. The resolution of the DAC following the modulator is 1-bit (instead of multi-bit) thanks to XOR gate usage, and the overall SNDR does not degrade because the dither is added at the output and hence it is noise-shaped (Fig. 37). Notice that limit cycles are usually not observed in in a  $\Delta\Sigma$  AD modulator due to the device noise inside the AD modulator.

Fig. 37  $\Delta\Sigma$  DA modulator with digital dither [88].

8.3 Phase Noise Measurement Techniques Using  $\Delta\Sigma$  TDC It was demanded from industry that short-time testing of phase noise without spectrum analyzer is required at mass-production shipping stage.

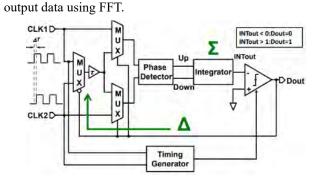

Then we came up with a technique for measuring phase noise of a clock using a  $\Delta\Sigma$  TDC (Fig. 38) [89]. It can be implemented with simple circuitry, due to the following: (i) Clock under test (CUT) is a repetitive signal. (ii) Time resolution with CUT and reference clock can be finer by using longer measurement time with the  $\Delta\Sigma$  TDC. (iii) Phase noise power spectrum can be calculated from the  $\Delta\Sigma$  TDC

Fig. 38  $\Delta\Sigma$  TDC configuration [89] © IEEE.

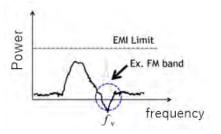

8.4 Band-Select Noise Spread Spectrum Clocking We investigated an  $\Delta\Sigma$  TDC and then as its duality, one of students simulated a  $\Delta\Sigma$  digital-time converter (DTC). We observed its simulation results in frequency domain and came up with usage as band-select spread spectrum clock for DC-DC converters [90]. This technique can exclude the noise spectrum spread such as in AM, FM radio bands (Fig. 39). Later its several extensions have been investigated by leading of a visiting professor of Gunma University [91].

Fig. 39 Band-select spectrum spread [90].

## 9. Dynamic Element Matching Technologies

It was pointed out by an industry researcher that "multi-bit" usage is mandatory for low-power  $\Delta\Sigma$ AD modulator, because the operational amplifier slew-rate requirement is significantly relaxed. However, the multi-bit DAC has some nonlinearities in the feedback path, which degrade the overall SNDR of the  $\Delta\Sigma$  ADC if no care is taken. Then we investigated several digital signal processing algorithms to suppress the multi-bit DAC nonlinearity effects, which is one of the digitally-assisted analog technologies.

We developed various DWA algorithms:

Muti-BP  $\Delta\Sigma$  ADC DWA algorithms [92], Second-order LP DWA algorithms [93, 94], Complex single-BP DWA algorithm [87], Complex multi-BP DWA algorithms [95], DWA algorithms for BP  $\Delta\Sigma$  DAC with ternary unit cells

[96], DWA and self-calibration algorithms of multi-bit  $\Delta\Sigma$  TDC [97, 98].

Here are some comments:

(i) The DWA algorithm with 1<sup>st</sup>-order noise-shaping of DAC nonlinearities can be implemented with simple hardware, whereas the one for the second-order is complicated; this is valid for all DWA algorithms of the second-order reported up-to now.

(ii) Two DACs are used in a complex BP modulator and its DWA algorithm utilizes cross-coupled order selection of unit cells in two DACs (Fig. 35) [87, 95].

(iii) As far as we know, we are the first for development of the multi-bit  $\Delta\Sigma$  TDC DWA algorithm [97, 98].

(iv) To our knowledge, there is no systematic method for development of DWA algorithms [99].

(v) Dynamic matching technique can be also applied to a I, Q-path of a transmitter circuit [100].

## 10. Other Circuits

10.1 Folding/Interpolation ADC and Digital Error Correction Algorithm

The author was involved in the development of a high-speed 6-bit ADC using SiGe Hetero-Junction Bipolar Transistor (HBT) for measuring instrument applications [101]. The folding/interpolation architecture is suitable for ADC design with HBT, which employs an analog encoding signal processing.

We also investigated its digital error correction algorithms by finding out very small redundancy [102]. The relationships between error correction and input signal frequency were clarified. The lower bits obtained by the interpolation circuit with redundancy correct the higher bits by the folding circuits.

Later the author realized that this is common for many digital error correction algorithms of various ADCs and that this is similar to a digital adder where lower bits are calculated first and their generated carries are propagated to higher bits.

10. 2 Background Self-Calibration Algorithm for Pipelined ADC Using Split ADC Scheme

We investigated ADC self-calibration technologies due to the industry demand. The background calibration uses indirect error measurements and an adaptive signal processing algorithm; it is performed during normal operation time. In other words, no calibration time is required. All of these operations are done by the circuit itself without help of the circuit user outside.

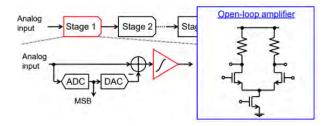

As one of them we investigated a background calibration algorithm for a pipelined ADC with an open-loop amplifier using a split ADC structure [103]. The open-loop amplifier is employed as a residue amplifier in the first stage of the pipelined ADC to realize low power and high speed (Fig. 40). However, the residue amplifier as well as the DAC suffer from gain error and non-linearity, and hence they need calibration. We investigated the split ADC structure for its background calibration with fast convergence.

Fig. 40 Pipeline ADC using open-loop amplifier [103].

10.3 Analysis and Design of Operational Amplifier Stability Based on Routh-Hurwitz Stability Criterion Control theory is basis of analog circuit design. Bode chart based on Nyquist stability criterion is widely used for operational amplifier design. But the author wondered why Routh-Hurwitz stability criterion was not used in circuit design, and finally realized that many of AMS circuit designers did not know it correctly; this fact was very

Then we investigated to use Routh-Hurwitz stability criterion in addition to Nyquist one for analysis and design of the operational amplifier stability, when its small equivalent circuit is derived; this can lead to explicit stability condition derivation for operational amplifier circuit parameters, and this is effective especially for multistage operational amplifiers [104].

## 10. 4 MOS Reference Current Source

surprising to the author.

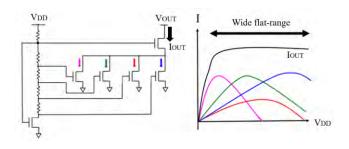

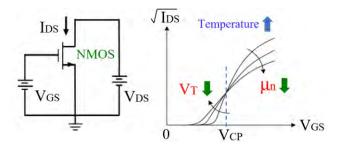

During the author's lecture about CMOS analog circuit to his laboratory members, he assigned several modifications of current sources and one of students showed her simulation results, which was the design improvement of the constant current source (peaking current mirror), originally invented by Nagata Minoru in 1966 (Fig. 41 (a)). Also, several researchers in industry suggested MOS drain current temperature characteristics with respect to the gate voltage (Fig. 41 (b)).

We applied these to MOS reference current source circuits insensitive to supply voltage and temperature [105, 106, 107, 108]. These demonstrated that there are still analog circuit design challenges with a small number of MOS transistors.

(a) For power supply insensitivity.

(b) For temperature insensitivity.

Fig. 41 Investigated MOS reference current source [108] © IEEE.

## 10. 5 AMS Circuit and System Testing Technologies

AMS circuit and system testing technologies are important but their researchers are not so many in universities. Then we have been engaged in the research for them by collaborating with industry [109-124]. These are at the boundary between AMS circuit and LSI testing technologies. Also, Physically Unclonable Function (PUF) has been investigated by applying the TDC linearity selfcalibration method [125].

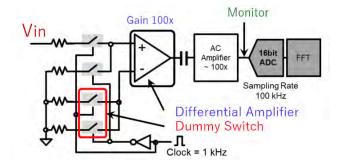

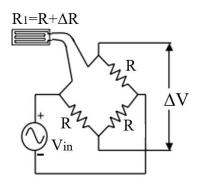

10.6 DC-AC Conversion Technique for Very Small DC Voltage

The author experienced two industry-collaboration research projects with two different companies independently. Both are for very small DC voltage measurement; one is that for analog IC related small voltage/current with DC-AC conversion (Fig. 42) [122, 123, 124] and the other is that for strain measurement using strain gauge (Fig. 43) [126]. Both research associates used the DC-AC conversion technique and both were successful. We recognized that in general this technique is useful for very small DC voltage measurement with high accuracy by suppressing the low-frequency noise effects.

Fig. 42 DC-AC conversion circuit [124] © IEEE.

Fig. 43 Bridge circuit with strain gauge [126].

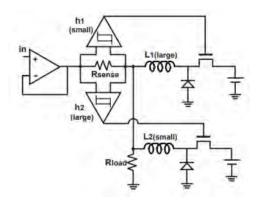

10. 7 Power Electronics Circuits

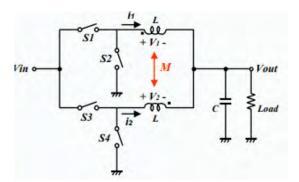

We consider that power electronics circuits play an important role worldwide, and we have been engaged in their study with our research associates: DC-DC converter [127-130], EMI reduction [131, 132], charge pump circuit [133, 134, 135], measurement technique [136], energy harvest [137], envelope tracking power supply (Fig. 44) [138], coupled inductor analysis (Fig. 45) [139], digital PWM generator [140] and IGBT gate driver [141].

10. 8 Floating-Point Digital Arithmetic Circuit based on Taylor-Series Expansion

The author realized that Taylor-series expansion has its conversion region; for some functions, it is very wide while for others, it is limited. Then we considered to apply it to some floating-point digital arithmetic circuits for good tradeoff among memory size, required numbers of additions/subtractions/multiplications, and computing accuracy [142, 143].

Fig. 44 Envelope tracking power supply circuit [138] @IEEE.

Fig. 45 Two-phase coupled-inductor buck converter [139].

10. 9 Research Results Led by Research Associates

There are also some research results led by visiting professors and researchers as well as Ph. D. course students in the author's lab: device modeling [144-147], laterally diffused MOS (LDMOS) device [148, 149, 150], analog filter [151-154], sensor [155], neural network [156], wireless power transmission [157], computer fluid dynamics [158] and distancing-free mask [159, 160].

## 11. Conclusion

This paper has reviewed the author's group research achievements in AMS circuit and system area with the introduction of thinking way and research motivation. Thanks to many excellent research collaborators and students, they cover wide range of areas such as algorithms, circuits, systems, modeling, devices, and testing. Since some of them are algorithm-oriented and technology-independent, hopefully they can live a long time in digital exploding society. This paper is closed by remarking that teaching students at classes as well as discussions with researchers are very helpful for new ideas.

## Acknowledgments

The author would like to thank all of his group members and research associates who have contributed the research mentioned in this paper. This work was supported by JSPS KAKENHI Grant Number 21K04190 and 21KK0080.

#### References

[1] H. Kobayashi, *et. al.*, "Challenges for Waveform Sampling and Related Technologies," IEEE International Conference on Solid-State and Integrated Circuit Technology, Oct. 2022.

[2] H. Kobayashi, *et. al.*, "Analog/Mixed-Signal Circuit Design in Nano CMOS Era," IEICE Electronics Express, 2014.

[3] H. Kobayashi, *et. al.*, "Classical Mathematics and Analog/Mixed-Signal IC Design," IEEE International Conference on ASIC, Oct. 2021.

[4] H. Kobayashi, *et. al.*, "Unified Methodology of Analog/Mixed-Signal IC Design Based on Number Theory," IEEE International Conference on Solid-State and Integrated Circuit Technology, Nov. 2018.

[5] H. Kobayashi and A. Kuwana, "Study of Analog-to-Digital Mixed Integrated Circuit Configuration Using Number Theory," Science Impact Ltd, Impact, Vol. 2022, No. 3, pp. 9-11, June 2022.

[6] H. Kobayashi, *et. al.*, "Modeling Technologies from Analog/Mixed-Signal Circuit Designer Viewpoint," IEEE Electron Devices Technology and Manufacturing, March 2022.

[7] H. Kobayashi, et. al., "Analog/Mixed-Signal/RF Circuits for Complex Signal Processing," IEEE International Conference on ASIC, Oct. 2019.

[8] H. Kobayashi, *et. al.*, "An Active Resistor Network for Gaussian Filtering of Images," IEEE Journal of Solid-State Circuits, Vol.26, No.5, pp.738-748, May 1991.

[9] T. Matsumoto, *et. al.*, "Vision Chip (I) – Analog Image Processing Neuro Chip," Proceedings of IEICE, Vol.76, No.7, pp.783-791, July 1993. [10] T. Matsumoto, *et. al.*, "Vision Chip (II) – Analog Image Processing Neuro Chip," Proceedings of IEICE, Vol.76, No.8, pp.851-858, Aug. 1993. [11] T. Matsumoto, *et. al.*, "Spatial Versus Temporal Stability Issues in

Image Processing Neuro Chips," IEEE Trans. Neural Networks, July 1992. [12] H. Kobayashi, *et. al.*, "Two-Dimensional Spatio-Temporal Dynamics of Analog Image Processing Neural Networks," IEEE Trans. Neural Networks, Vol.6, No.5, pp.1148-1164, May 1995.

[13] M. Chiba, *et. al.*, "Spatial and Temporal Dynamics of Non-Uniform Active Resistor Networks," IEEE International Conference on Solid-State and Integrated Circuit Technology, Oct. 2022.

[14] H. Kobayashi, et. al., "Back to the Analog Neural Network and Linear Circuit Theory," IEEE 15th International Conference on ASIC, Oct. 2023.

[15] H. Hirai, et. al., "Digital-to-Analog Converter Configuration Based on Non-uniform Current Division Resistive-Ladder", International Technical Conference on Circuits/Systems, Computers and Communications, June 2021.

[16] M. Hirai, et. al., "Nonlinearity Analysis of Resistive Ladder-Based Current-Steering Digital-to-Analog Converter," International SOC Design Conference, Oct. 2020.

[17] M. Hirai, *et. al.*, "Systematic Construction of Resistor Ladder Network for N-ary DACs," IEEE International Conference on ASIC, Oct. 2019.

[18] H. Kobayashi, *et. al.*, "Explicit Transfer Function of RC Polyphase Filter for Wireless Transceiver Analog Front-End," IEEE Asia-Pacific Conference on ASICs, Aug. 2002.

[19] Y. Niki, et. al., "Flat Passband Gain Design Algorithm for 2nd-order RC Polyphase Filter," IEEE International Conference on ASIC, Nov. 2015.

[20] Y. Tamura, *et. al.*, "RC Polyphase Filter as Complex Analog Hilbert Filter," IEEE International Conference on Solid-State and Integrated Circuit Technology, Oct. 2016.

[21] M. T. Tri, *et. al.*, "Design of Sixth-Order Passive Quadrature Signal Generation Network Based on Polyphase Filter," IEEE International Conference on Solid-State and Integrated Circuit Technology, Nov. 2020.

[22] M. T. Tran, *et. al.*, "Pass-band Gain Improvement Technique for Passive RC Polyphase Filter in Bluetooth Low-IF Receiver using Two RC Band-stop Filters," Advanced Engineering Forum, Vol. 38, pp.192-205, Nov. 2020. [23] X. Bai, et. al., "Asynchronous Capacitive SAR ADC based on Hopfield Network," IEICE Electronics Express, Vol. 19, No. 18, Pages 20220276, Sept. 2022.

[24] H. Kobayashi *et. al.*, "Challenges for Waveform Sampling and Related Technologies," IEEE International Conference on Solid-State & Integrated Circuit Technology, Oct. 2022.

[25] Y. Abe, *et. al.*, "Frequency Estimation Sampling Circuit Using Analog Hilbert Filter and Residue Number System," IEEE International Conference on ASIC, Oct. 2019.

[26] S. Katayama, et. al., "Application of Residue Sampling to RF/AMS Device Testing," IEEE Asian Test Symposium, Nov. 2021.

[27] Y. Sasaki, *et. al.*, "Highly Efficient Waveform Acquisition Condition in Equivalent-Time Sampling System," IEEE Asian Test Symposium, Oct. 2018.

[28] S. Yamamoto, *et. al.*, "Metallic Ratio Equivalent-Time Sampling: A Highly Efficient Waveform Acquisition Method," IEEE International Symposium on On-Line Testing and Robust System Design, June 2021.

[29] Y. Zhao, *et. al.*, "Revisit to Histogram Method for ADC Linearity Test: Examination of Input Signal and Ratio of Input and Sampling Frequencies," Journal of Electronic Testing: Theory and Applications, Springer, Vol. 38, pp. 21-38, March 2022.

[30] R. Ohta, A. Kuwana, *et. al.*, "Pseudo Random Number Generation Algorithms with Fibonacci Sequence," International Workshop on Post-Binary ULSI Systems, May 2022.

[31] T. Tobari, et. al., "Track / Hold Circuit in GaAs HBT Process," IEICE Trans. Fundamentals, Vol.E80-A, No.3, pp.454-460, March 1997.

[32] H. Kobayashi, et. al., "Aperture Jitter Effects on Wideband Sampling Systems," IEEE Instrumentation and Measurement Technology Conference, May 1999.

[33] H. Kobayashi, *et. al.*, "Sampling Jitter and Finite Aperture Time Effects in Wideband Data Acquisition Systems," IEICE Trans. Fundamentals, Vol. E85-A, No. 2, pp. 335-346, Feb. 2002.

[34] M. Uemori, *et. al.*, "High-Speed Continuous-Time Subsampling Bandpass  $\Delta\Sigma$ AD Modulator Architecture", IEICE Trans. Fundamentals, E89-A, no.4, pp. 916-923, April 2006.

[35] H. Lin, *et. al.*, "Study on Q Factor and Loop Delay Effects om a Continuous-Time Bandpass  $\Delta\Sigma$ AD Modulator," IEICE Trans. Vol.J93-A, No.2, pp.107-118, Feb. 2010.

[36] K. Niitsu, *et. al.*, "CMOS Circuits to Measure Timing Jitter Using a Self-Referenced Clock and a Cascaded Time Difference Amplifier with Duty-Cycle Compensation," IEEE Journal of Solid-State Circuits No. 47, No.11, pp.2701-2710, Nov. 2012.

[37] K. Niitsu, *et. al.*, "A Clock Jitter Reduction Circuit Using Gated Phase Blending Between Self-Delayed Clock Edges," IEEE Symposium on VLSI Circuits, June 2012.

[38] K. Niitsu, *et. al.*, "Design and Theoretical Analysis of a Clock Jitter Reduction Circuit Using Gated Phase Blending Between Self-Delayed Clock Edges," IEICE Electronics Express, 2019.

[39] N. Hayasaka, H. Kobayashi, "Input-Dependent Sampling-Time Error Effects in MOS Samplers," IEICE Trans. Electronics, Vol. E87-C, No. 6, pp.1015-1021, June 2004.

[40] M. Arai, *et. al.*, "Finite Aperture Time Effects in Sampling Circuit," IEEE International Conference on ASIC, Nov. 2015.

[41] H. Kogure, et. al., "Analysis of CMOS ADC Nonlinear Input Capacitance," IEICE Trans. Electron, Vol.E85-C, No.5, pp.1182-1190, May 2002.

[42] N. Kurosawa, et. al., "Sampling Clock Jitter Effects in Digital-to-Analog Converters," Measurement, Vol.31, No.3, pp.187-199, March 2002.

[43] L. Nengvang, *et. al.*, "Relaxation DAC with Positive and Negative Polarity Output using High-Pass Filter," IEICE Electronics Express, Feb. 2023.

[44] R. Jiang, *et. al.*, "Gray-code Input DAC Architecture for Clean Signal Generation," IEEE International Symposium on Intelligent Signal Processing and Communication Systems, Nov. 2017.

[45] X. Bai, *et. al.*, "Derivation of Digital-to-Analog Converter Architectures Based on Number Theory," Journal of Pure and Applied Mathematics, Oct. 2022.

[46] M. Higashino, *et. al.*, "Digital-to-Analog Converter Layout Technique and Unit Cell Sorting Algorithm for Linearity Improvement Based on Magic Square," Journal of Technology and Social Science, Vol.4, No.1, pp.22-35, Jan. 2020.

[47] D. Yao, *et. al.*, "DAC Linearity Improvement with Layout Technique using Magic and Latin Squares," IEEE International Symposium on Intelligent Signal Processing and Communication Systems, Nov. 2017.

[48] D. Yao, *et. al.*, "Segmented DAC Unit Cell Selection Algorithm and Layout/Routing Based on Euler's Knight Tour," IEEJ International Conference on Analog VLSI Circuits, Oct. 2021.

[49] S. N. Mohyar, H. Kobayashi, "Digital Calibration Algorithm for Half-Unary Current-Steering DAC for Linearity Improvement," IEEE International SoC Design Conference, Nov. 2014.

[50] D. Yao, *et. al.*, "Unit Cell Mismatch Scrambling Method for High-Resolution Unary DAC based on Virtual 3D Layout," IEICE Electronics Express, Dec. 2022.

[51] T. Ogawa, *et. al.*, "SAR ADC Algorithm with Redundancy and Digital Error Correction," IEICE Trans. Fundamentals, vol. E93-A, No.2, pp. 415-423, Feb. 2010.

[52] Y. Kobayashi, et. al., "SAR ADC Design Using Golden Ratio Weight Algorithm," International Symposium on Communications and Information Technologies, Oct. 2015.

[53] Y. Kobayashi, H. Kobayashi, "Redundant SAR ADC Algorithm Based on Fibonacci Sequence," Advanced Micro-Device Engineering VI, Key Engineering Materials pp.117-126, 2016.

[54] H. Arai, *et. al.*, "Fibonacci Sequence Weighted SAR ADC as Golden Search SAR ADC as Golden Section Search," IEEE International Symposium on Intelligent Signal Processing and Communication Systems, Nov. 2017.

[55] T. Arafune, *et. al.*, "Fibonacci Sequence Weighted SAR ADC Algorithm and its DAC Topology," IEEE International Conference on ASIC, Nov. 2015.

[56] Y. Kobayashi, et. al., "SAR ADC Algorithm with Redundancy Using Pseudo-Silver-Ratio," IEEJ Trans. Electronics, Information and Systems, Vol. 137, No. 2, pp.222-228, Feb. 2017.

[57] M. Hotta, *et. al.*, "SAR ADC Architecture with Digital Error Correction," IEEJ International Analog VLSI Workshop, Nov. 2006.

[58] M. Hotta, *et. al.*, "SAR ADC Architecture with Digital Error Correction", IEEJ Transactions on Electrical and Electronic Engineering, vol.5, no.6, pp.651-659, Nov. 2010.

[59] A. Hayakawa, *et. al.*, "High Performance Successive Approximation ADC Architecture," IEEJ Electronic Circuit Workshop, March 2006.

[60] T. Ogawa, et. al., "SAR ADC Algorithms with Redundancy – 2-Comparator Case –," IEEJ Electronic Circuit Workshop, March 2008.

[61] T. Ogawa, *et. al.*, "SAR ADC Algorithms with Redundancy – 3-Comparator Case –," IEICE Circuit and System Workshop in Karuizawa, April 2008.

[62] T. Ogawa, *et. al.*, "Design for Testability That Reduces Linearity Testing Time of SAR ADCs," IEICE Trans. Electronics, Vol. E 94-C, no.6, pp.1061-1064, June 2011.

[63] T. Ogawa, et. al., "SAR ADC That is Configurable to Optimize Yield," IEEE Asia Pacific Conference on Circuits and Systems, Dec. 2010.

[64] T. Ogawa, et. al., "Fast Testing of Linearity and Comparator Error Tolerance of SAR ADCs," IEEJ International Analog VLSI Workshop, Nov. 2009.

[65] T. Ogawa, *et. al.*, "Non-binary SAR ADC with Digital Compensation for Comparator Offset Effects," IEICE Trans. Vol. J94-C, No. 3, pp. 68-78, March 2011.

[66] N. Kurosawa, et. al., "Explicit Analysis of Channel Mismatch Effects in Time-Interleaved ADC Systems," IEEE Trans. Circuits and Systems I: Fundamental Theory and Applications, Vol.48, No.3, pp.261-271, Mar. 2001.

[67] N. Kurosawa, et. al., "Channel Linearity Mismatch Effects in Time-Interleaved ADC Systems," IEICE Trans. Fundamentals, Vol. E85-A, No. 4, pp.749-756, April 2002.

[68] K. Asami, "Technique to Improve the Performance of Time-Interleaved A-D Converters with Mismatches of Non-linearity," IEICE Trans. Fundamentals, Vol. E92-A, No.2, pp. 374-380, Feb. 2009.

[69] N. Ishida, *et. al.*, "Frequency Interleaved DAC System Design: Fundamental Problems and Compensation Methods," Proceedings of 8th International Congress on Information and Communication Technology, Lecture Notes in Networks and Systems, Springer, Aug. 2023.

[70] R. Yi, et. al., "Digital Compensation for Timing Mismatches in Interleaved ADCs," IEEE Asian Test Symposium, Nov. 2013. [71] K. Asami, et. al., "Timing Skew Compensation Technique using Digital Filter with Novel Linear Phase Condition," IEEE International Test Conference, Nov. 2010.

[72] K. Asami, *et. al.*, "Digitally-Assisted Compensation Technique for Timing Skew in ATE Systems," IEEE International Mixed-Signals, Sensors, and Systems Test Workshop, May 2011.

[73] Y. Ozawa, *et. al.*, "SAR TDC Architecture with Self-Calibration Employing Trigger Circuit," IEEE Asian Test Symposium, Nov. 2017.

[74] Y. Sasaki, H. Kobayashi, "Integral-type Time-to-Digital Converter," IEEE International Conference on Solid-State and Integrated Circuit Technology, Nov. 2018.

[75] H. Kobayashi, *et. al.*, "Fine Time Resolution TDC Architectures -Integral and Delta-Sigma Types," IEEE International Conference on ASIC, Oct. 2019.

[76] K. Machida, *et. al.*, "Time-to-Digital Converter Architectures Using Two Oscillators with Different Frequencies," IEEE Asian Test Symposium, Oct. 2018.

[77] C. Li, et. al, "Time-to-Digital Converter Architecture with Residue Arithmetic and its FPGA Implementation," International SoC Design Conference, Nov. 2014.

[78] C. Li, H. Kobayashi, "A Glitch-Free Time-to-Digital Converter Architecture Based on Gray Code," IEEJ Trans. EIS, Vol. 136, No. 1, pp. 22-27, Jan. 2016.

[79] S. Ito, *et. al.*, "Stochastic TDC Architecture with Self-Calibration," IEEE Asia Pacific Conference on Circuits and Systems, Dec. 2010.

[80] C. Li, et. al., "Stochastic TDC Architecture with Self-Calibration and its RTL Verification," IEEJ Trans. EIS, Vol. 137, No. 2, pp.335-341, Feb. 2017.

[81] K. Katoh, *et. al.*, "A Small Chip Area Stochastic Calibration for TDC Using Ring Oscillator," Journal of Electronic Testing: Theory and Applications, Vol. 30, Issue 6, pp.653-663, Springer, Dec. 2014.

[82] S. Yamamoto, *et. al.*, "Metallic Ratio Equivalent-Time Sampling and Application to TDC Linearity Calibration," IEEE Transactions on Device and Materials Reliability, Vol. 22, No.2, pp. 142-153, June 2022.

[83] T. Komuro, *et. al.*, "ADC Architecture Using Time-to-Digital Converter," IEICE Trams. Vol. J90-C, No.2, pp.125-133, Feb. 2007.

[84] H. San, *et. al.*, "A Second-Order Multi-bit Complex Bandpass  $\Delta\Sigma$ AD Modulator With I, Q Dynamic Matching and DWA Algorithm", IEICE Trans. Electronics, Vol.E90-C, No.6, pp.1181-1188, June 2007.

[85] H. San, *et. al.*, "A Multibit Complex Bandpass  $\Delta\Sigma$ AD Modulator with I, Q Dynamic Matching and DWA Algorithm," IEEE Asian Solid-State Circuits Conference, Nov. 2006,

[86] H. San, *et. al.*, "Complex Bandpass  $\Delta\Sigma$ AD Modulator Architecture Without I, Q-Path Crossing Layout," IEICE Trans. Fundamentals, E89-A, no.4, pp. 908-915, April 2006.

[87] H. San, *et. al.*, "A Noise-Shaping Algorithm of Multi-bit DAC Nonlinearities in Complex Bandpass  $\Delta \Sigma AD$  Modulators," IEICE Trans. Fundamentals, E87-A, No. 4, pp.792-800, April 2004.

[88] J. Kojima, *et. al.*, "Study on  $\Delta\Sigma$  DA Modulator Performance Improvement Using Digital Dither," IEEJ Trans. EIS. Vol. 136, No. 12, pp. 1767-1772, Dec. 2016.

[89] Y. Osawa, et. al., "Phase Noise Measurement Techniques Using Delta-Sigma TDC," IEEE International Mixed-Signals, Sensors and Systems Test Workshop, Sept. 2014.

[90] R. Khatami, *et. al.*, " $\Delta\Sigma$  Digital-to-Time Converter and its Application to SSCG," IEICE International Conference on Integrated Circuits Design and Verification, Nov. 2013.

[91] Y. Sun, Y. Kobori, *et. al.*, "Pulse Coding Controlled Switching Converter that Generates Notch Frequency to Suit Noise Spectrum", IEICE Trans. Communications, Vol.E103-B, No.11, pp.1331-1340, Nov. 2020.

[92] A. Motozawa, *et. al.* "Multi-Band-Pass  $\Delta\Sigma$  Modulator Techniques and Their Applications," IEICE Trans. Vol. J90-C, No.2, pp.143-158, Feb. 2007.

[93] H. Hagiwara, *et. al.* "DA Converter Circuits Provided with DA Converter of Segment Switched Capacitor Type," Patent Application No.: 11/157,923 (U.S.), Application Date : June 22, 2005.

[94] H. Hagiwara, *et. al.* "A Second-order DWA Algorithm for Multi-bit Lowpass  $\Delta\Sigma$ AD Modulators," IEEJ Electronic Circuit Workshop, June 2004.

[95] M. Murakami, et. al., "I-Q Signal Generation Techniques for Communication IC Testing and ATE Systems," IEEE International Test Conference, Nov. 2016.

[96] J. Kojima, et. al., "DWA Algorithm for Band-Pass  $\Delta\Sigma$  DAC with Ternary Unit Cells," IEEE International Conference on Solid-State and Integrated Circuit Technology, Nov. 2018.

[97] S. Uemori, *et. al.*, "Multi-bit Sigma-Delta TDC Architecture with Improved Linearity," Journal of Electronic Testing: Theory and Applications, Springer, Vol. 29, No. 6, pp.879-892, Dec. 2013.

[98] T. Chujo, *et. al.*, "Timing Measurement BOST with Multi-bit  $\Delta\Sigma$  TDC," IEEE International Mixed-Signal Testing Workshop, June 2015.

[99] H. Kobayashi, *et. al.*, "Performance Improvement of Delta-Sigma ADC/DAC/TDC Using Digital Technique," IEEE International Conference on Solid-State and Integrated Circuit Technology (Nov. 2018).

[100] J. Otsuki, *et. al.*, "Reducing Spurious Output of Balanced Modulators by Dynamic Matching of I, Q Quadrature Paths," IEICE Trans. Electronics, E88-C, no.6, pp.1290-1294, June 2005.

[101] H. Kobayashi, et. al., "A High-Speed 6-bit ADC Using SiGe HBT," IEICE Trans. Fundamentals, Vol. E81-A, No. 3, pp.389-397, March 1998.

[102] H. Kobayashi, *et. al.*, "Error Correction Algorithm for Folding/ Interpolation ADC," IEEE International Symposium on Circuits and Systems, May 1995.

[103] T. Yagi, *et. al.*, "Background Self-Calibration Algorithm for Pipelined ADC Using Split ADC Scheme", IEICE Trans. Electronics, Vol.E94-C, No.7, pp. 1233-1236, July 2011.

[104] J. Wang, *et. al.*, "Analysis and Design of Operational Amplifier Stability Based on Routh-Hurwitz Stability Criterion," IEEJ Trans. EIS, Vol. 138, No. 12, pp.1517-1528, Dec. 2018.

[105] M. Hirano, *et. al.*, "Silicon Verification of Improved Nagata Current Mirrors," IEEE International Conference on Solid-State and Integrated Circuit Technology, Nov. 2018.

[106] M. Hirano, *et. al.*, "Simple Reference Current Source Insensitive to Power Supply Voltage Variation - Improved Minoru Nagata Current Source," IEEE International Conference on Solid-State and Integrated Circuit Technology, Oct. 2016.

[107] T. Feng, *et. al.*, "A Reference Current Source with Cascaded Nagata Current Mirrors Insensitive to Supply Voltage and Temperature," IEEE International Conference on Solid-State and Integrated Circuit Technology, Oct. 2022.

[108] T. Hosono, *et. al.*, "Nagata Current Sources with Self-Bias Configuration Insensitive to Supply Voltage and Temperature," IEEE International Conference on Electrical, Computer and Energy Technologies, Dec. 2021.

[109] H. Kobayashi, *et. al.*, "Analog/Mixed-Signal Circuit Testing Technologies in IoT Era," IEEE International Conference on Solid-State and Integrated Circuit Technology, Nov. 2020.

[110] H. Kobayashi, *et. al.*, "Analog/Mixed-Signal Circuit Testing Technologies in IoT Era," IEEJ Trans. EIS, Vol. 141, No. 1, pp.1-12, Jan. 2021.

[111] H. Kobayashi, "Signal Generation Technologies for Analog/Mixed-Signal IC Testing," IEEE International Conference on ASIC (Oct. 2023).

[112] F. Abe, *et. al.*, "Low-Distortion Signal Generation for ADC Testing," IEEE International Test Conference, Oct. 2014.

[113] D. Iimori, T. Nakatani, *et. al.*, "Summing Node and False Summing Node Methods: Accurate Operational Amplifier AC Characteristics Testing without Audio Analyzer," IEEE International Test Conference, Oct. 2021.

[114] R. Aoki, *et. al.*, "Evaluation of Null Method for Operational Amplifier Short-Time Testing," IEEE International Conference on ASIC, Oct. 2019.

[115] K. Sato, T. Nakatani, *et. al.*, "Low Distortion Sinusoidal Signal Generator with Harmonics Cancellation Using Two Types of Digital Predistortion," IEEE International Test Conference, Oct. 2023.

[116] K. Sato, *et. al.*, "Revisit to Accurate ADC Testing with Incoherent Sampling Using Proper Sinusoidal Signal and Sampling Frequencies," IEEE International Test Conference, Oct. 2021.

[117] K. Sato, T. Nakatani, *et. al.*, "High Precision Voltage Measurement System Utilizing Low-End ATE Resource and BOST," IEEE Asian Test Symposium, Nov. 2022.

[118] P. Sarson, *et. al.*, "A Distortion Shaping Technique to Equalize Intermodulation Distortion Performance of Interpolating Arbitrary Waveform Generators in Automated Test Equipment," Journal of Electronic Testing, Springer, Vol. 34, pp.215-232, June 2018.

[119] D. Iimori, et. al., "SAR Time-to-Digital Converter with 1ps

Resolution for LSI Test System," International Congress on Information and Communication Technology, Lecture Notes in Networks and Systems, Springer, Feb.2023.

[120] T. Komuro, *et. al.*, "A Practical BIST Circuit for Analog Portion in Deep Sub-Micron CMOS System LSI," IEEE International Symposium on Circuits and Systems, May 2005.

[121] Y. Motoki, *et. al.*, "Multi-Tone Curve Fitting Algorithms for Communication Application ADC Testing," Electronics and Communication in Japan: Part 2, Wiley Periodicals Inc.Vol.86, No.8, pp.1-11, Feb. 2003.

[122] G. Ogihara, T. Nakatani, *et. al.*, "Evaluation of High-Precision Nano-Ampere Current Measurement Method for Mass Production," IEEE International Conference on Electronics Circuits and Systems, Nov. 2021.

[123] K. Sato, T. Nakatani, et. al., "Accurate Testing of Precision Voltage Reference by DC-AC Conversion," IEEE Asian Test Symposium, Nov. 2020.

[124] Y. Sasaki, *et. al.*, "Accurate and Fast Testing Technique of Operational Amplifier DC Offset Voltage in  $\mu$ V-order by DC-AC Conversion," IEEE International Test Conference in Asia, Sept. 2019.

[125] K. Katoh, *et. al.*, "A Physically Unclonable Function Using Timeto-Digital Converter with Linearity Self-Calibration and its FPGA Implementation," IEEE International Test Conference in Asia, Sept. 2023.

[126] M. Kono, *et. al.*, "High-Precision Strain Measurement Bridge Circuit with On-Line Compensation for Parasitic Capacitance Effects," IECE Trans. Vol.J91-C, No.3, pp.204-216, March 2008.

[127] S. Wu, *et. al.*, "Transient Response Improvement of DC-DC Buck Converter by a Slope Adjustable Triangular Wave Generator," IEICE Trans. Communications, vol. E98-B, no.2, pp.288-295, Feb. 2015.

[128] M. T. Tran, *et. al.*, "Overshoot Cancelation Based on Balanced Charge-Discharge Time Condition for Buck Converter in Mobile Applications," IEEE International Conference on ASIC, Oct. 2019.

[129] Y. Sekine, S. Katayama, Y. Kobori, *et. al.*, "Multi-Output SEIPC Multiplied Boost Converter with Exclusive Control," IEEE International Conference on ASIC, Oct. 2021.

[130] Y. Kobori, *et. al.*, "Single Inductor Dual Output Switching Converter using Exclusive Control Method," IEEE International Conference on Power Engineering, Energy and Electrical Devices, May 2013.

[131] T. Daimon, *et. al.*, "Spread-Spectrum Clocking in Switching Regulators for EMI Reduction", IEICE Trans. Fundamentals, Vol. E86-A, No. 2, pp.381-386, Feb. 2003.

[132] I. Mori, *et. al.*, "EMI Reduction by Spread-Spectrum Clocking in Digitally-Controlled DC-DC Converters," IEICE Trans. Fundamentals, Vol. E92-A, No.4, pp. 1004-1011, April 2009.

[133] T. Myono, *et. al.*, "Reducing Startup-time Inrush Current in Charge Pump Circuits," IEICE Trans. Fundamentals, vol. E87-A, No. 4, pp.787-791, April 2003.

[134] T. Myono, *et. al.*, "High-Efficiency Charge-Pump Circuits which use a 0.5Vdd-Step Pumping Method," IEICE Trans. Fundamentals, Vol. E86-A, No. 2, pp.371-380, Feb. 2003.

[135] H. Sato and H. Kobayashi, "Dynamic Power Dissipation of Track/Hold Circuit," IEICE Trans. Fundamentals, Vol.83, No.8, pp.1728-1731, Aug. 2000.

[136] N. Tsukiji, *et. al.*, "A Study on Loop Gain Measurement Method Using Output Impedance in DC-DC Buck Converter," IEICE Trans. Communications, Vol.E101-B, No.9, pp.1940-1948, Sep. 2018.

[137] Z. Nosker, *et. al.*, "A Small, Low Power Boost Regulator Optimized for Energy Harvesting Applications," Analog Integrated Circuits and Signal Processing, Springer, Vol. 75, Issue 2, pp. 207-216, April 2013.

[138] A. Kanbe, et. al., "New Architecture of Envelope Tracking Power Amplifier for Base Station," IEEE Asia Pacific Conference on Circuits and Systems, Dec. 2008.

[139] S. A. Wibowo, *et. al.*, "Analysis of Coupled Inductors for Low-Ripple Fast- Response Buck Converter," IEICE Trans. Fundamentals, Vol. E92-A, No.2, pp. 45-455, Feb. 2009.

[140] I. Mori, *et. al.*, "High-Resolution DPWM Generator for Digitally Controlled DC-DC Converters," IEEE Asia Pacific Conference on Circuits and Systems, Dec. 2008.

[141] S. Yamamoto, *et. al.*, "Current-Driven IGBT Gate Driver Circuit Considering Four Operation Regions," International Congress on Information and Communication, Springer (Aug. 2022).

[142] J. Wei, et. al.,"IEEE754 Binary32 Floating-Point Logarithmic

Algorithms based on Taylor-Series Expansion with Mantissa Region Conversion and Division," IEICE Trans. Fundamentals, Vol.E105-A, No.7, pp.1020-1027, Jul. 2022.

[143] J. Wei, *et. al.*, "Floating-Point Inverse Square Root Algorithm Based on Taylor-Series Expansion," IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 68, Issue 7, pp. 2640-2644, July 2021.

[144] H. Aoki and H. Kobayashi, "Self-Heat Characterizations and Modeling of Multi-finger n-MOSFETs for RF-CMOS Applications," IEEE Transactions on Electron Devices. vol.62, no.9, pp.2704-2709, Sept. 2015.

[145] H. Aoki , *et. al.*, "Electron Mobility and Self-Heat Modeling of AlN/GaN MIS-HEMTs with Embedded Source Field-Plate Structures," IEEE Compound Semiconductor Integrated Circuit Symposium, Oct. 2016.

[146] M. Higashino, H. Aoki, *et. al.*, "Study on ON-Resistance Degradation Modeling Used for HCI Induced Degradation Characteristic of LDMOS Transistors," International Conference on Solid State Devices and Materials, Sept. 2016.

[147] Y. Arai, H. Aoki, *et. al.*, "Gate Voltage Dependent 1/f Noise Variance Model Based on Physical Noise Generation Mechanisms in n-Channel Metal-Oxide-Semiconductor Field-Effect Transistors," Japanese Journal of Applied Physics, vol. 54, 04DC10 1-4, Feb. 2015.

[148] J. Matsuda, *et. al.*, "High Reliability and Low Switching Loss Dual RESURF 40 V N-LDMOS Transistor with Grounded Multi-Step Field Plate," Journal of Technology and Social Science, Vol.7, No.1, pp.1-12, Jan. 2023.

[149] J. Matsuda, et. al., "Optimization of High Reliability and Wide SOA 100 V N-LDMOS Transistor," IEEJ Trans. EIS, Vol.140, No.11, pp.1220-1229, Nov. 2020.

[150] J. Matsuda, et. al., "Wide SOA and High Reliability 60-100 V LDMOS Transistors with Low Switching Loss and Low Specific On-Resistance," IEEE International Conference on Solid-State and Integrated Circuit Technology, Nov. 2018.

[151] T. Komuro, *et. al.*, "Total Harmonic Distortion Measurement System for Electronic Devices up to100MHz with Remarkable Sensitivity," IEEE Trans. Instrumentation and Measurement, Vol. 56, Issue 6, pp. 2360 – 2368, Dec. 2007.

[152] M. Takagi, T. Nakatani, *et. al.*, "Design Consideration for LC Analog Filters: Inductor ESR Compensation, Mutual Inductance Effect and Variable Center Frequency," International Congress on Information and Communication Technology, Lecture Notes in Networks and Systems, Springer, Aug. 2023.

[153] T. M. Tran, et. al., "Investigation of Behaviors of Kerwin-Huelsman-Newcomb Filters Using Nichols Charts of Self-Loop Function," IEEE International Midwest Symposium on Circuits and Systems, Aug. 2021.

[154] M. T. Tran, *et. al.*, "Study of Behaviors of Multi-Source Rauch Filters," American Journal of Science & Engineering, Vol. 2, Issue 1, pp. 35-52, April 2021.

[155] S. Wang, M. Z. Hossain, *et. al.*, "Graphene Field-Effect Transistor Biosensor for Detection of Biotin with Ultra High Sensitivity and Specificity," Biosensors and Bioelectronics, Elsevier, Vol. 165, 112363, Oct. 2020.

[156] M. M. H. Milu, M. A. Rahman, M. A. Rashid, *et. al.*, "Improvement of Classification Accuracy of Four-Class Voluntary-Imagery fNIRS Signals Using Convolutional Neural Network," Engineering, Technology & Applied Science Research, Vol. 13, Issue 2, pp. 10425-10431, April 2023.

[157] T. Yanagida, K. Machida, K. Asami, *et. al.*, "Harmonic Suppression Technique of Magnetic Field Coupling Type Wireless Power Transmission System Using ATAC Circuit," IEEE 14th International Conference on Solid-State and Integrated Circuit Technology, Nov. 2018.

[158] A. Kuwana, *et. al.*, "Numerical Simulation for the Starting Characteristics of a Wind Turbine," Advanced Engineering Forum, Vol. 38, pp.215-221, Nov. 2020.

[159] R. M. Galindo, *et. al.*, "Low-Cost Powered Air-Purifying Respirator (PAPR) "Distancing-Free Mask Frontline (DFM-F) Prototype No.1" for the Operational Tests in Hospitals in Cebu City, Philippines," Mechanical and Electrical Intelligent System, Vol.5, No.2, pp.1-6, April 2022.

[160] E. Carcasona, et. al., "Very-Low-Cost Powered Air-Purifying Respirator (PAPR) "Distancing-Free Mask Industry (DFM-I) Prototype No.1" and Proposal for a Lockdown-Free Industry," Journal of Technology and Social Science, Vol.6, No.2, pp.1-4, April 2022

Haruo Kobayashi received the B.S. and M.S. degrees in information physics from the University of Tokyo, Tokyo, Japan, in 1980 and 1982, respectively, the M.S. degree in electrical engineering from the University of California at Los Angeles (UCLA), Los Angeles, CA, USA, in 1989, and the Ph.D. degree in electrical engineering from Waseda University, Tokyo, in 1995. After working at Yokogawa Electric, he joined Gunma University as Associate Professor and promoted to Professor. He has been engaged in research and education on analog /mixed signal LSI design & test, and signal processing algorithms. He is currently Professor Emeritus there. He has supervised 20 Ph. D. students and 160 MS students. He has published over 170 journal papers and 560 international conference papers, and he has served as committee member of many international conferences. He received the 2002 Yokoyama Science and Technology Award. He is a Senior Member of IEEE, IEICE and IEEJ.