# △Σ変調ADCを用いたモータ駆動用 ディジタル信号処理方式の検討

群馬大学: 小堀、古谷、山田、佐藤、田浦、森、

光野、小林(和)、小林(春)

ルネサステクノロジ:鴻上、黒岩、黒澤

# 背景

- 1. 背景と目的

- 2. 回路構成と提案方式

- 3. △∑変調ADCとディジタル制御方式

- 4. リア・デシメーションフィルタ方式

- 5. シミュレーション結果

- 6. 結論

## 1. 背景と目的

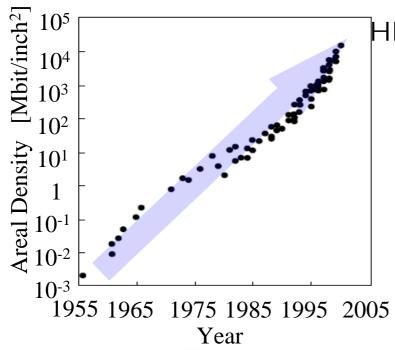

HDD**の面記録密度は**50**年間で約**1,000**万倍に増加**

トラック幅がどんどん狭くなる

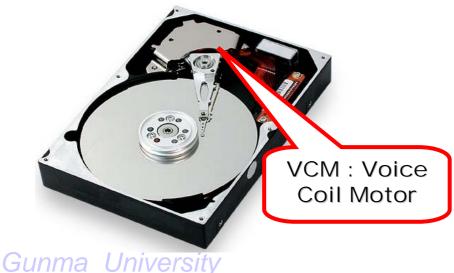

VCMの制御の高精度化

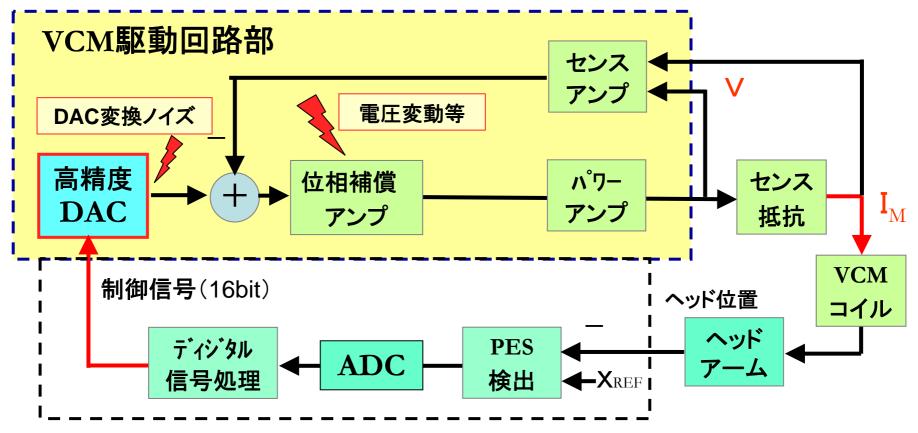

VCM駆動回路部

現在:アナログ信号 ⇒ 電源、GND、DAC等で

ノイズが発生

今後: ディジタル信号 ⇒ アナログノイズの一元化

ループ最終段に集約

\* 高精度なADCが必要

\*低域ノイズの低減

(シークモードは別制御)

# 目標仕様(トラッキング・モード時)

# 目的

- 低ノイズVC電流駆動回路の開発

- ⊿Σ変調ADCとディジタル信号処理方式

#### 従来仕様

**面記録密度:** 65 [Gbit/inch<sup>2</sup>]

トラック密度: 90 [ktracks/inch]

オントラック精度: ±28 [nm]

## 次期仕様

118 [Gbit/inch<sup>2</sup>]

113 [ktracks/inch]

±23 [nm]

#### 目標性能:トラッキングモード時

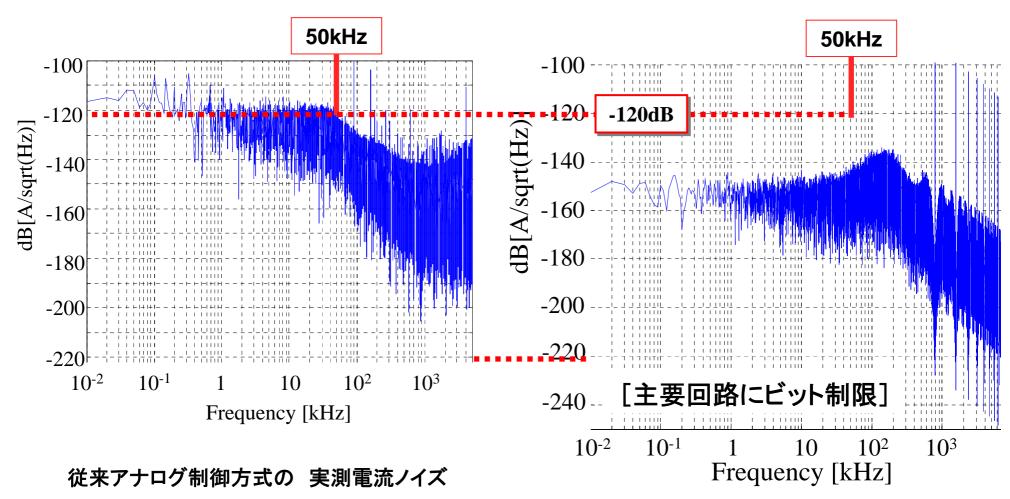

・ノイズレベル: N < -120dB (<50kHz) [DC30mV入力、従来計算法]</li>

• 遅延時間 :  $\tau < 7 \mu$  S [sin波、 $\pm 30$ mV、2kHz入力]

[条件] ステップ応答 : オーバーシュートなし [ステップ30mV入力]

遅延時間:電流制御入力に対する モータ駆動電流

# 2. 回路構成と提案方式

## (1) 従来アナログ制御方式の回路構成

- ●CPUからの制御信号に 正確にVCM電流 IMを追従

- ●モータ電流を検出し、フィードバック制御

PES: Position Error Signal

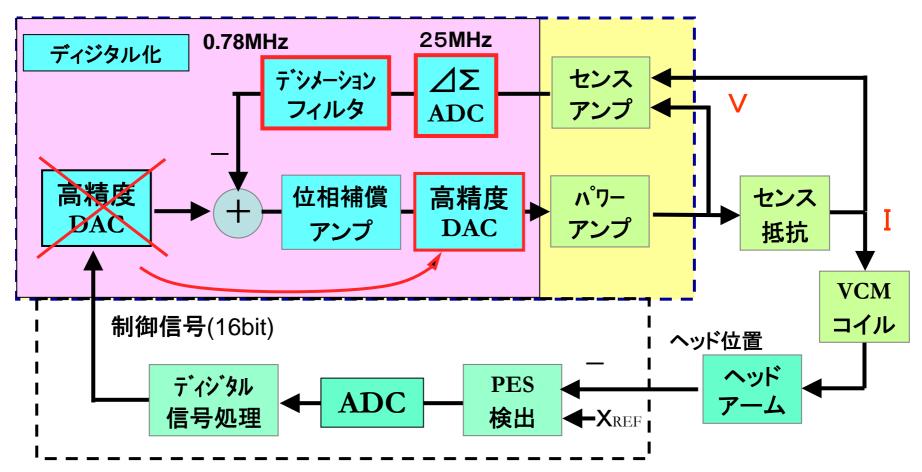

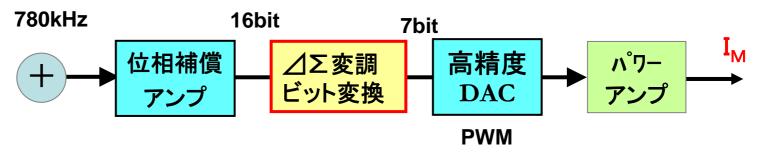

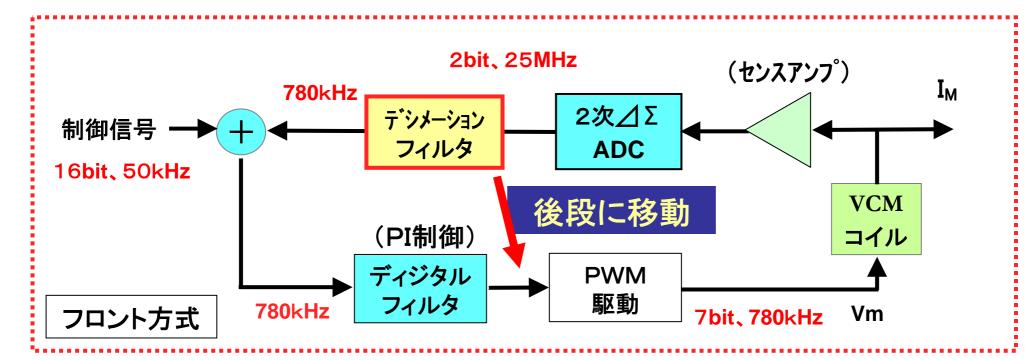

## (2) ディジタル制御方式の回路構成(フロント方式)

- ●ループ制御回路の多くをディジタル化 ⇒ 初段に高精度ADCが必要

- ●DACをループ終段に移動し、ノイズ低減(回路の簡単化)

- ●デシメーション・フィルタが必要(LPF+ダウン・サンプリング:(25⇒0.78MHz)

# 3. **△**∑変調ADCと出力ノイズ

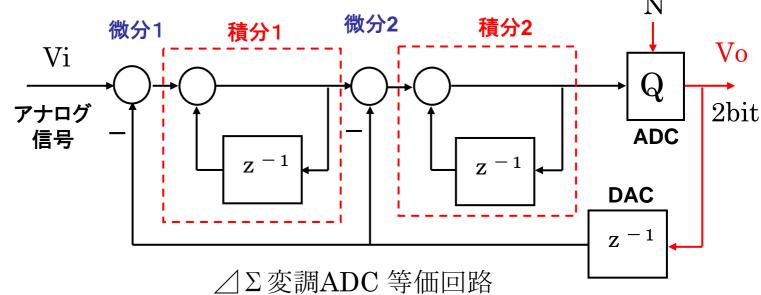

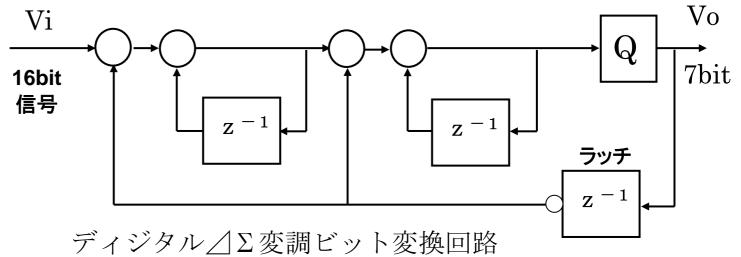

## (1) 2次△∑変調ADC回路(等価回路)

●構成: 微分+積分 ⇒ 量子化、ADC+DACが必要 低ビット出力で誤差大⇒高速サンプリングで帰還補正 (電圧軸の精度を、時間軸方向に拡散)

●伝達関数: Vo=Vi+(1−Z<sup>-1</sup>)N =Vi+ N/6 SIN<sup>4</sup>(πF/Fs) ノイズ出力(近似式) No=N·(πF/Fs)<sup>4</sup>/6 (F<<Fs)

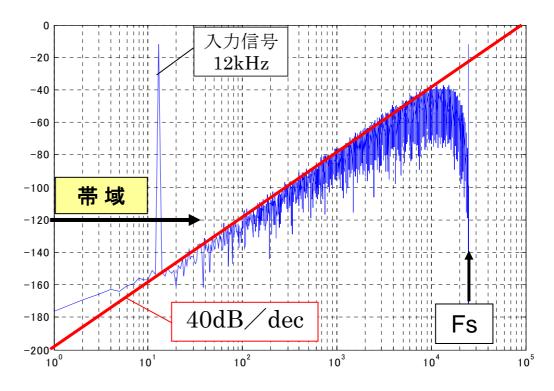

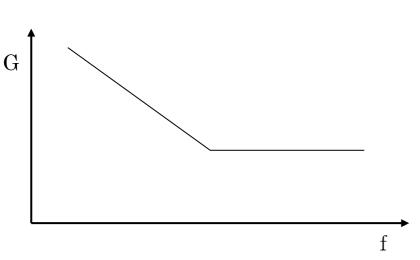

# (2) △∑ADCのノイズ・スペクトラム(シミュレーション)

◆特性:ADCノイズを広域にノイズ・シェーピング F<Fs/6 でノイズ低減効果・・・傾斜部 40dB/dec 低域レベル: -140dB @25kHz(=Fs/1000)

#### ● モータ帯域:

- $F_M < 50 \text{kHz}$

- ・数kHz以下が重要

2次2ビット ΔΣ変調のスペクトラム

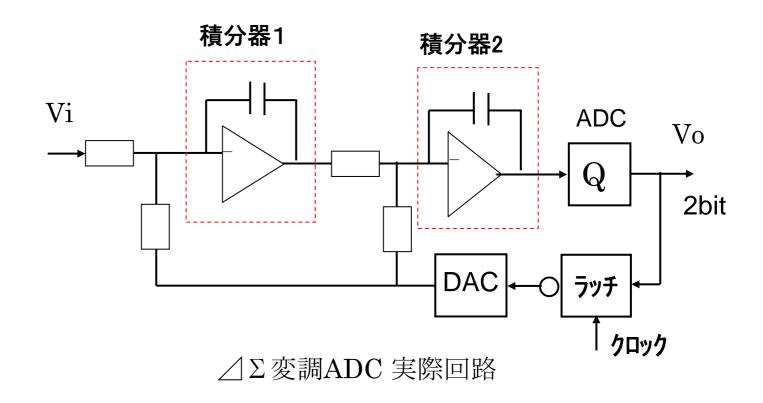

# (3) 2次 △ Σ変調ADC回路(実際の回路)

●構成: OPアンプによる(微分回路+積分回路)構成 加算抵抗は等しく(極性に注意)

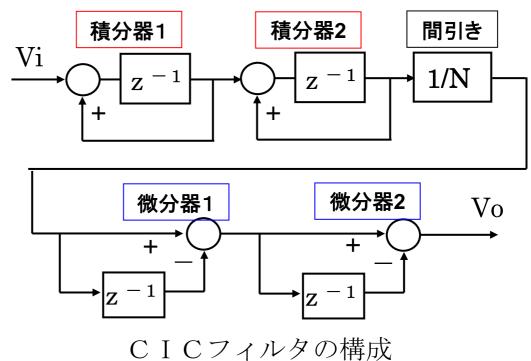

## (4) デシメーション・フィルタ

- 構成: LPF+ダウンサンプリング

- \* LPF: 折り返し防止用フィルタ・・・ 高次・低Fcフィルタ ただし 遅延時間の制限あり

- ▶ CRCフィルタの採用:加算器、減算器のみの構成

- \* 2セクション構成

- \* Fs=25MHz Fc=250kHz

- \*間引き:32

- ⋑特性

- \* Sinc フィルタ

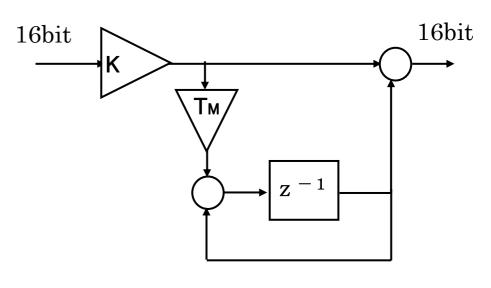

#### (5) 位相補償とDAC

#### (A) 位相補償アンプ: モータ特性の補正と PI 制御

- ●モータのインピーダンス(近似)・・・ Z(s)=r+sL=r(1+sT<sub>M</sub>)⇒ 周波数的に直線特性にしたい・・・逆補正

- ●センス抵抗による電流:  $I_M(s)=V(s) \angle Z(s)$  より 位相補償特性:  $G(s)=K\cdot Z(s)$  ⇒  $K\cdot (1+sT_M)\cdots$  低域ゲインをアップ

(A) 位相補償回路の伝達特性

(B) 位相補償回路の構成

#### (B) ビット変換とDAC(PWM回路)

● 2次⊿∑変調ビット変換:16 bit⇒7 bit :ノイズ・シェーピング

● 特性:加算器・積分回路(ラッチ)のビット数に注意

出力ノイズ: 180kHz以下で低減: △N=△N7·(F/180k)

## (6) 出力ノイズ比較(従来計算法に統一)

- 従来方式ノイズ:スピンドル・モータ成分あり・・・ベースレベル: 120dB

- ディジタル方式: 約30dB の改善見込みあり(センスアンプ・ノイス、駆動回路ノイス、含まず)

ディジタル制御方式のシミュレーション・ノイズ

# 4. リア・デシメーションフィルタ方式

- (1)デシメーション・フィルタの挿入位置検討

- (A) フロント・デシメーションフィルタ制御方式の特徴

- \* 低周波( 780kHz) ⇒ 低消費電力·素子数多(16ビットの演算)

- \* デシメーション・フィルタ ⇒ 高精度・高次数(゚。゚ループ初段)⇒ 素子数多

- \* 多ビット処理 ⇒ 演算精度の劣化(丸め誤差)

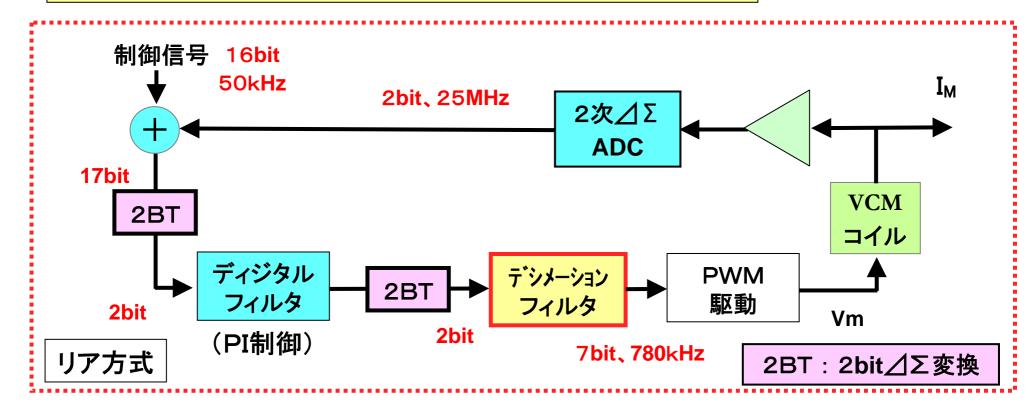

#### (B)リア·デシメーション·フィルタ方式···PWMの前に移動

- \* デシメーション・フィルタ ⇒ 低精度・低次数(゚.゚ループ最終段)⇒ 素子数少ただし 高速演算必要 ⇒ 消費電力 増大

- \* 各ブロック出力の 2ビット化 ⇒ 素子数・消費電力の低減

#### (C)2ビット変換の特徴

- \* 2ビット入力 ⇒ 掛算器の簡単化

- \* 丸め誤差・量子化誤差 ⇒ △∑変調によるノイズ・シェーピング (ブロック内のラッチビット数を、2~3ビット上げる)

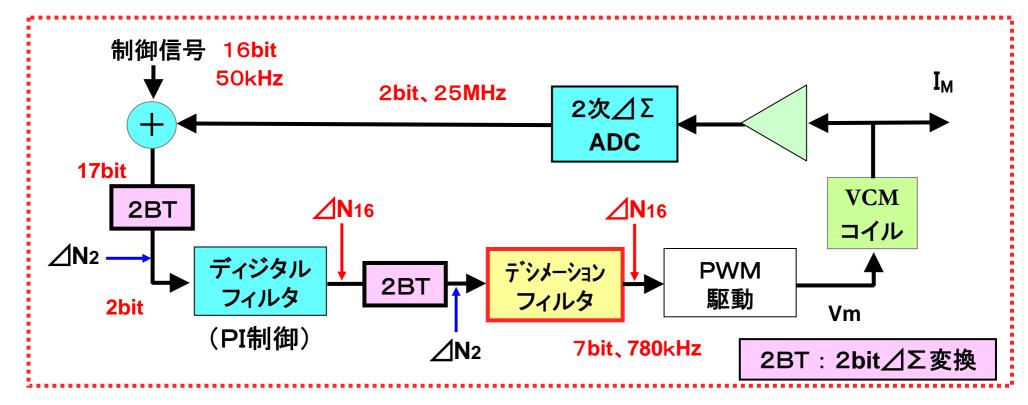

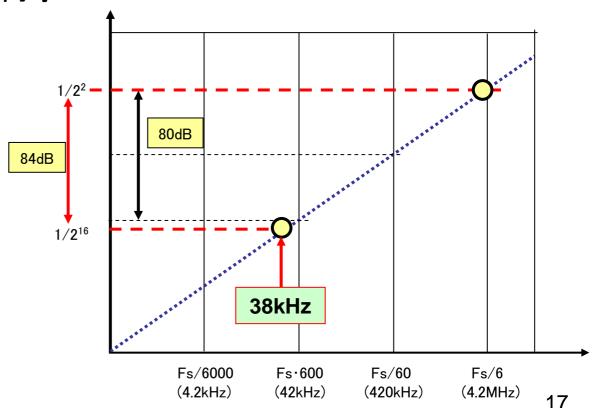

#### (D)丸め誤差と⊿∑変調ノイズの比較

\* 丸め誤差レベル : 16bit ⇒ ⊿N<sub>16</sub>=1/2<sup>16</sup>

\* △∑出力ノイズレベル: 2bit ⇒ △N2=1/2<sup>2</sup>

両者のレベル差 : ⊿N = 2<sup>14</sup> • • • 84 dB

\* △∑変調ノイズ: Fs/6 で △N2 と同等

⇒ 右図の特性

\*ノイズ・シェーピング出力 38kHz で 丸め誤差と同等

#### ノイズに関して

38kHz以下では リア方式が有利

#### (2)リア方式における 素子数低減手法

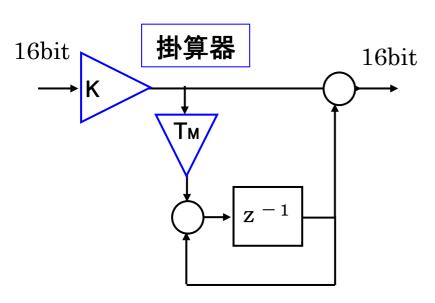

#### (A) 位相補償回路・・・ Tm は外部設定係数

- \*(B)図のように変形 ⇒ K2=K·TM

- \* 2ビット入力より ⇒ K、K2 は係数器···LUTで可能

- \*K、TM は外部設定 ⇒低い精度で可能 ⇒低ビット数でOK

(A) フロント方式の補償回路

(B) リア方式の補償回路

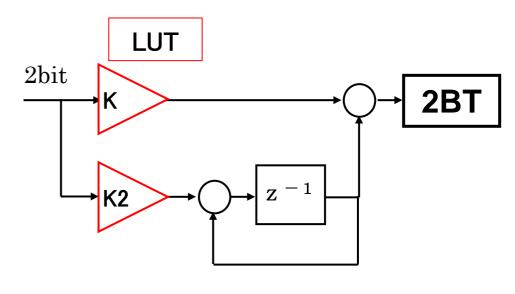

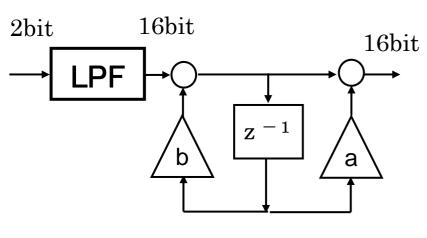

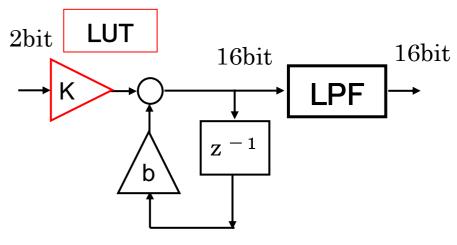

#### (B) LPF用位相進み補償

- \* デシメーション・フィルタ内のLPFで位相が遅れる。⇒ これを補償

- \*一般には、LPF後に位相進み補償(リードーラグ・フィルタ)

- \*素子数削減手法:ブロック入替えと式の変形

$$F(z)=(1-a\cdot z^{-1})/(1-b\cdot z^{-1})=(1-b/a)/(1-b\cdot z^{-1})=K/(1-b\cdot z^{-1})$$

\*係数器 K:LUT で実現可能

(A) LPF+位相補償

(B) 位相補償+LPF

# 5. シミュレーション結果

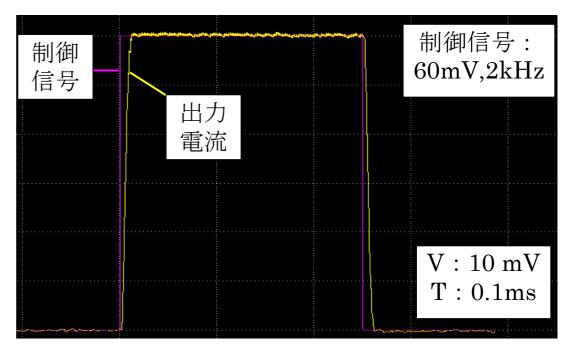

## (1)ステップ応答

\*仕様:オーバーシュートが無い

\* 結果:立上り傾斜

di/dt = 60m/0.02ms

$= 3A/ms = 3mA/\mu s$

●測定条件:制御信号⇒モータ駆動電流 制御信号:矩形波、2kHz、60mV

ステップ応答 (ゲイン調整後)

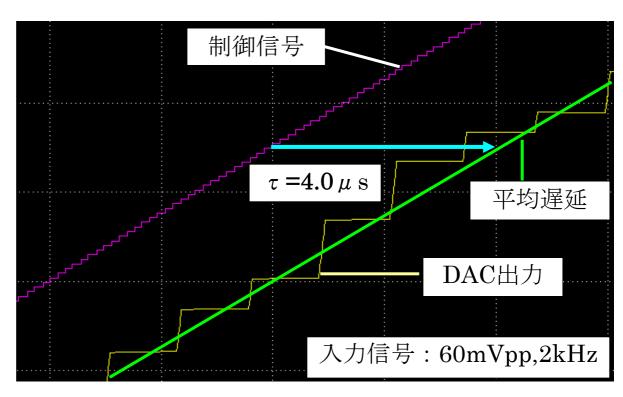

## (2) 遅延特性

\* 仕様: <7μs

\*  $\tau = 4.0 \ \mu \, s$

#### ●測定条件:制御信号⇒モータ駆動電流 制御信号: SIN波、2kHz、60mVpp

クローズド・ループ遅延特性

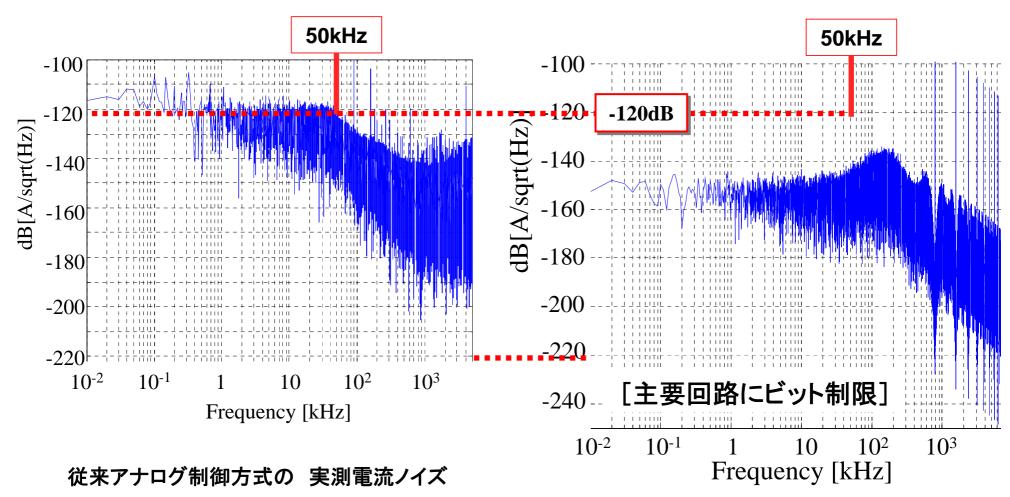

# (3) 従来方式とのノイズ比較(従来計算法に統一)

- 従来方式ノイズ:スピンドル・モータ成分あり・・・ベースレベル: 120dB

- ディジタル方式: 約30dB の改善見込みあり(センスアンプ・ノイス、駆動回路ノイス、含まず)

Gunma University

フロント制御方式のシミュレーション・ノイズ

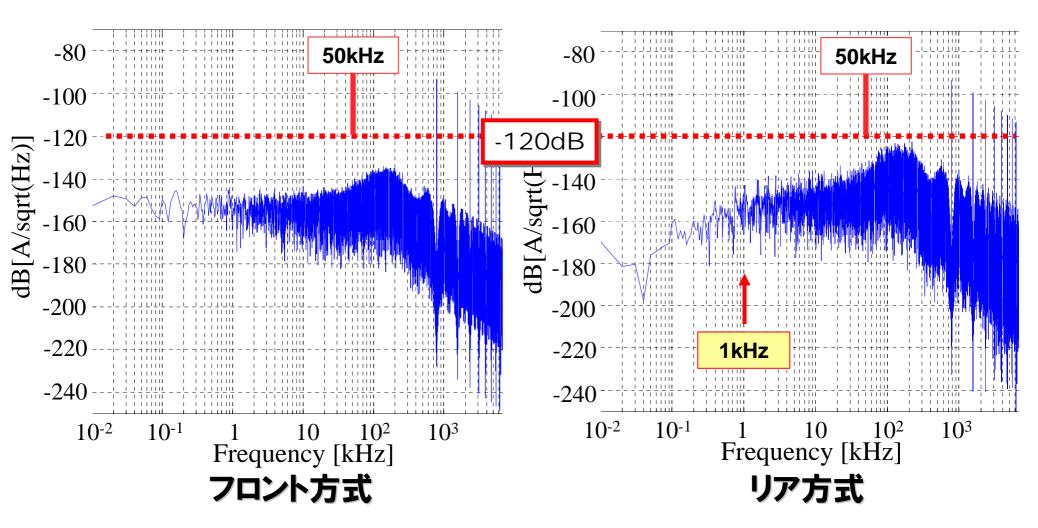

# (4) フロント方式とリア方式の比較

● フロント方式: > 1kHz で有利、リア方式: <1kHz で有利</p>

# 結 果

## HDD用VCMの高精度電流制御駆動方式として

- 2. 従来アナログ制御方式(実測)に比較して、シミュレーションで 電流ノイズレベルを 30dB 低減 ⇒ -150dB

- 3. デシメーション・フィルタを後段に設置したリア方式で 丸め誤差と減素子数の低減

- 4. リア方式では、さらに 低域ノイズ(<1kHz)を低減

- 5. 遅延時間: τ =4.0 μ s