PAPER Special Section of Selected Papers from the 9th Karuizawa Workshop on Circuits and Systems

# Track/Hold Circuit in GaAs HBT Process

Tsutomu TOBARI<sup>†</sup>, Nonmember, Haruo KOBAYASHI<sup>††</sup>, Member, Kenji UCHIDA<sup>††</sup>, Nonmember, Hiroyuki MATSUURA<sup>††</sup>, Member, Mineo YAMANAKA<sup>††</sup>, Shinji KOBAYASHI<sup>††</sup>, Tadashige FUJITA<sup>††</sup>, Nonmembers, and Akira MIURA<sup>††</sup>, Member

SUMMARY This paper reports on the design and performance of a very fast Track/Hold (T/H) circuit with GaAs Heterojunction Bipolar Transistor (HBT) to precede a 3GS/s 6 bit ADC. The T/H circuit employs a differential open-loop architecture for high-speed operation, and it consists of diode bridge switches, hold capacitors and output buffers. The differential structure as well as the output buffers suppress droop effects due to the small  $h_{FE}$  ( $\approx$ 20) of our HBT. Measured results show that the T/H circuit has better than 6 bit linearity within an input range of  $1.0 V_{p-p}$  with power dissipation of 990 mW, and the bandwidth is 6 GHz in the track mode. The measured droop rate is 2.1 mV/ns, the feedthrough is -46 dB at 500 MHz and the hold pedestal is less than 10 mV. Also a 3 GHz sampling operation of the T/H circuit was measured. The T/H circuit uses 43 HBTs, 24 Schottky barrier diodes and occupies a chip area of  $1.4 \times 1.75 \,\mathrm{mm^2}$ . We also describe the design and performance of a variable gain amplifier with GaAs HBT to precede the T/H circuit as an input buffer and adjust its gain. These results support the possibility of meeting the requirements for a high-speed ADC system.

key words: track-hold, sample-hold, analog-to-digital converter, HBT. GaAs

#### 1. Introduction

Electronic devices are continuously getting faster and, accordingly, there is a growing need for instruments to measure their performance. We describe here the design and performance of a very fast Track/Hold (T/H) circuit to precede a 3 GS/s 6 bit ADC [1]-[3] for future measuring instrument applications. A T/H circuit is necessary *in practice* to improve the AC performance of the following ADC even if the ADC employs a flash or folding/interpolation architecture which *in principle* does not require a T/H circuit [4], [5]. T/H circuits are also key components for a time-interleaved ADC system [6].

We chose the GaAs Heterojunction Bipolar Transistor (HBT) to implement the ADC system because of its good device matching, large  $g_m$  and high  $f_T$ , and now we are trying to integrate T/H and ADC circuits on an AlGaAs/GaAs HBT IC. Recently a couple of in-

Manuscript received June 24, 1996.

Manuscript revised September 30, 1996.

stitutions have implemented very fast ADCs [7], [8] with this technology, and their figures of the merits compete with Si Bipolar ADCs. The technological potential of GaAs HBT to T/H circuits has been addressed [9]; however, only a limited number of implementations have been reported [7], [8], [10]–[12]. In this paper we investigate the technological potential of GaAs HBT for realizing a very fast T/H circuit, and report on its design and measured performance. We also describe the design and performance of a variable gain amplifier (VGA) with GaAs HBT to precede the T/H circuit and adjust its gain.

GaAs MESFET and Si Bipolar are also technology candidates to realize a high-speed T/H circuit and the T/H circuit design issue comparison among GaAs HBT, GaAs MESFET and Si Bipolar is as follows: since the gate current of GaAs MESFET is negligible, the droop rate of a T/H circuit with GaAs MESFET is very small, which is an advantage of GaAs MES-FET. However GaAs MESFET suffers from the trap effects and  $g_m$  is smaller compared to GaAs HBT and Si Bipolar, and the challenge in the T/H circuit design with GaAs MESFET is to overcome them [13], [14]. Also since the device matching of GaAs MESFET is poor compared to GaAs HBT and Si Bipolar, monolithic integration of a high accuracy T/H and ADC system will be difficult. The  $f_T$  of GaAs HBT is higher than that of Si Bipolar but the device matching of Si Bipolar is better. Then GaAs HBT will be suitable for the very high-speed but relatively lower accuracy T/H and lower resolution ADC system compared to Si Bipolar [15], [16]. Also the thermal conductivity of GaAs substrate is one-third of Si Bipolar and thermal problems should be taken into account more in GaAs HBT circuit design [17].

#### 2. GaAs HBT Process

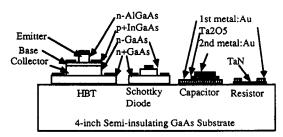

In our AlGaAs/GaAs HBT process, npn transistors and Schottky barrier diodes (SBDs), thin-film resistors  $(25\,\Omega/\Box)$  and metal-insulator-metal capacitors  $(31\,\mathrm{nF/cm^2})$  are available and a cross section of the devices is shown in Fig. 1. In our HBT,  $h_{FE}$  is 20,  $f_t = 40\,\mathrm{GHz}$  and  $f_{max} = 40\,\mathrm{GHz}$  with an emitter current

<sup>&</sup>lt;sup>†</sup>The author is with Iwatsu Electric Co., Ltd, Research and Development Department, Tokyo, 168 Japan.

<sup>&</sup>lt;sup>††</sup>The authors are with Teratec Corporation, Research and Development Department 1, Musashino-shi, 180 Japan.

Fig. 1 Cross section of the devices.

Table 1

HBT characteristics (SPICE parameters).

| Emitter size | $2\times10\mu\mathrm{m}^2$ | $I_{MAX}$ | 10 mA  |

|--------------|----------------------------|-----------|--------|

| $	au_F$      | 2.12 ps                    | $C_{JC}$  | 60 fF  |

| $C_{JE}$     | 83 fF                      | $R_B$     | 68.5Ω  |

| $R_E$        | $9.05\Omega$               | $R_C$     | 20.0 Ω |

Table 2 SBD characteristics.

| Junction size | $2.1\times20\mu\text{m}^2$ |         |       |

|---------------|----------------------------|---------|-------|

| Series L      | 30 pH                      | Stray C | 50 fF |

| $C_{jo}$      | 30 fF                      | $R_s$   | 5.5 Ω |

| M             | 0.35                       | N       | 1.11  |

density of  $5.0\times10^4~\mathrm{A/cm^2}$ , and  $BV_{CEO}>10~\mathrm{V}$ . Table 1 shows its other characteristics. In our SBD  $R_{on}=4.0~\Omega$  and  $C_{vo}=30~\mathrm{fF}$  and Table 2 shows its other characteristics. We consider GaAs HBT to be suitable for realizing a very high-speed T/H circuit because  $f_T$  of HBT is high, GaAs substrate is semi-insulating and SBDs can realize very fast diode bridge switches.

## 3. T/H Circuit

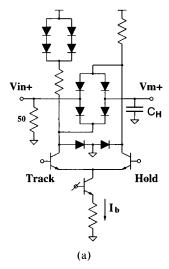

Architecture: The T/H circuit employs a differential open-loop architecture [4], [5] for high-speed operation, and it consists of diode bridge switches, hold capacitors and output buffers (Fig. 2). A VGA circuit described in Sect. 4 precedes the T/H circuit as an input buffer.

We consider the main challenge in our T/H circuit design to be reducing the droop rate while maintaining high-speed operation because of the small  $h_{FE}$  of our HBT, while other nonidealities are relatively insignificant because GaAs substrate is semi-insulating and, thus, the associated parasitic capacitances of active and passive elements are small.

**Acquisition Time and Bandwidth:** The output  $V_{out}(t)$  and input  $V_{in}(t)$  of the T/H circuit in the track mode are given by the following relationships provided that it is a first-order system:

$$V_{out}(t) = V_{in}(t) \exp(-t/\tau)$$

where  $\tau$  is a time constant. For a 3 GS/s operation, we set the acquisition time to 124 ps and during this time  $V_{out}(t)$  should reach  $V_{in}(t)$  with better than a 6 bit accuracy (0.78%) which demands

$$\tau \le 25.5 \,\mathrm{ps}.$$

**Fig. 2** Track/hold circuit schematics. (a) Core of track/hold circuit. The actual circuit is differential but is shown single-ended for simplicity. (b) Output buffer.

Hence the requirement of the analog bandwidth in the track mode  $f_{total}$  is given by

$$f_{total} = \frac{1}{2\pi\tau} \ge 6 \, \mathrm{GHz}.$$

The T/H circuit consists of diode bridge switches and an output buffer and we assign their bandwidth to 10 GHz and 8 GHz as design specifications, respectively, to achieve a total bandwidth of 6 GHz according to the following equation:

$$\frac{1}{6\,{\rm GHz}} \approx \sqrt{\frac{1}{(10\,{\rm GHz})^2} + \frac{1}{(8\,{\rm GHz})^2}}.$$

**Diode Bridge Gate Switch:** SBDs are used for the diode bridge switches as they have small parasitic capacitances and can provide high-speed switching. As the hold capacitance  $C_H$  increases, the effects of droop, feedthrough and hold pedestal are reduced but bandwidth decreases. We chose a hold capacitor  $C_H$  of  $0.6 \, \mathrm{pF}$  as a best compromise and set the diode bridge tail

current  $I_b$  to 25 mA in Fig. 2(a) so that the bandwidth  $f_{bridge}$  of the diode bridge reaches 10 GHz:

$$f_{bridge} = \frac{1}{2\pi R_s C_H} = 10\,\mathrm{GHz},$$

where

$$R_s = 26.5 \,\Omega$$

at  $I_b = 25 \,\mathrm{mA}$ .

Also note that the slew rate  $V_{out_{max}}$  is given as follows:

$$\frac{dV}{dt} = \frac{I_b}{2C_H} = 2\pi f_{bridge} V_{out_{max}},$$

then

$$V_{out_{max}} = \pm 0.33 \, V.$$

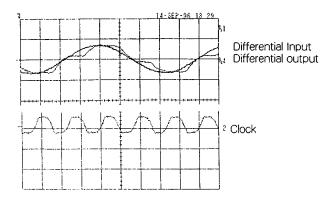

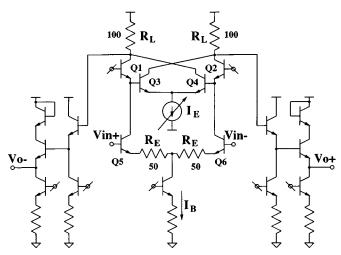

**Output Buffer:** The output buffer in Fig. 2 (b) consists of differential Darlington emitter followers and an open-loop amplifier with a gain of one. The Darlington emitter followers decrease the base currents which flow from the nodes of  $V_{m+}$  and  $V_{m-}$ , and this reduces the droop effect as described later. We use an open-loop unity gain amplifier because it is faster than a closed-loop one. In our open-loop amplifier (Fig. 2 (b)),  $Q_1$  and  $Q_2$  are added to improve the linearity, and the gain of the open-loop amplifier is given by

$$Gain := \frac{R_L + 1/g_{mL}}{R_E + 1/q_{mE}},$$

where  $g_{mL}$  is the transconductance of  $Q_1,\,Q_2$  and  $g_{mE}$  is the transconductance of  $Q_5,\,Q_6$ . Since  $R_L=R_E=50\,\Omega$  and  $g_{mL}=g_{mE}$ , the gain is set to one. Also the current buffers  $Q_3,\,Q_4$  enhance the AC performance of the unity gain amplifier. We see that  $V_{o+}-V_{o-}=V_{m+}-V_{m-}$  and the common mode voltage between  $V_{o+}$  and  $V_{o-}$  is constant and level-shifted appropriately regardless of that between  $V_{m+}$  and  $V_{m-}$ .

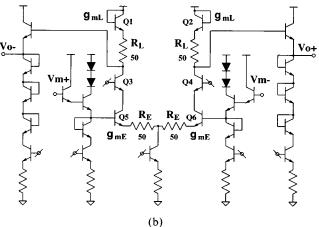

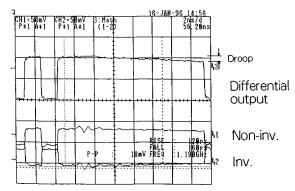

**Operation:** Figure 3 shows measured waveforms of the T/H circuit for a sinusoidal input with  $f_{in} = 750 \,\text{MHz}$

200ps/div

**Fig. 3** Measured waveforms for a sinusoidal input with  $f_{in} = 750 \,\text{MHz}$ , and a sampling clock of  $f_s = 3 \,\text{GS/s}$ . When the clock is high (low), the T/H circuit is in hold (track) mode respectively.

and a sampling clock of  $f_s = 3$  GS/s. In the track mode, Track signal is high and Hold signal is low (Fig. 2 (a)), and the diode bridge switch is ON. Hence the output signal follows the input signal. On the other hand, in the hold mode, Track signal is low and Hold signal is high, and the diode bridge switch is OFF. The input voltage just before switching from the track to hold modes is stored in the hold capacitor, and thus the output voltage is constant in the hold mode; this helps improve the AC performance of the following ADC. Also the measured error between the input and output just before switching from the track to hold modes is within 1/2 LSB.

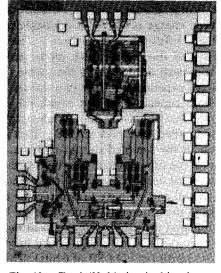

**Implementation:** The differential core part in Fig. 2 (a) uses 16 HBTs and 20 SBDs dissipating 570 mW, and the output buffer in Fig. 2 (b) uses 27 HBTs and 4 SBDs dissipating 420 mW. The whole T/H circuit occupies a chip area of  $1.4 \times 1.75 \,\text{mm}^2$  (Fig. 10), and its layout is rather conservative to avoid thermal problems due to the low thermal conductivity of GaAs substrate [17].

**Input Range:** The measured results show that the T/H circuit has better than 6 bit linearity within the differential input range of  $1.0 V_{p-p}$ .

**Droop:** The input bias current flowing to the output buffer in the hold mode discharges the hold capacitor  $C_H$  and the held voltage drops; this is called droop [18]. The differential structure, as well as the output buffers, suppress droop effects due to the small  $h_{FE}$  ( $\approx$ 20) of our HBT. Suppose that currents  $I_{b+}$  and  $I_{b-}$  flow from the nodes of  $V_{m+}$  and  $V_{m-}$  to the output buffer respectively. Then voltage drops  $\Delta V_{m+}$  and  $\Delta V_{m-}$  at nodes  $V_{m+}$  and  $V_{m-}$  during the hold time  $T_H$  are given by

$$\Delta V_{m+} = -\frac{I_{b+}}{C_H} T_H, \quad \Delta V_{m-} = -\frac{I_{b-}}{C_H} T_H,$$

respectively. Since the  $h_{FE}$  is rather small,  $I_{b+}$ ,  $I_{b-}$  are relatively large and the voltage drops may be considerable. In other words, the single-ended structure suffers from significant droop effects. On the other hand, the differential voltage drop is given by

$$\Delta(V_{m+} - V_{m-}) = -\frac{I_{b+} - I_{b-}}{C_H} T_H.$$

Since the values of  $I_{b+}$  and  $I_{b-}$  are almost the same and thus  $\Delta(V_{m+}-V_{m-})$  is very small compared to  $\Delta V_{m+}$  and  $\Delta V_{m-}$ , we see that the differential structure reduces the droop effect significantly. The Darlington emitter followers reduce  $I_{b+}$ ,  $I_{b-}$  and hence also  $I_{b+}-I_{b-}$ , which further reduces the droop rate. The unity gain open-loop amplifier maintains the common mode voltage between the differential outputs  $V_{o+}$  and  $V_{o-}$  even if the common mode voltage between  $V_{m+}$  and  $V_{m-}$  decreases in the hold mode.

The measured results show that the droop rate is less than 2.1 mV/ns (Fig. 4), which is small enough for 3 GS/s 6 bit applications. The main reason for droop

**Fig. 4** Droop measurement. A pulse input with  $f_{in} = 500 \,\text{MHz}$  is applied with a sampling speed of  $f_s = 62.5 \,\text{MS/s}$ .

even in a differential structure is the collector-emitter voltage dependence of base currents in HBTs.

Feedthrough: Ideally no current flows through the diode bridge switch in the hold mode and its impedance is infinite, and thus the hold capacitor is isolated from the input signal. However, in reality because of nonidealities such as junction capacitances in bridge diodes, isolation is not complete. The extent to which an input signal affects the hold output in the hold mode is characterized by feedthrough [18].

Since the junction capacitance of SBDs in the diode bridge is small (30 fF), feedthrough is not expected to be a problem: the calculated feedthrough [18] is -54.5 dB at 500 MHz while the measured result is -46.0 dB at 500 MHz, which is less than 1/2 LSB of 6 bits.

Hold Pedestal: While the bridge diodes are ON in the track mode, they store charge in both their depletion capacitance and their diffusion capacitance. After the bridge switches to the hold mode and all transients settle, the bridge diodes conduct no current. In this state, reduced charge is stored in the depletion capacitance and the diffusion storage is zero. The difference in charge stored during the track mode and the hold mode is from each diode during the turn-off transient. If the charges expelled from the two diodes connected from the hold capacitor are not equal, the net charge injected onto that capacitor imparts an output voltage perturbation called hold pedestal [18]. This introduces a distortion in the sampled output if it is nonlinearly dependent on the input signal. In other words, the hold pedestal does not need to be zero if it is proportional to the input signal, and we have to consider its nonlinearity. Thanks to the differential structure, even harmonics are negligible and the third harmonic is dominant. The measured pedestal is 10 mV and its third harmonic distortion is  $-53.0 \, dB \, (< 1/4 \, LSB \, of \, 6 \, bits)$ . This result is due to the small junction capacitance of SBDs.

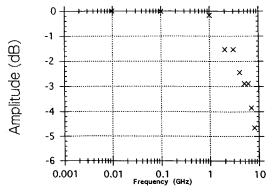

**Pulse and Frequency Responses:** Figure 5 shows the pulse response of the T/H circuit in the track mode. Its rise time (10%-90%) is 62 ps while the fall time is 72 ps, and we see that there is little overshoot in the pulse re-

**Fig. 5** Pulse response in the track mode. Rise time (10%–90%) is 62 ps while fall time is 72 ps.

Fig. 6 Frequency response. A sinusoidal input was applied to the T/H circuit and its frequency was swept from 10 MHz to 8 GHz.

sponse, which means that the output signal can follow the input signal properly in the track mode. Also, Fig. 6 shows the measured frequency response of the T/H circuit; a sinusoidal input was applied and its frequency was swept from 10 MHz to 8 GHz. We see that the bandwidth is 6 GHz.

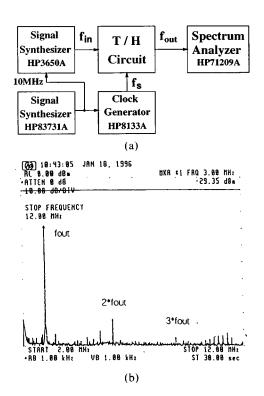

**3GHz Sampling:** We use the principle of equivalent time sampling for a 3GS/s operation measurement of the T/H circuit [19]. Figure 7 (a) shows its setup where a sampling clock with  $f_s$  and a sinusoidal input with  $f_{in}$ are synchronized and the output spectrum of the T/H circuit is measured by a spectrum analyzer. The signal frequency  $f_{out}$  of the T/H circuit output is given by  $f_{out} = f_s - f_{in}$ , and it is near the baseband if  $f_s$  and  $f_{in}$ are close. Figure 7(b) shows the measured power spectrum of the T/H circuit output with  $f_s = 3.000 \,\mathrm{GS/s}$ and  $f_{in} = 2.997 \,\text{GHz}$ , and we see that the second harmonic is -83 dBm and the third harmonic is -95 dBm. This measurement was performed for the single-ended output  $V_{o+}$  due to the restriction of measurement instruments, but the actual T/H circuit has the differential output  $V_{o+}$ ,  $V_{o-}$ , which is expected to further improve the total harmonic distortion (even harmonics will be cancelled).

All measurements are performed by on-wafer probing, and the summary of the T/H circuit performance is given in Table 3.

Fig. 7  $\,$  3 GS/s measurement. (a) Measurement setup where  $f_{in}$  and  $f_s$  are synchronized. (b) Measured power spectrum of the T/H circuit output.

Table 3 Measured performance of T/H circuit.

| Clock frequency   | 3GS/s                          |

|-------------------|--------------------------------|

| Analog bandwidth  | 6 GHz                          |

| Analog input      | $1.0\mathrm{V}_{p-p}$          |

| Droop rate        | 2.1 mV/ns                      |

| Feedthrough       | -46.0 dB at 500 MHz            |

| Hold pedestal     | $< \pm 10 \mathrm{mV}$         |

| Power supplies    | 3.1 V,-4.5 V                   |

| Power consumption | 990 mW                         |

| HBT count         | 43                             |

| SBD count         | 24                             |

| Chip size         | $1.4 \times 1.75  \text{mm}^2$ |

#### 4. Variable Gain Amplifier

**Circuit:** A VGA to precede the T/H circuit as an input buffer and adjust the gain of the T/H circuit was also designed and fabricated with GaAs HBT. Figure 8 shows its circuit diagram. If  $Q_3$  and  $Q_4$  are not incorporated and the  $1/g_m$ 's of  $Q_1$ ,  $Q_2$ ,  $Q_5$  and  $Q_6$  are much less than  $R_E$  and  $R_L$ , then the gain is given by

$$Gain := \frac{V_o}{V_{in}} = \frac{R_L}{R_E}.$$

$Q_3$  and  $Q_4$  steer the current of  $I_E$  from the load resistors  $R_L$  and the gain is varied by changing  $I_E$ :

$$Gain := \frac{V_o}{V_{in}} = \frac{R_L}{R_E} \left( 1 + \frac{I_E}{I_B} \right).$$

Fig. 8 Variable gain amplifier circuit schematics.

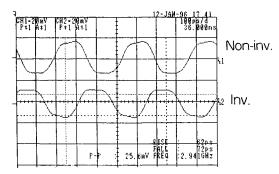

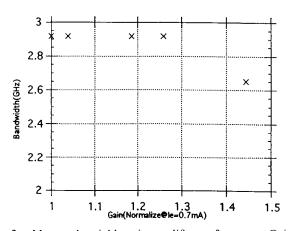

Fig. 9 Measured variable gain amplifier performance. Gain is normalized.

Fig. 10 Track/Hold circuit chip photo.

The differential outputs of the current gain cell are buffered with Darlington emitter followers to minimize

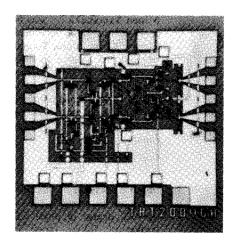

Fig. 11 VGA chip photo.

their base currents.

Since the current buffers  $Q_1$ ,  $Q_2$  are incorporated, changing the gain does not affect the bandwidth. In many VGA topologies, the gain-bandwidth products are constant, which means that the bandwidth changes according to the gain. However, the bandwidth of VGAs in the front-end of measuring instruments has to be constant regardless of the gain [20], and the circuit in Fig. 8 satisfies this requirement.

**Measured Results:** The VGA consists of 24 HBTs and 3 SBDs, and it occupies a chip area of  $1.0 \times 0.9 \,\mathrm{mm^2}$  (Fig. 11). The measured results showed that the gain is set to two, and it can be increased by 30% without changing the bandwidth of 2.9 GHz (Fig. 9), and it dissipates power of 155 mW.

## 5. Conclusion

We have described the design and performance of a very high-speed T/H circuit with GaAs HBT technology and shown that it meets the requirements to precede a 3 GS/s 6 bit ADC. We have also developed a VGA circuit which works as an input buffer of the T/H circuit and adjusts its gain.

## Acknowledgments

We would like to thank H. Nakamura, M. Morimura, H. Hosomatsu, K. Kobayashi, H. Sakayori, A. Miyazaki, A.A. Abidi and K. Wilkinson for valuable discussions.

#### References

- [1] H. Kobayashi, T. Tobari, H. Matsuura, A. Miura, M. Yamanaka, T. Yakihara, S. Kobayashi, S. Oka, T. Fujita, and D. Murata, "System architecture and key components of a multi-giga-hertz A/D converter with HBT," Proc. of IEEE Instrumentation and Measurement Technology Conference, pp.1160–1166, June 1996.

- [2] H. Kobayashi, T. Tobari, H. Sakayori, and H. Matsuura, "Multi-giga-hertz A/D converter design with HBT," Proc. of the 8th Karuizawa Workshop on Circuits and Systems,

- pp.145-150, April 1995.

- [3] H. Kobayashi, H. Sakayori, T. Tobari, and H. Matsuura, "Error correction algorithm for folding/interpolation ADC," Proc. of International Symposium on Circuits and Systems, Seattle, vol.1, pp.700-703, May 1995.

- [4] B. Razavi, "Principles of Data Conversion System Design," IEEE Press, 1995.

- [5] R. van de Plassche, "Integrated Analog-to-Digital and Digital-to-Analog Converters," Kluwer Academic Publishers, 1994.

- [6] H. Kobayashi, T. Tobari, and H. Matsuura, "Issues on time-interleaved ADC architecture," Proc. of the 9th Karuizawa Workshop on Circuits and Systems, pp.311– 316, April 1996.

- [7] K. Poulton, K.L. Knudsen, J.J. Corcoran, K.-C. Wang, R.B. Nubling, R.L. Pierson, M.-C.F. Chang, P.M. Asbeck, and R.T. Huang, "A 6 b 4 GSa/s GaAs HBT ADC," IEEE J. Solid-State Circuits, vol.30, no.10, pp.1109–1117, Oct. 1995.

- [8] K.R. Nary, R. Nubling, S. Beccue, W.T. Colleran, J. Penney, and K.-C. Wang, "An 8 bit 2 giga sample per second analog to digital converter," GaAs IC Symposium Tech. Digest, pp.303-306, 1995.

- [9] D.P. Wong and B.K. Oyama, "Analog-to-Digital Converters Using III-V HBTs," B. Jalali and S.J. Pearton, eds., InP HBTs: -Growth, Processing and Applications, Chapter 9, Artech House, 1995.

- [10] G.M. Gorman, J.B. Camou, A.K. Oki, B.K. Oyama, and M.E. Kim, "High performance sample-and-hold implemented with GaAs/AlGaAs heterojunction bipolar transistor technology," IEDM Tech. Digest, pp.623-626, 1987.

- [11] K. Poulton, J.S. Kang, and J.J. Corcoran, "A 2 GS/s HBT sample and hold," GaAs IC Symposium Tech. Digest, pp.199-202, 1988.

- [12] S. Naboicheck and S. Ems, "5 GHz sampling oscilloscope front-end based on heterojunction bipolar transistors (HBT)," GaAs IC Symposium Tech. Digest, pp.155-158, 1993

- [13] J. Sauerer, R. Hagelauer, F. Oehler, G. Rohmer, U. Schlag, D. Seitzer, T. Grave, and W. Kellner, "System architecture and key components for an 8 b 1 GHz GaAs MESFET ADC," GaAs IC Symposium Tech. Digest, pp.105-108, 1992.

- [14] K. Poulton, J. Concoran, and T. Honak, "A 1 GHz 6 b ADC system," IEEE J. Solid-State Circuits, vol.22, no.6, pp.962-970, Dec. 1987.

- [15] B. Pregardier, U. Langmann, and W. J. Hilery, "A I GS/s 8 b silicon bipolar track & hold IC," Tech. Digest of ISSCC, pp.58-59, 1996.

- [16] A.K. Joy, A.J. Holden, T.C. Leslie, and P.H. Saul, "A comparison of GaAs HJBT and silicon bipolar technologies for high-speed analog-to-digital converters," IEEE J. Solid-State Circuits., vol.24, no.3, pp.609-616, June 1989.

- [17] K.Poulton, K.L. Knudsen, J.J. Corcoran, K.-C. Wang, R.L. Pierson, R.B. Nubling, and M.-C.F. Chang, "Thermal design and simulation of bipolar integrated circuits," IEEE J. Solid-State Circuits, vol.25, no.10, pp.1379-1387, Oct. 1992.

- [18] W. Colleran, "A 10 bit 100 MS/s A/D converter using folding, interpolation, and analog encoding," UCLA Ph.D. Dissertation, Dec. 1993.

- [19] B. Razavi and J. Sung, "A 200 MHz 15 mW BiCMOS sample-and-hold amplifier with 3 V supply," ISSCC Tech. Digest, pp.56-57, Feb. 1995.

- [20] Kh. Hadidi and H. Kobayashi, "A 25 MHz 20 dB variable gain amplifier," Proc. of IEEE Instrumentation and Measurement Technology Conference, Hamamatsu, pp.780–

783, May 1994.

Tsutomu Tobari received the B.S. and M.S. degrees in physics from Science University of Tokyo in 1980 and 1984, respectively. In 1984 he joined IWATSU Electric Co., Ltd., where he was engaged in the development of high-speed CRT (cathode ray tube) for oscilloscopes. Since 1993, he has been developing high-speed analog-to-digital converters in Teratec Corporation.

Haruo Kobayashi received the B.S. and M.S. degrees in information physics and mathematical engineering from University of Tokyo in 1980 and 1982 respectively, and the Dr.Eng. degree in electrical engineering from Waseda University in 1995. From 1987 to 1989, he was at UCLA and received the M.S. degree in electrical engineering in 1989. He joined Yokogawa Electric Corp. Tokyo, Japan in 1982, where he was engaged in the re-

search and development related to measuring instruments and a mini-supercomputer. From 1994 he has been involved in the research and development of ultra-high-speed ADCs and DACs at Teratec Corporation; he is also a lecturer at Waseda University. Dr. Kobayashi is a member of the IEEE, and the Society of Instrument and Control Engineers. He is a recipient of the 1994 Best Paper Award from the Japanese Neural Network Society.

Kenji Uchida received the B.E. and M.E. degrees in electrical engineering from Waseda University in 1990 and 1992 respectively. In 1992, he joined Yokogawa Electric Corporation, Tokyo, Japan. Since 1993, he has been involved in the research and development of wide bandwidth sampling systems in Teratec Corporation, Japan.

Hiroyuki Matsuura received the B.S. and M.S. degrees in electronic engineering from Tokyo Institute of Technology, Tokyo, Japan, in 1978 and 1980, respectively. In 1980 he joined Yokogawa Electric Corporation, Tokyo, Japan. He was engaged in the research of medical imaging apparatuses and measuring instruments. From 1990 to 1992 he was a visiting scholar of Stanford University, Palo Alto, California. From 1992 he has been engaged in

the circuits design for high-speed / high-frequency measuring instruments in Teratec Corporation, Tokyo, Japan. Mr. Matsuura received the Society of Instrument and Control Engineers' Best Paper Award in 1988. He is a member of the IEEE and Society of Instrument and Control Engineers.

Mineo Yamanaka was born on June 3, 1948. In 1964 he joined Yokogawa Electric Corporation, Tokyo, Japan. He received B.S. degree in electronic engineering from Kogakuin University. From 1994 he has been engaged in the development of the semiconductor process for the high speed and high frequency application in Teratec Corporation, Tokyo, Japan.

Shinji Kobayashi was born in Tokyo, Japan, on February 2, 1963. He received the B.S. degree in physics from Sophia University, Tokyo, Japan, in 1985. In 1993 he joined Teratec Corporation, Tokyo, Japan. He has been engaged in the development of high-speed and high-frequency compound semiconductor devices.

Tadashige Fujita was born in Chiba, Japan, on April 28, 1965. He received the B.S. and M.S. degrees in physics from Gakusyuin University, Tokyo, Japan, in 1988 and 1990, respectively. In 1990 he joined the Yokogawa Electric Corporation, Tokyo, Japan. From 1993 he joined the Teratec Corporation, Tokyo, Japan. He has been engaged in the development of high-speed and high-frequency compound semiconductor devices.

Akira Miura was born in Japan, on November 5, 1955. He received the M.S.E. degree from Waseda University, Tokyo, Japan, in 1980. In 1980 he joined the Yokogawa Electric Corporation, Tokyo, Japan, where he was engaged in the research and development of compound semiconductor devices and circuits. From 1992 he has been engaged in research of III-V HBT's/Si-HBT's devices in Teratec Corporation. His research interests center

on the analysis and design of the band engineering for quantum electronics.