PAPER Special Section on Selected Papers from the 18th Workshop on Circuits and Systems in Karuizawa

# Complex Bandpass ΔΣAD Modulator Architecture without I, Q-Path Crossing Layout

Hao SAN<sup>†a)</sup>, Member, Akira HAYAKAWA<sup>†</sup>, Nonmember, Yoshitaka JINGU<sup>†</sup>, Student Member, Hiroki WADA<sup>†</sup>, Hiroyuki HAGIWARA<sup>†</sup>, Kazuyuki KOBAYASHI<sup>†</sup>, Nonmembers, Haruo KOBAYASHI<sup>†b)</sup>, Tatsuji MATSUURA<sup>††</sup>, Members, Kouichi YAHAGI<sup>††</sup>, Junya KUDOH<sup>††</sup>, Nonmembers, Hideo NAKANE<sup>††</sup>, Masao HOTTA<sup>†††</sup>, Toshiro TSUKADA<sup>††††</sup>, Koichiro MASHIKO<sup>††††</sup>, and Atsushi WADA<sup>†††††</sup>, Members

This paper proposes a new architecture for multibit com-SUMMARY plex bandpass  $\Delta\Sigma AD$  modulators with built-in Switched-Capacitor (SC) circuits for application to Low-IF receivers such as used for Bluetooth and WLAN. In the realization of complex bandpass  $\Delta\Sigma AD$  modulators, we face the following problems: (i) SNR of AD converter is deteriorated by mismatches between internal analog I and Q paths. (ii) Layout design becomes complicated because of signal lines crossing by complex filter and feedback from DAC for I and Q paths in the complex modulator, and this increases required chip area. We propose a new structure for a complex bandpass  $\Delta\Sigma$ AD modulator which can be completely divided into two paths without layout crossing, and solves the problems mentioned above. The two parts of signal paths and circuits in the modulator are changed for I and Q while CLK is changed for High/Low by adding multiplexers. Symmetric circuits are used for I and Q paths at a certain timing, and they are switched by multiplexers to those used for Q and I paths at another timing. Therefore the influence from mismatches between I and Q paths is reduced by dynamic matching. As a result, the modulator is divided into two separate parts without crossing signal lines between I and Q paths and its layout design can be greatly simplified compared with conventional modulators. We have conducted MATLAB simulations to confirm the effectiveness of the proposed structure.

key words: complex bandpass  $\Delta\Sigma AD$  modulator, I, Q path mismatches, dynamic matching, multiplexer

#### 1. Introduction

In the RF receiver of communication systems such as cellular phones and wireless LANs, low-IF receiver architecture is frequently used. In conventional low-IF receiver architectures, two real (one input and one output)  $\Delta\Sigma$ AD modulators are used for In-phase (I) and Quadrature (Q) paths. Its disadvantage is that not only input signals but also image signals

a) E-mail: san@el.gunma-u.ac.jp

DOI: 10.1093/ietfec/e89-a.4.908

are converted by ADCs. On the other hand, complex bandpass  $\Delta\Sigma$ AD modulators can provide superior performance to a pair of real bandpass  $\Delta\Sigma$ AD modulators of the same order. They process just input I and Q signals and not image signals, and AD conversion can be realized with low power dissipation, so they are desirable for such low-IF receiver applications [1]–[4]. The performance of the complex bandpass  $\Delta\Sigma$ AD modulator is degraded by mismatches between I and Q paths which cause both signal and quantization noise in the mirror image band and alias into the design signal band, thus decrease the SNDR of the complex modulator.

This paper presents a new Switched-Capacitor topology architecture which is suitable for complex bandpass  $\Delta\Sigma$ AD modulators and compensates for mismatches between I and Q paths. The new architecture reduces the amount of mirror image band quantization noise aliased into the signal band. It also simplifies the modulator structure into a symmetrical configuration with no crossing of signal lines between the two circuit parts, and thus required chip area becomes smaller and its layout design can be simplified. Moreover, this technique can be extended to multi-bit modulators suitable for complex bandpass DWA algorithm [5]–[7].

#### 2. New Structure of Complex Bandpass Filter

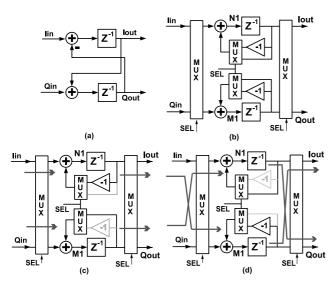

Figure 1(a) shows a conventional complex bandpass filter and the inputs and outputs are written as follows:

$$I_{out}(n) = I_{in}(n-1) - Q_{out}(n-1)$$

(1)

$$Q_{out}(n) = Q_{in}(n-1) + I_{out}(n-1)$$

(2)

Figure 1(b) shows the proposed structure of a complex bandpass filter, where four multiplexers (MUX) are added to the conventional structure. The select signal (SEL) for the MUXs is generated by half of CLK in  $Z^{-1}$  block and they are synchronized. Compared to the conventional structure, we see that the proposed complex filter can be divided into two separate parts without any crossing of signal lines,

The proposed complex filter operates with two states; in state 1 (in Fig. 1(c)), the upper part of circuit is used for I path, while the lower path is for Q path. In state 2 (in Fig. 1(d)), the upper part of circuit is used for Q path, while the lower path is for I path. In our proposed configuration, the input I and Q signals alternate between the

Manuscript received June 27, 2005.

Final manuscript received October 3, 2005.

<sup>&</sup>lt;sup>†</sup>The authors are with the Department of Electronic Engineering, Faculty of Engineering, Gunma University, Kiryu-shi, 376-8515 Japan.

<sup>&</sup>lt;sup>††</sup>The authors are with Advanced Analog Development Dept., Renesas Technology Corp., Takasaki-shi, 370-0021 Japan.

<sup>&</sup>lt;sup>†††</sup>The author is with the Department of Electronics & Communication Engineering, Musashi Institute of Technology, Tokyo, 158-8557 Japan.

<sup>&</sup>lt;sup>††††</sup>The authors are with Semiconductor Technology Academic Research Center (STARC), Yokohama-shi, 222-0033 Japan.

<sup>&</sup>lt;sup>+++++</sup>The author is with the Frontier Devices Research Center, Sanyo Electric Co., Ltd., Gifu-ken, 503-0195 Japan.

b) E-mail: k\_haruo@el.gunma-u.ac.jp

**Fig. 1** (a) Conventional complex bandpass filter. (b) Proposed structure of a complex bandpass filter. (c) Operation of the proposed complex bandpass filter (state 1). (d) Operation of the proposed complex bandpass filter (state 2).

above two parts of the complex filter by SEL signal defined above. Thus the inputs and outputs are written as the same as Eqs. (1) and (2).

#### 3. Conventional Complex Bandpass $\Delta\Sigma$ AD Modulator

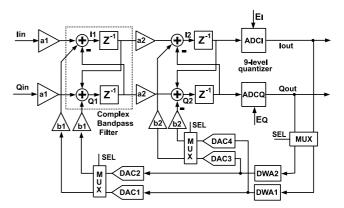

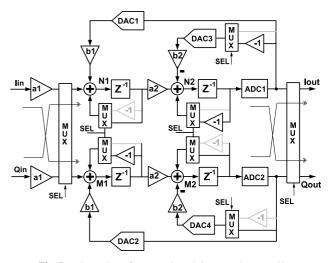

Figure 2 shows a conventional configuration of a discretetime second-order complex bandpass  $\Delta\Sigma$ AD modulator [8], which is composed of a second-order complex bandpass filter, two 3-bit ADCs and four 3-bit DACs. Multi-bit ADCs/DACs are used inside the modulator to obtain high SNR with a low-order loop filter and relax the required performance for OP-Amps. MUXs and data-weighted averaging (DWA) logic circuits [5]–[7] are added to reduce the effect of nonlinearities of multi-bit DACs inside the modulator.

The input and output of the complex bandpass  $\Delta\Sigma AD$  modulator shown in Fig. 2 are given by

$$\begin{aligned} & \int J_{out} + j Q_{out} \\ &= z^{-2} \bigg[ \frac{1}{2} (I_{in} + j Q_{in}) + (z - j)^2 (E_I + j E_Q) \bigg]. \end{aligned}$$

Internal signals in Fig. 2 can be written as follows:

j

$$I_{1}(n+1) = a_{1} \cdot I_{in}(n+1) + b_{1} \cdot DAC1(n+1) - Q_{1}(n)$$

(3)

$$Q_{1}(n+1) = a_{1} \cdot Q_{in}(n+1) + b_{1} \cdot DAC2(n+1) + I_{1}(n)$$

(4)

$$I_2(n+1) = a_2 \cdot I_1(n)$$

$$+ b_2 \cdot DAC3(n+1) - Q2(n)$$

(5)

$$Q_2(n+1) = a_2 \cdot Q_2(n)$$

+

$$b_2 \cdot DAC4(n+1) + I_2(n)$$

. (6)

Here, the inputs of DAC1 and DAC4 are fedback from the

**Fig. 2** Conventional discrete-time second-order complex bandpass  $\Delta\Sigma$ AD modulator. (Here  $a_1 = 1/3$ ,  $b_1 = -2/3$ ,  $a_2 = 3/2$ ,  $b_2 = 2$ )

output of ADCI, while the inputs of DAC2 and DAC3 are fedback from the output of ADCQ.

The following two problems arise when implementing the conventional configuration in Fig. 2.

#### 1. Complexity of chip layout design:

There are many I and Q signal crossing lines in the complex bandpass  $\Delta\Sigma$ AD modulator as shown in Fig. 2. There are not only signal crossings between the I and Q paths of the complex filter in the forward paths, but also signal crossings between the feedback paths from ADCs through four DACs in I and Q paths. As their result, the signal lines become long, which leads to large chip area, and crosstalk may occur, and also large power dissipation may be needed to drive large parasitic capacitances.

#### 2. Mismatches between I and Q paths:

Mismatches between forward I and Q paths cause an image signal in Fig. 2, and the quantization noise of the mirror image band aliases into the design signal band, which degrades the modulator SNR (see Appendix). Some ideas [10]–[13] have been proposed to reduce their influence, but they are not very suitable for our modulator structure.

Therefore, we propose a new architecture of a complex bandpass  $\Delta\Sigma AD$  modulator to solve the above two problems, and we have conducted MATLAB simulations to verify its effectiveness.

**Remark** The effect of mismatches among DACs in feedback paths can be reduced by our already proposed DWA algorithm [5], [6] because it alternates the DACs for I and Q paths every sample cycle, and hence it is not a problem here.

#### 4. Proposed Structure of Complex Bandpass $\Delta\Sigma AD$ Modulator

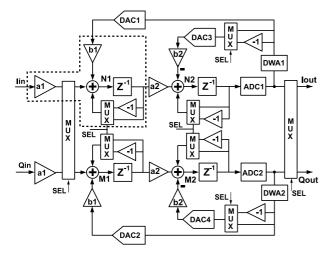

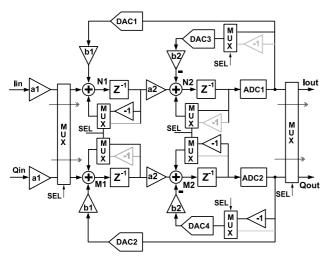

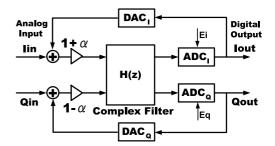

Figure 3 shows the structure of our proposed complex bandpass  $\Delta\Sigma$ AD modulator. First, we will show that the proposed structure is equivalent to the conventional one shown in Fig. 2 when their circuits are ideal (no mismatches).

At time

$$n = 2k - 1$$

(Fig. 4):

Fig. 3 Proposed structure of a complex bandpass  $\Delta\Sigma$ AD modulator.

**Fig. 4** Operation of proposed modulator (at time n = 2k - 1).

The input analog signal for the *upper* part circuits is  $I_{in}$  while the one for the *lower* part circuits is  $Q_{in}$ . Also the output digital signal from the *upper* part ADC1 is  $I_{out}$ , while the one from the *lower* part ADC2 is  $Q_{out}$ . Then the internal signals relationship is given as follows:

$$N_{1}(2k) = a_{1} \cdot I_{in}(2k) + b_{1} \cdot DAC1(2k) - N_{1}(2k-1)$$

(7)

$$M_1(2k) = a_1 \cdot Q_{in}(2k)$$

$$+ b_{-} DAC2(2k) + M(2k - 1)$$

(9)

$$+ b_1 \cdot DAC2(2k) + M_1(2k-1)$$

$$V_2(2k) = a_2 \cdot N_1(2k-1)$$

(8)

$$+ b_2 \cdot DAC2(2k) + N_2(2k-1) \tag{9}$$

$$M_2(2k) = a_2 \cdot M_1(2k-1) + b_2 \cdot DAC4(2k) - M_2(2k-1)$$

(10)

Here

Let

Δ

$$k = \dots - 2, -1, 0, 1, 2, 3, \dots$$

**Fig. 5** Operation of proposed modulator (at time n = 2k).

$N_1(2k-1) = Q_1(2k-1)$   $M_1(2k-1) = I_1(2k-1)$   $N_2(2k-1) = I_2(2k-1)$  $M_2(2k-1) = Q_2(2k-1).$

Then we see from Fig. 4 that ADC1 output (I signal) is fedback to DAC1 and DAC3, and ADC2 output (Q signal) is to DAC2 and DAC3. Thus Eqs. (7) and (3), Eqs. (8) and (4), Eqs. (10) and (5), Eqs. (9) and (6) have the same forms respectively.

#### **At time** *n* = 2*k* (Fig. 5):

The input analog signal for the *lower* part circuits is  $I_{in}$  while the one for the *upper* part circuits is  $Q_{in}$ . Also the output digital signal from the *lower* part ADC2 is  $I_{out}$ , while the one from the *upper* part ADC1 is  $Q_{out}$ . Then we have the followings:

$$N1(2k+1) = a_1 \cdot Q_{in}(2k+1) + b_1 \cdot DAC1(2k+1) - N_1(2k)$$

(11)

$$M_1(2k+1) = a_1 \cdot I_{in}(2k+1) + b_1 \cdot DAC2(2k+1) + M_1(2k)$$

(12)

$$N_2(2k+1) = a_2 \cdot N_1(n)$$

$$+ b_2 \cdot DAC3(2k+1) + N2(2k)$$

(13)

$$M_2(2k+1) = a_2 \cdot M_1(2k)$$

+

$$b_2 \cdot DAC4(2k+1) - M_2(2k)$$

. (14)

Let

$$N_1(2k) = I_1(2k)$$

$$M_1(2k) = Q_1(2k)$$

$$N_2(2k) = Q_2(2k)$$

$$M_2(2k) = I_2(2k).$$

Similarly we see from Fig. 5) that ADC1 output (Q signal) is fedback to DAC1 and DAC3 and ADC2 output (I signal) is fedback to DAC2 and DAC3. Hence Eqs. (12) and (3), Eqs. (11) and (4), Eqs. (13) and (5), Eqs. (14) and (6) have

the same forms respectively.

From the above statements, we see that the proposed structure (Fig. 3) is equivalent to the conventional one (Fig. 2) when their circuits are ideal.

Also we see from Fig. 3 that the proposed structure has no crossing signal lines for either the forward paths of  $Z^{-1}$ block or the feedback paths from DACs, which is different from the conventional modulator in Fig. 2. Hence the proposed modulator can be completely divided into two separate parts and its layout design can be greatly simplified compared with the conventional one. Then its internal signal lines can be shorter, which leads to smaller chip area.

For the proposed architecture, we note that MUXs can be realized by MOS switches easily. Moreover we add MUXs which alternate the polarity of the fedback signals between +1 and -1 at every sampling time to the feedback paths of filters and DACs. This is to keep the polarity of internal complex signals so that they are processed as a complex signal form [14]. In fact we can realize this simply by chopping the two differential outputs at every sampling time.

## 5. Reduction of SNR Deterioration by I and Q Path Mismatches

We explain why our proposed structure can reduce the influence of mismatches between I and Q paths. Note that for the circuit surrounded by a dotted line in Fig. 3, we have the followings:

$$N_1(2k-1) = Q_1(2k-1)$$

while  $n = 2k-1$ ,

$N_1(2k) = I_1(2k)$  while  $n = 2k$ .

We see that ADC1 output is for  $I_{out}$  at time n = 2k - 1, and it is for  $Q_{out}$  at time n = 2k. DACs are used alternately for I and Q paths when CLK toggles. Thus the SNR degradation by mismatches between the upper and lower paths can be reduced by this dynamic matching.

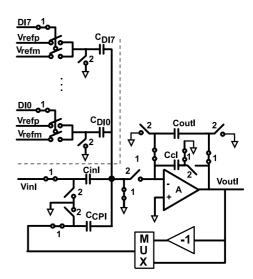

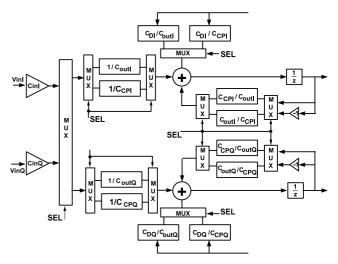

Furthermore, we propose another dynamic matching technique for SC circuits to reduce the influence of mismatches between capacitors in the complex filter. Figure 6 shows the SC implementation of a complex bandpass filter which uses  $Z^{-1}$  blocks [9] in Fig. 3.

For an ideal complex modulator shown in Fig. 6 (without any mismatches), the values of the capacitors in the complex filter in Fig. 3 should have the following relationships:

$$\frac{C_{inI}}{C_{outI}} = \frac{C_{inQ}}{C_{outQ}} (= a_1),$$

$$\frac{\sum_{n=0}^{7} C_{DIn}}{C_{outI}} = \frac{\sum_{n=0}^{7} C_{DQn}}{C_{outQ}} (= b_1),$$

$$C_{CPI} = C_{CPQ} = C_{outI} = C_{outQ}.$$

However, in real chips the ratios of the capacitances do not satisfy the above equations due to process variations, which

**Fig.6** SC implementation of proposed complex bandpass filter (which is the surrounded part by a dotted line in Fig. 3).

**Fig.7** Equivalent circuit of the proposed first-stage filter in the modulator which can reduce the influence of capacitor mismatches by dynamic matching.

cause the mismatches between I and Q paths and the modulator SNR degrades. According to this consideration, we propose to add another dynamic matching technique for the SC filter in the first stage of the modulator (Fig. 3) to reduce the influence of capacitor mismatches. The SC filter circuit operates as follows (Fig. 7):

- 1.  $C_{inI}$  and  $C_{inQ}$  are fixed for I and Q paths in the front of the input MUX. Input signals  $I_{in}$  and  $Q_{in}$  charge to  $C_{inI}$ and  $C_{inQ}$  at first, and then they transfer the charges to upper and lower paths alternately by the input MUX. This idea is based on our simulation result that the influence of mismatches in  $C_{inI}$  and  $C_{inQ}$  is small.

- 2. We exchange capacitors for  $C_{OUTI}$  and  $C_{CPI}$ ,  $C_{OUTQ}$  and  $C_{CPQ}$  very sampling time by MUXs, in order to reduce the influence of mismatches between  $C_{OUTI}$  and  $C_{CPI}$ ,  $C_{OUTQ}$  and  $C_{CPQ}$ .

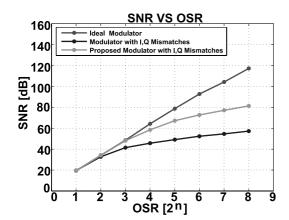

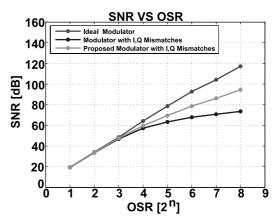

Fig. 8 Comparison for SNR of modulators in three cases. (parameter as Table 1).

With the above configuration and operation, we can reduce influence of mismatches in the modulator further. Since the influence of mismatches in the second-stage filter is smaller, we form the above operation for the first-stage only.

#### 6. Simulation of Proposed Architecture

We have conducted MATLAB simulations to confirm the effectiveness of the proposed architecture with dynamic matching. A second-order complex bandpass modulator with internal ADCs/DACs of 9-level resolution (in Fig. 2 or Fig. 3) was used for the simulation with the following three cases:

- 1. An ideal modulator (in Figs. 2, 3) without any mismatches and nonlinearities between I and Q paths is used.

- 2. A modulator in Fig. 2 with I and Q paths mismatches, and internal DACs with nonlinearities is used.

- 3. A modulator which employs the proposed architecture (in Fig. 3) and whose mismatches and nonlinearities are the same as case 2 is used.

Figure 8 shows the simulation result comparison for SNR of the modulators in three cases. We see that in case 1, SNR of the ADC increases as OSR increases. However in case 2 (where mismatch parameters between I and Q paths are shown in Table 1), SNR saturates as OSR increases. On the other hand, in case 3, the mismatch effects are out of signal band by dynamic matching and their influence on the modulator accuracy is reduced which leads to SNR improvement. Also Fig. 9 shows the simulation result comparison for SNR of the modulators with ideal DACs, where mismatch parameters are shown in Table 2.

#### 7. Conclusion

We have proposed a new architecture of a multibit complex bandpass  $\Delta\Sigma AD$  modulator which is built by switchedcapacitor circuits targeted for low-IF receivers applications in Bluetooth and WLAN. The influence of mismatches between I and Q paths to SNR is reduced by adding some

Table 1 Parameter 1 for capacitor mismatches between I and Q paths.

|             | I            | Q           |

|-------------|--------------|-------------|

| $C_{in}$    | (1-0.023)*1  | (1-0.023)*1 |

| Cout        | (1+0.014)*3  | (1-0.028)*3 |

| $C_{CP}$    | (1-0.035)*3  | (1+0.028)*3 |

| $C_{D0}$    | (1-0.0004)*2 | (1-0.018)*2 |

| $C_{D1}$    | (1-0.0014)*2 | (1+0.014)*2 |

| $C_{D2}$    | (1+0.0018)*2 | (1+0.008)*2 |

| $C_{D3}$    | (1-0.0006)*2 | (1+0.014)*2 |

| $C_{D4}$    | (1+0.0012)*2 | (1+0.012)*2 |

| $C_{D5}$    | (1+0.0012)*2 | (1-0.006)*2 |

| $C_{D6}$    | (1-0.018)*2  | (1-0.024)*2 |

| <i>CD</i> 7 | (1-0.000)*2  | (1+0.000)*2 |

**Fig.9** Comparison for SNR of modulators with ideal DACs in three cases. (parameter as Table 2).

Table 2

Parameter 2 for capacitor mismatches between I and Q paths.

|          | Ι           | Q          |

|----------|-------------|------------|

| $C_{in}$ | (1-0.03)*1  | (1+0.03)*1 |

| Cout     | (1+0.014)*3 | (1-0.03)*3 |

| $C_{CP}$ | (1-0.03)*3  | (1+0.02)*3 |

multiplexers to the modulator circuitry, which are relatively easy to implement. As another result, the modulator is divided into two separate parts without crossing of signal lines between I and Q paths and its layout design can be greatly simplified compared with conventional circuits. The validity of the proposed architecture and circuit technique has been confirmed by MATLAB simulation. As the next step, we are designing and laying out the transistor level circuits of the multi-bit complex bandpass  $\Delta\Sigma$ AD modulator with the proposed architecture and dynamic matching technique.

#### Acknowledgement

We would like to thank STARC which supports this research. Thanks are also due to T. Kozawa, E. Imaizumi, H. Sugihara, T. Komuro, I. Sakurazawa and K. Wilkinson for valuable discussions. A part of this work was performed at Gunma University Satellite Venture Business Laboratory.

#### References

- J. Crols and M. Steyeart, "Low-IF topologies for high-performance analog front ends of fully integrated receivers," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol.45, no.3, pp.269–282, March 1998.

- [2] F. Munoz, K. Philips, and A. Torralba, "A 4.7 mW 89.5 dB DR CT complex ΔΣ ADC with built-in LPF," ISSCC Digest of Technical Papers, vol.47, pp.500–501, Feb. 2004.

- [3] N. Yaghini and D. Johns, "A 43 mW CT complex ΔΣ ADC with 23 MHz of signal bandwidth and 68.8 SNDR," ISSCC Digest of Technical Papers, vol.47, pp.502–503, Feb. 2004.

- [4] S.A. Jantzi, K.W. Martin, and A.S. Sedra, "Quadrature bandpass ΣΔ modulator for digital radio," IEEE J. Solid-State Circuits, vol.32, pp.1935–1949, Dec. 1997.

- [5] H. San, H. Kobayashi, S. Kawakami, N. Kuroiwa, and H. Wada, "An element rotation algorithm for multi-bit DAC nonlinearities in complex bandpass delta-sigma AD modulators," IEEE 17th International Conference on VLSI Design, pp.151–156, Mumbai, India, Jan. 2004.

- [6] H. San, H. Kobayashi, S. Kawakami, and N. Kuroiwa, "A noiseshaping algorithm of multi-bit DAC nonlinearities in complex bandpass ΔΣAD modulators," IEICE Trans. Fundamentals, vol.E87-A, no.4, pp.792–800, April 2004.

- [7] H. Wada, H. Kobayashi, and H. San, "Mapping from a DWA algorithm into circuits for multi-bit complex bandpass ΔΣAD modulators," ECT-04-07, pp.1–6, Hakodate, Japan, June 2004.

- [8] A. Hayakawa, H. San, H. Kobayashi, Y. Jingu, and K. Kobayashi, "Design of discrete-time multi-bit complex bandpass ΔΣAD modulators," IEICE Technical Report, July 2004.

- [9] L. Longo and B. Horng, "A 15b 30 kHz bandpass sigma-delta modulator," ISSCC Digest of Technical Papers, pp.226–227, Feb. 1993.

- [10] R. Schreier, "Quadrature mismatch-shaping," Proc. ISCAS, vol.4, pp.675–678, May 2002.

- [11] J. Riches and N. Erdol, "Mismatch cancellation in quadrature bandpass ΔΣ modulators using an error shaping technique," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol.49, pp.73–85, Feb. 2002.

- [12] L. Breems, E. Dijkmans, and H. Huijsing, "A quadrature datadependent DEM algorithm to improve image rejection of a complex ΔΣ modulator," IEEE J. Solid-State Circuits, vol.36, pp.1879–1886, Dec. 2001.

- [13] R. Maurino and C. Papavassiliou, "Multibit quadrature sigma-delta modulator with DEM scheme," Proc. ISCAS, vol.1, pp.I1136–1139, May 2004.

- [14] K.W. Martin, "Complex signal processing is not complex," IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol.51, pp.1823– 1836, Sept. 2004.

### Appendix: Resolution Deterioration by I and Q Mismatches in a Complex Bandpass $\Delta\Sigma AD$ Modulator

According to the thinking of complex signal processing [14], we consider the reason to resolution (SNR) deteriorates by I and Q mismatches. We can get the relationship of complex inputs and outputs as following while the complex modulator shown in Fig. A  $\cdot$  1 without any mismatches( $\alpha = 0$ ):

$$I_{out} + jQ_{out} = \frac{H}{1+H}(I_{in} + jQ_{in}) + \frac{1}{1+H}(E_i + jE_q).$$

**Fig.** A  $\cdot$  **1** A complex AD modulator with I and Q paths mismatches as  $\alpha$ .

However, while the modulator with I and Q mismatches ( $\alpha \neq 0$ ), the equation will be written as follows:

$$\begin{split} I_{out} + jQ_{out} \\ &= \frac{H + (1 - \alpha^2)H^2}{1 + 2H + (1 - \alpha^2)H^2}(I_{in} + jQ_{in}) \\ &+ \frac{\alpha H}{1 + 2H + (1 - \alpha^2)H^2}(I_{in} - jQ_{in}) \\ &+ \frac{1 + H}{1 + 2H + (1 - \alpha^2)H^2}(E_i + jE_q) \\ &+ \frac{\alpha H}{1 + 2H + (1 - \alpha^2)H^2}(E_i - jE_q). \end{split}$$

Here, the quantization noise of image signal  $(E_i - jE_q)$  will alias into the signal band, thus damage the SNR of the modulator, and the image noise transfer function can be written as follows:

$$\frac{\alpha H}{1+2H+(1-\alpha^2)H^2}$$

**Hao San** received the B.S. degree in automation engineering from Liaoning Institute of Technology, China in 1993, and the M.S. and Dr. Eng. degrees in electronic engineering from Gunma University, Japan in 2000 and 2004 respectively. From 2000 to 2002, he worked for Kawasaki Microelectronics Inc. In 2004 he joined Gunma University and currently he is an assistant professor in Electronic Engineering Department there. He has been engaged in design of  $\Delta\Sigma$ AD converters and charge pump cir-

cuits. He is a member of the IEEE. He serves as a committee member of University LSI Design Contest on ASP-DAC 2006.

**Akira Hayakawa** received the B.S. degree and is expected to receive the M.S. degree in electronic engineering from Gunma University in 2004 and 2006 respectively. He is currently a graduate student there, and his research interests are  $\Delta\Sigma$  AD modulators and SAR ADCs.

Yoshitaka Jingu received the B.S. degree and is expected to receive the M.S. degree in electrical engineering from Gunma University in 2004 and 2006 respectively. Currently he is a graduate student there, and he has been involved in research for complex bandpass  $\Delta\Sigma AD$  modulators and continuous-time analog filters.

Tatsuji Matsuura received the B.E. and M.E. degrees in mathematical engineering and instrumentation physics from the University of Tokyo, Tokyo, Japan, in 1976 and 1978 respectively. He joined the Central Research Lab. Hitachi, Ltd, in 1978 where he has been engaged in the research and development of pictureprocessing LSIs and high-speed A/D and D/A converters. Since 1995, he has been with the Semiconductor & Integrated Circuit Group, Hitachi, Ltd. Since 2004, he is in Renesas Tech-

nology, where he is a chief engineer. He is a member of the IEICE and IEEE. He served as a technical program committee member of CICC (Custom Integrated Circuit Conference) for analog sub-committee since 1996 to 2003. Since 2005, he serves as a technical program committee member of ISSCC(International Solid-State Circuit Conference).

received the B.S. degree and is expected to receive the M.S. degree in electronic engineering from Gunma University in 2004 and 2006 respectively. He is a currently graduate student there, and he has been involved in development of a complex bandpass  $\Delta\Sigma$  AD modulator.

Hiroki Wada

Hiroyuki Hagiwara was born in Gunma, Japan on Oct. 5, 1981, and he received the B.S. degree in electronic engineering from Gunma University in 2004. Now he is a graduate student there and his research interests lie in multibit  $\Delta\Sigma$ AD/DA modulators.

Kouichi Yahagi received the B.E. degree in electronic engineering from Tokyo University of Agriculture and Technology, Tokyo, Japan in 1988. Since he joined Hitachi, Ltd. in 1988, he has involved in the development of various analog and analog-digital mixed ICs. Currently he is in Renesas Technology Corp. where he leads a RF transceiver design team for wireless communications.

Junya Kudoh received the B.E. degree in electrical engineering from Waseda University, Tokyo Japan in 1991. He joined Device Development Center of Hitachi, Ltd. in 1991. Currently he is in Advanced Analog Development Div. of Renesas Technology Corp. and engaged in development of analog circuits. His interests include the design of analog-to-digital conversion circuits and architectures.

Kazuyuki Kobayashi received the B.S. degree in electronic engineering from Gunma University in 2005. In April 2005, he joined Sanyo LSI Design · System Soft Co. Ltd.. His research interests include analog integrated circuit design.

Haruo Kobayashi received the B.S. and M.S. degrees in information physics from University of Tokyo in 1980 and 1982 respectively, the M.S. degree in electrical engineering from University of California at Los Angeles (UCLA) in 1989, and the Dr.Eng. degree in electrical engineering from Waseda University in 1995. He joined Yokogawa Electric Corp. Tokyo, Japan in 1982, where he was engaged in the research and development related to measuring instruments and mini-supercomputers. From 1994 to

1997, he was involved in research and development of ultra-high-speed ADCs/DACs at Teratec Corp. In 1997 he joined Gunma University and presently is a Professor in Electronic Engineering Department there. He was also an adjunct lecturer at Waseda University from 1994 to 1997. His research interests include analog & digital integrated circuits design and signal processing algorithms. He received Yokoyama Award in Science and Technology in 2003, and the Best Paper Award from the Japanese Neural Network Society in 1994.

IEE of Japan.

Hideo Nakane received the B.E. and M.E. degrees in Electrical Engineering and Computer Science, Kumamoto University, Kumamoto, Japan in 1998 and 2000, respectively. And he received D.Eng. in Graduate School of Science and Technology, Kumamoto University in 2003. He joined Semiconductor & Integrated Circuit Group, Hitachi, Ltd. in 2003. Since 2004, he is in Renesas Technology Corp., and engaged in A/D converter design for radio communications. He is a member of the IEEE and

Masao Hotta received the Ph.D. degree in electronics from Hokkaido University, Sapporo, Japan, in 1976. In 1976 he was with the Central Research Laboratory, Hitachi Ltd., Tokyo, Japan. He engaged in research and development of on high-precision D/A converters, ultra-highspeed D/A converters and high-speed A/D converters. From 1996 to 2003, he was a Manager of Advanced Device Development Department and also a Senior Chief Engineer & Senior Manager of Advanced Analog Technology Cen-

ter, Semiconductor & Integrated Circuits Division of Hitachi Ltd. He has worked on the development of microprocessors, memories, RF devices, and DA/CAD systems. From 2003 to 2005, he was a General Manager of Advanced Analog Technology Division, Renesas Technology Corp. He conducted development on RF power amplifier modules, RF transceiver LSIs, mixed-signal LSIs and advanced analog cores for SoC. Since 2005, he has been a Professor at Musashi Institute of Technology, working on high performance ADCs, mixed-signal LSI design and wireless systems. Dr. Hotta has served as a chair of Technical Committee on Circuits and Systems, IEICE, a technical program committee co-chair of ITC-CSCC2000 and technical program committees of CICC, BCTM and ASIC/SOC Conference. He is a chair of IEEE Circuits and Systems Society Japan Chapter, and he is a fellow of IEEE.

**Toshiro Tsukada** received the B.E., M.E. and D.Eng. degrees in electrical engineering from the University of Tokyo, in 1971, 1973, and 1995 respectively. Since joining the Central Research Laboratory, Hitachi, Ltd. in 1973, he has been involved in the research and development of MOS analog and mixed-signal integrated circuits. From 1980 to 1981 he worked on MOS analog circuits as a research associate in the Electronics Research Laboratory, University of California, Berkeley, and worked on inte-

grated communication circuits at the Telecommunications Division of Hitachi (1988–1993). Since 1995, he has been in Semiconductor & Integrated Circuits of Hitachi and in the Advanced Analog Development Department, Renesas Technology Corporation. He is currently working as a senior manager in the Low Power Technology Group of Semiconductor Technology Academic Research Center (STARC), Yokohama.

Koichiro Mashiko received the B.S. and M.S. degrees in physics from the University of Tokyo, Tokyo, Japan, in 1975 and 1977 respectively. He received the Ph.D. degree in electrical engineering from Osaka University, Osaka, Japan, in 1988. He joined the LSI Laboratory, Mitsubishi Electric Corporation, Itami, Hyogo, Japan, in 1977. There he was engaged in the research and development of dynamic RAM's from 64 kbit to 4 Mbit, 256 kbit dual-port video RAM, cache controller chips, neural network

chips, and so on. From 1990 to 1993, he was with Mitsubishi Electric Research Laboratories, Inc., Cambridge, MA. U.S.A. There he was engaged in the establishment of the new laboratory and collaboration with universities. In 1993, he transferred to the System LSI Laboratory, Mitsubishi Electric Corporation, Itami, Japan, where he was engaged in the research and development of high-speed logic circuits and low-voltage/low-power circuit technologies. In 2002, he joined STARC (Semiconductor Technology Academic Research Center), Yokohama, Japan, where he has been promoting the collaboration between universities and industry in SoC design area, in particular analog and RF circuit technologies. He is a member of IEEE. He served as a member of Technical Program Committee for IEEE VLSI Circuit Symposium and for IEEE CICC from 1994 to 1997 and from 1998 to 2001, respectively. He also served as Chair and Vice Chair of Analog and RF Subcommittee for ASP-DAC 2004 and 2005, respectively.

Atsushi Wada received the B.S. degree in physics from Kyoto University, Kyoto, Japan, in 1987. Since 1987, he has been with SANYO Electric Co., Ltd., where he has been engaged in research and development of memories, A/D converters, and CMOS analog circuits. He served as a member of Technical Program Committee for IEEE VLSI Circuit Symposium from 1998 to 2002. He is currently working as General Manager of Mixed Signal Department in Frontier Device Research Center, SANYO Elec-

tric Co., Ltd., Gifu, Japan.