2009年3月20日

電子情報通信学会 全国大会(愛媛大) チュートリアル

## 広帯域デルタシグマAD変換器

小林春夫、元澤篤史、上森将文 林海軍、田邉朋之、傘 昊、小長谷肇 群馬大学大学院 電気電子工学専攻

# 広帯域デルタシグマAD変換器

#### 2つのアプローチ

- 高次・マルチビットを用いた 離散時間変調器

- 高速サンプリング可能な 連続時間変調器

このチュートリアルでは後者を解説する。

## 発表内容

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパス∆∑AD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

## 発表内容

- ◆ ナノCMOSとΔ∑AD変換器

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

## デジタル・アシスト・アナログ技術

CMOS微細化にともない

- デジタルは大きな恩恵

- 高集積化、低消費電力化、高速化、低コスト化

- アナログは必ずしも恩恵を受けない 電源電圧低下、出力抵抗小、ノイズ増大

- 「デジタル技術を用いて アナログ性能向上する技術」が重要

- 「デジタルリッチ・アナログミニマムな構成」が重要

# 上ナノCMOS時代のアナログ技術

「デジタルリッチ」(空間)

「高速サンプリング」(時間)

ナノCMOS FETの余裕ある高速特性、 高周波特性を生かす設計が重要。

## ナノCMOSでの 高速サンプリング技術

高速サンプリングにより

- (1) 電源ノイズ、基板ノイズ、量子化ノイズ、ジッタ等の 折り返しノイズ低減

- (2) アナログフィルタの簡単化

- (3) 従来サンプリングが用いられなかったアナログ回路にも使用可能になる

## デルタ・シグマAD変調技術

- アナログ最小、デジタルリッチな構成 ナノCMOSではデジタルは大きな恩恵

- スピードを精度に変換 ナノCMOSではスピードに余裕

- 高精度なデバイス、回路不要

ナノCMOSで高精度なADCを 実現するのに適した構成

## 発表内容

- ナノCMOSとΔ∑AD変換器

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

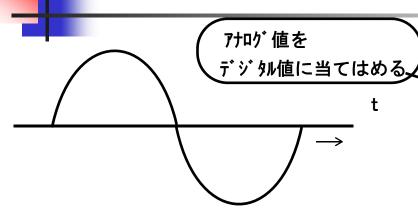

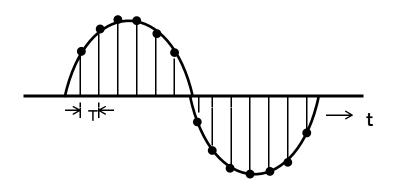

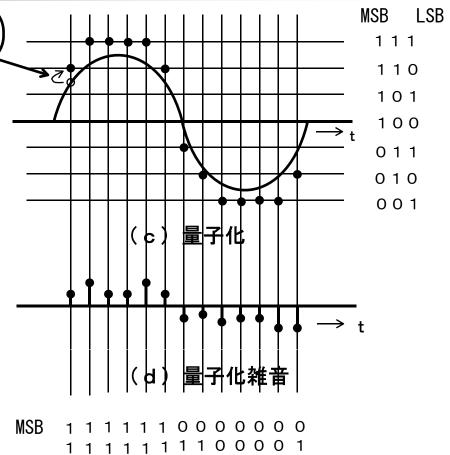

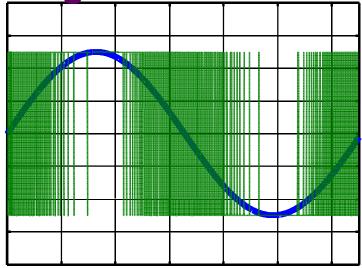

#### アナログ -> デジタル 変換波形

(a)アナログ入力

(b)標本化

LSB 0 1 1 1 1 0 1 0 1 1 1 1 0

(e)符号化

オーバーサンプリングにより入力信号 の再現性が高まる

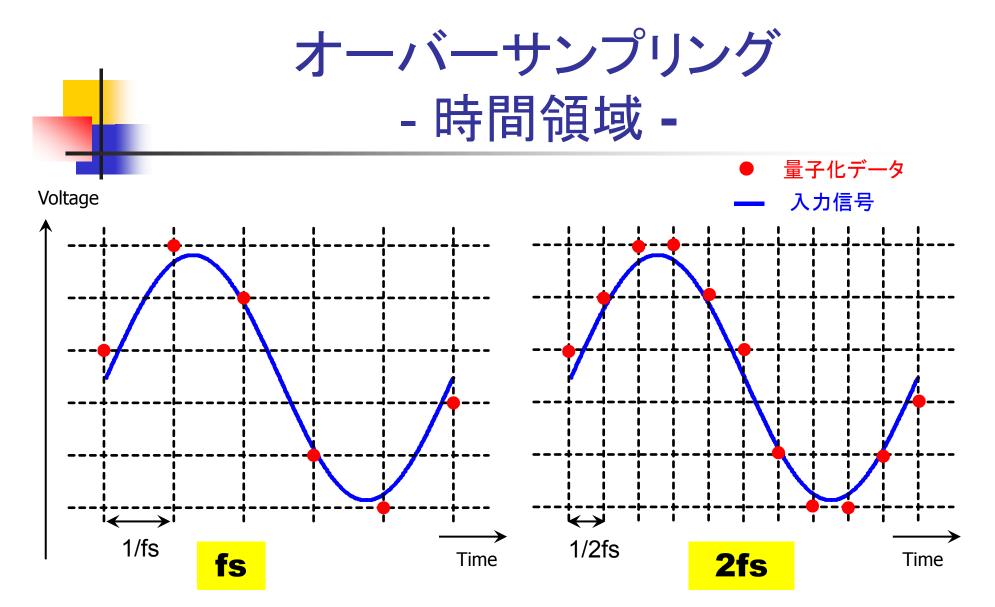

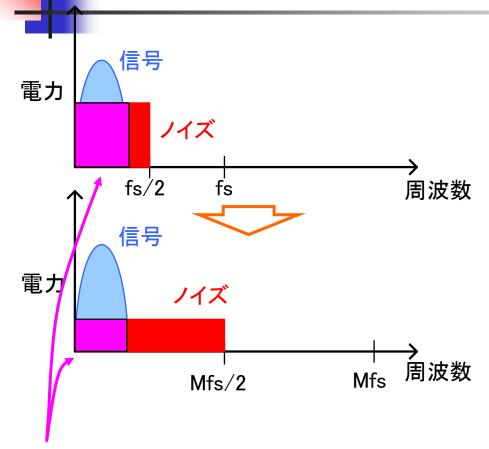

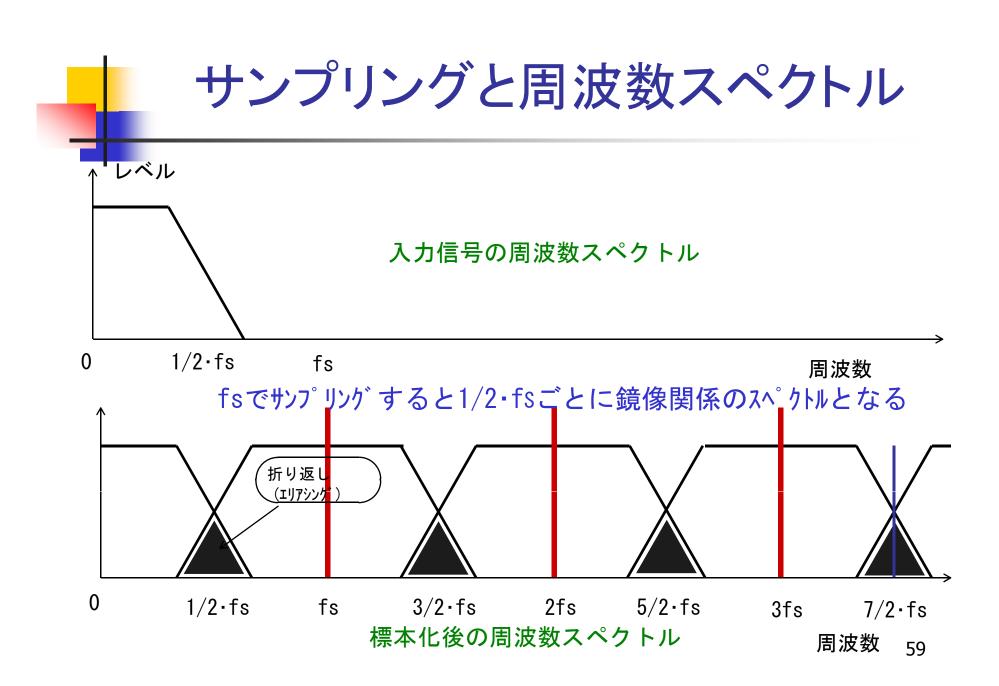

# オーバーサンプリング - 周波数領域 -

サンプリング周波数fsをM倍

↓

ノイズ 広域に分散

ただし、ノイズ総量は変わらない

「信号帯域でノイズ低減

信号帯域のノイズ成分

高速サンプリングにより低ノイズ化

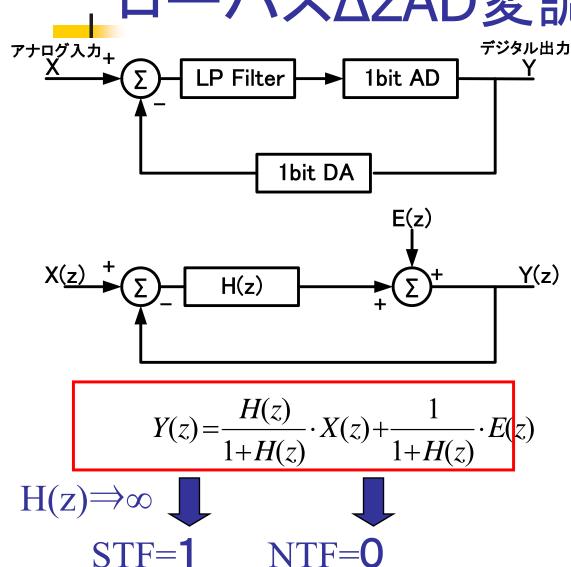

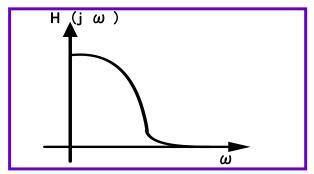

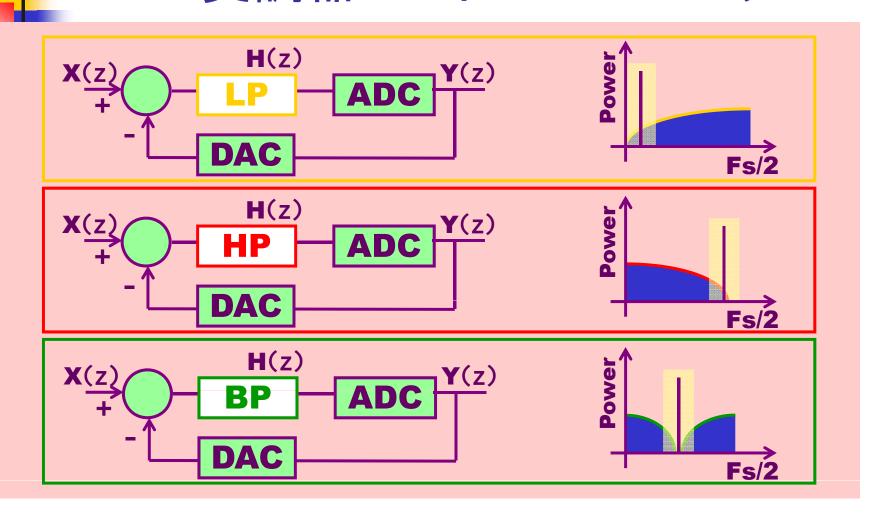

## ローパスΔΣAD変調器

⇒ 高SNRを実現

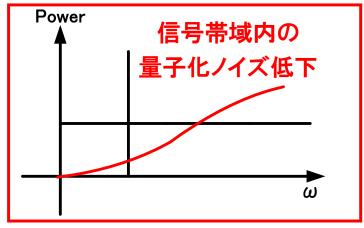

## ΔΣAD変調器とノイズシェーピング

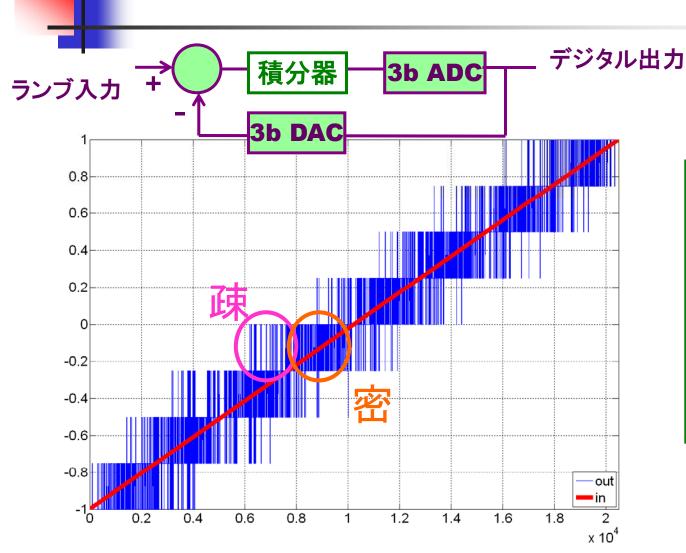

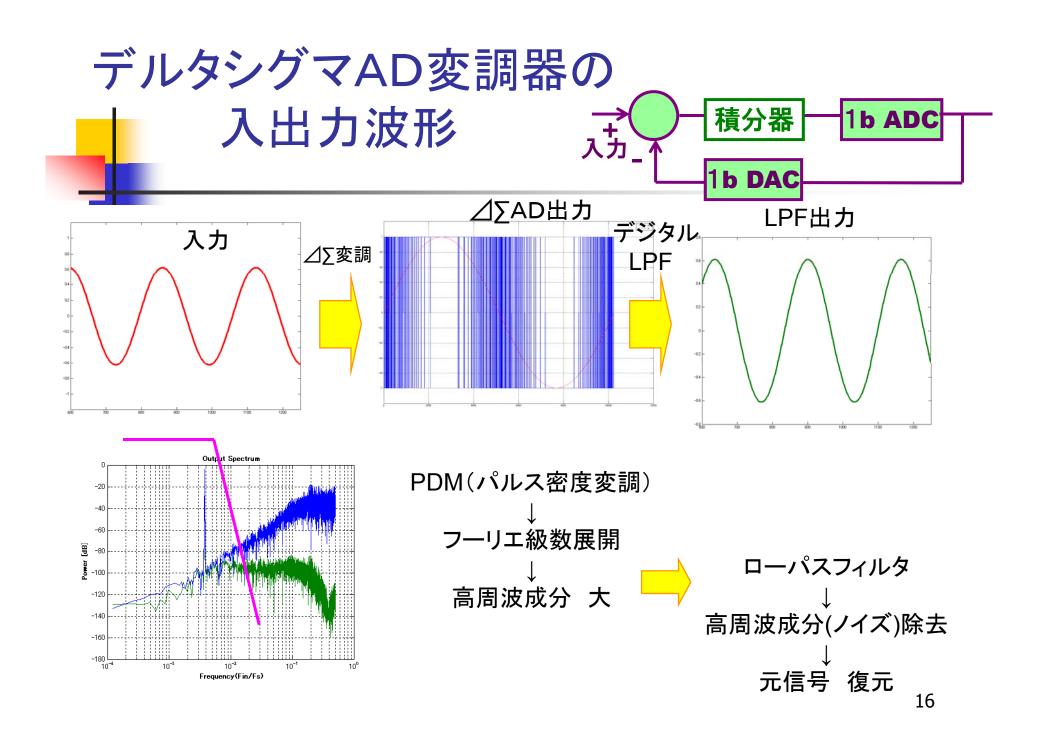

## デルタシグマ変調による高精度化

内部のADC は低分解能

疎密により より細かい デジタル値を 表現できる

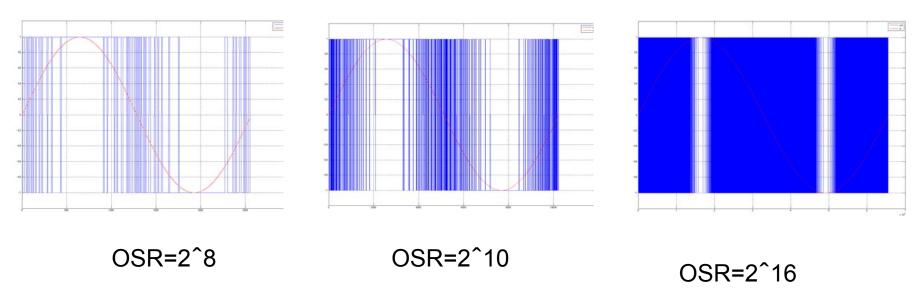

## オーバーサンプリング比 OverSampling Ratio (OSR)

OSRが大きいほどON,OFFの回数が増える ⇒細かい値が表現可能。

## 発表内容

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

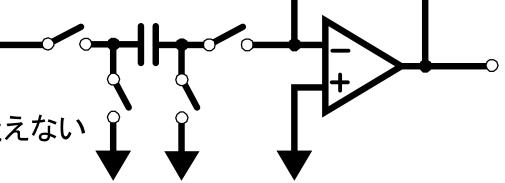

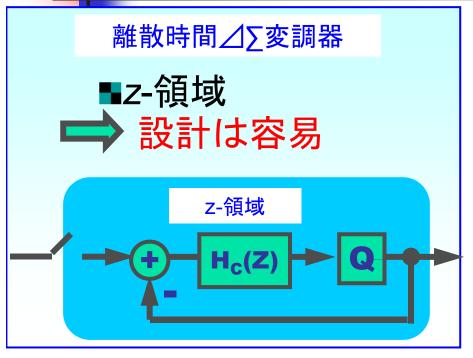

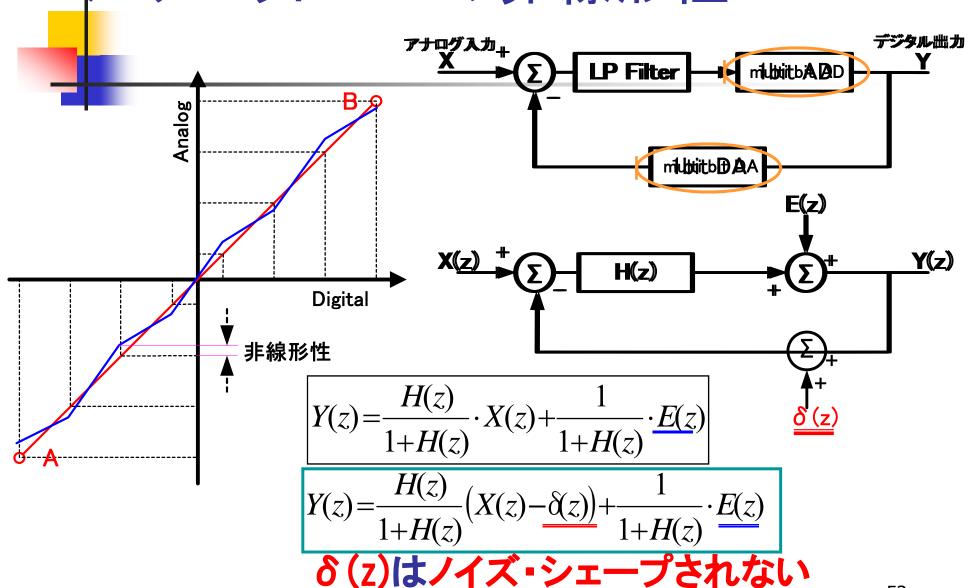

#### ΔΣAD変調器の構成

- 離散時間ΔΣAD変調器

- 高精度

- 消費電力大

- 低速・低周波信号しか扱えない

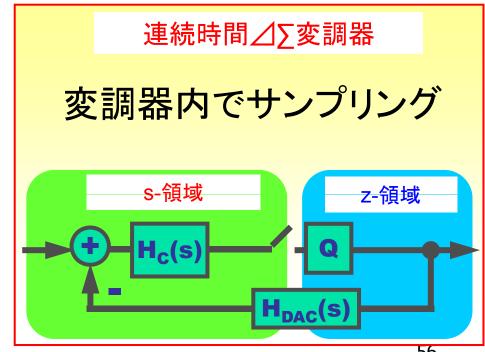

- 連続時間ΔΣAD変調器

- 低精度(DACのクロックジッタの影響大)

- 低消費電力

- 高速・高周波信号を扱える

- アンチエリアスフィルタ機能を持つ

# 4

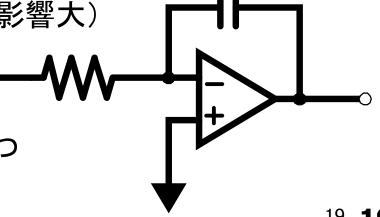

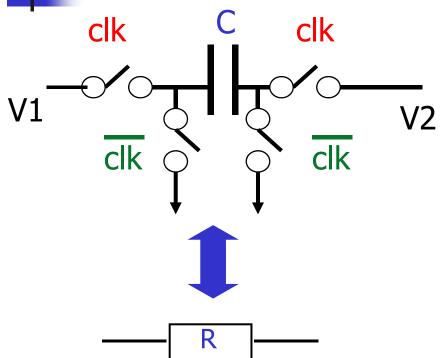

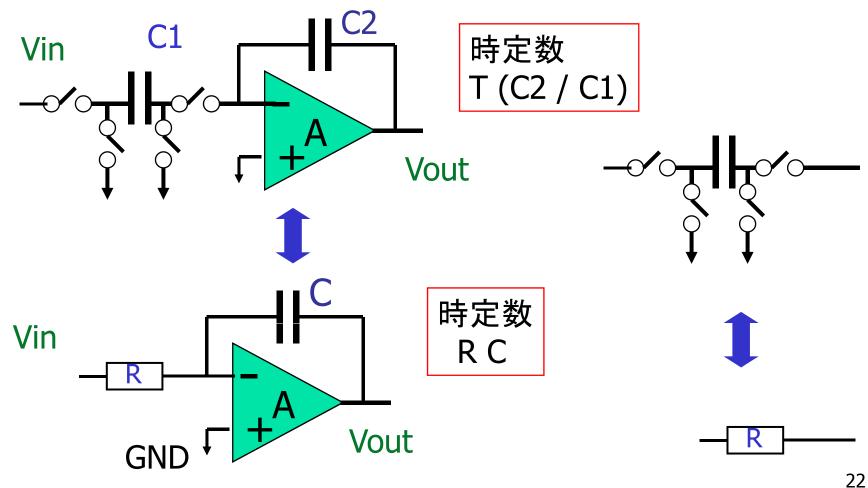

## スイッチド・キャパシタ回路

T: clk 周期

R = T / C

clk

- 容量 C と スイッチで等価的に抵抗 R を実現

- MOSスイッチ使用

- バイポーラでは実現困難

- 米国カルフォルニア大学 の大学院生が考案

- 多くの製品に使用。

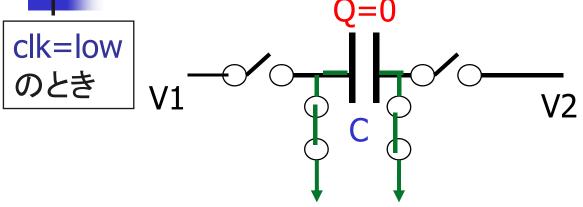

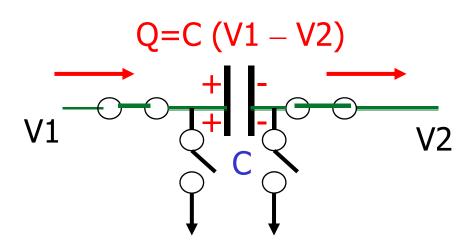

## スイッチド・キャパシタ回路の 動作原理(バタフライ型)

clk=high のとき

時間Tに電荷 Q=C (V1 - V2) が流れる。

$$I = \frac{C}{T}(V1 - V2)$$

- 1 (V1 - V2)

$$\therefore R = \frac{T}{C}$$

## スイッチド・キャパシタ回路を 用いた積分回路(バタフライ型)

- スイッチド・キャパシタ積分回路 時定数T (C2 / C1)

- クロック周期Tで制御可能

- 集積回路内では C2 / C1 は高精度に実現可能 集積回路内では 絶対精度は良くないが 比精度は良い。

- C2 / C1 の値は温度が変化しても一定

- 連続時間積分回路 時定数 RC

- 集積回路内でRC の値の高精度な実現が困難

- RC の値は温度が変化すると変わる。

- デジタル信号: 信号レベルの量子化(離散信号レベル) 時間レベルの量子化(離散時間)

- スイッチド・キャパシタ回路

- 離散時間アナログ回路

| 信号レベル時間レベル | 連続         | 離散   |

|------------|------------|------|

| 連続         | アナログ       | PWM等 |

| <b> </b>   | スイッチドキャパシタ | デジタル |

## 変調器内連続時間フィルタの調整法

- 連続時間フィルタとして調整

- ΔΣ変調器として調整 UCSD Prof. Song Gr.

- R, C変動の少ないプロセスで無調整

## 発表内容

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- ・バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

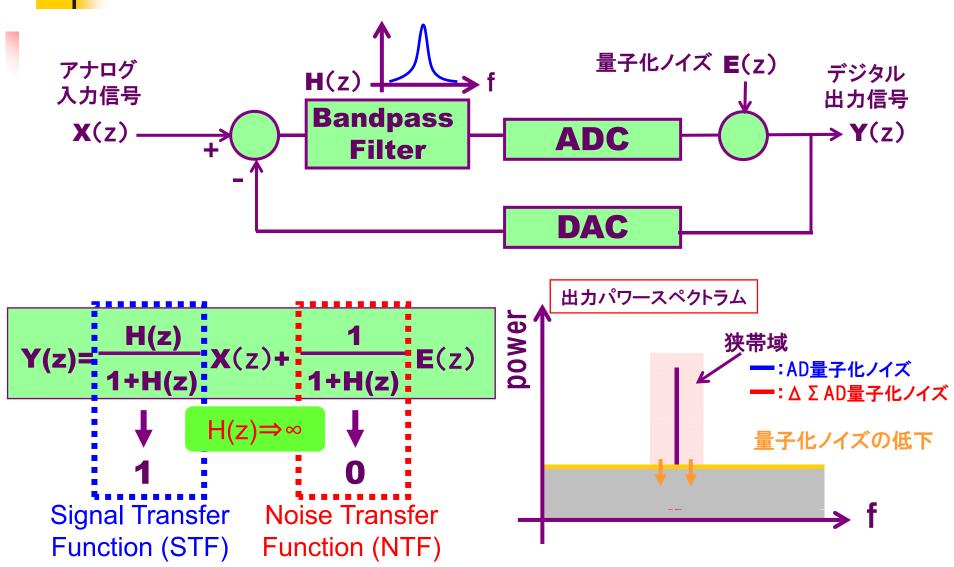

## バンドパスΔΣAD変調器

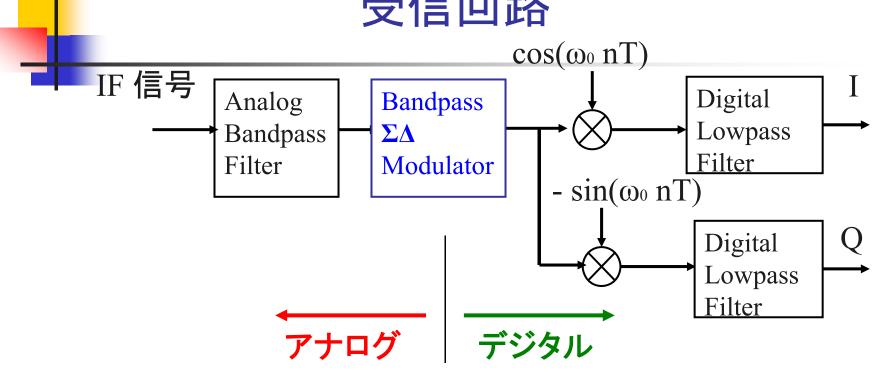

#### バンドパスΣΔ AD変調器と 受信回路

- アナログ・バンドパス・フィルタが簡単化。

- アナログ・ミキサ、アナログLO発振器が不要。

- デジタルなのでI,Q 経路のミスマッチの問題なし。

- アナログ回路は最小限でよい。

- デジタル・フィルタが必要。

#### バンドパス変調器帯域と デジタル・フィルタ

$cos(\omega_0 nT) = 1, 0, -1, 0, 1, 0, ...$  $sin(\omega_0 nT) = 0, -1, 0, 1, 0, -1, ...$

Digital Filter の 設計が容易

$ω_0/ω_s=(2k+1)/4$  でもよい。 k=0, 1, 2, ... k>0 のとき、アナログ・サブサンプリング<sup>29</sup>

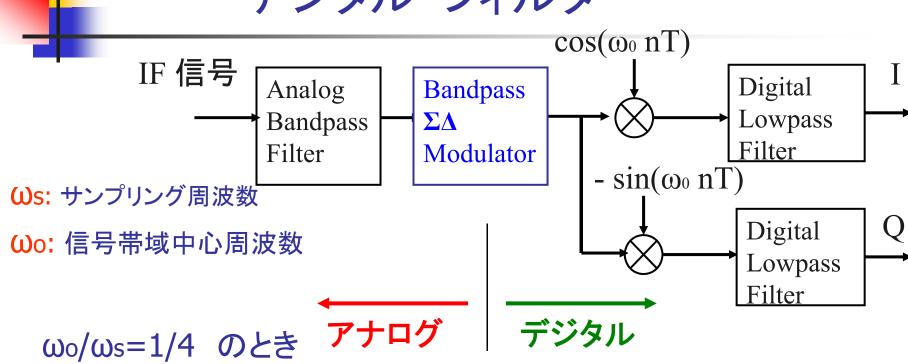

## RFサンプリング実現へ

- 携帯電話、無線LAN等の受信機アナログフロントエンド部 ⇒ソフトウェア無線

- RF信号を直接AD変換

- 低消費電力、高精度

- アナログ最小、デジタルリッチな回路構成

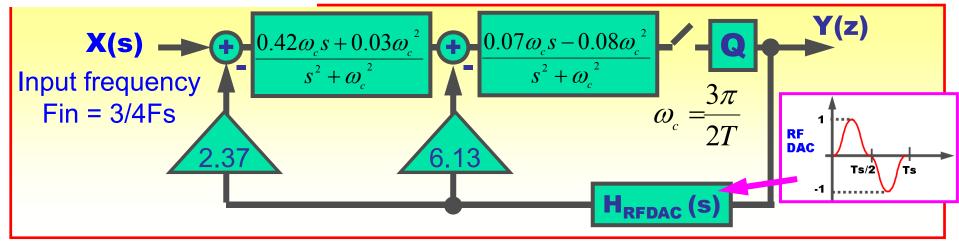

## 連続時間バンドパス変調器で RFサンプリング

- 低消費電力 ⇒ 連続時間ΔΣAD変調器

- ・ 狭帯域 ⇒ バンドパス

- 高周波 ⇒ サブサンプリング

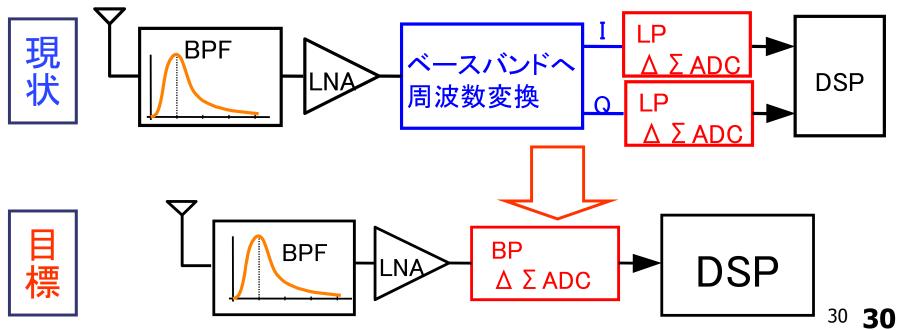

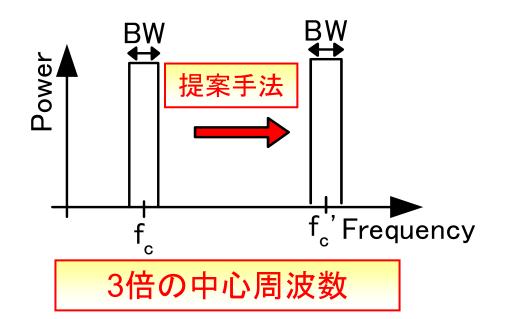

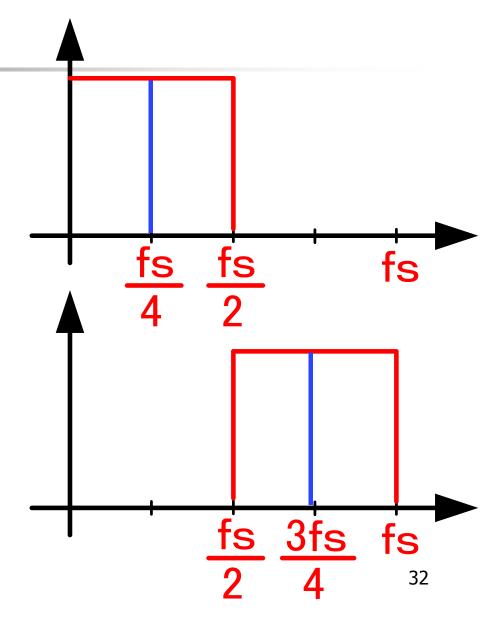

#### サブサンプリング技術

#### ナイキスト・サンプリング

■ 中心周波数: fs/4

■ 帯域 :0~fs/2

#### サブサンプリング

■ 中心周波数: 3fs/4

■ 帯域 :fs/2~fs

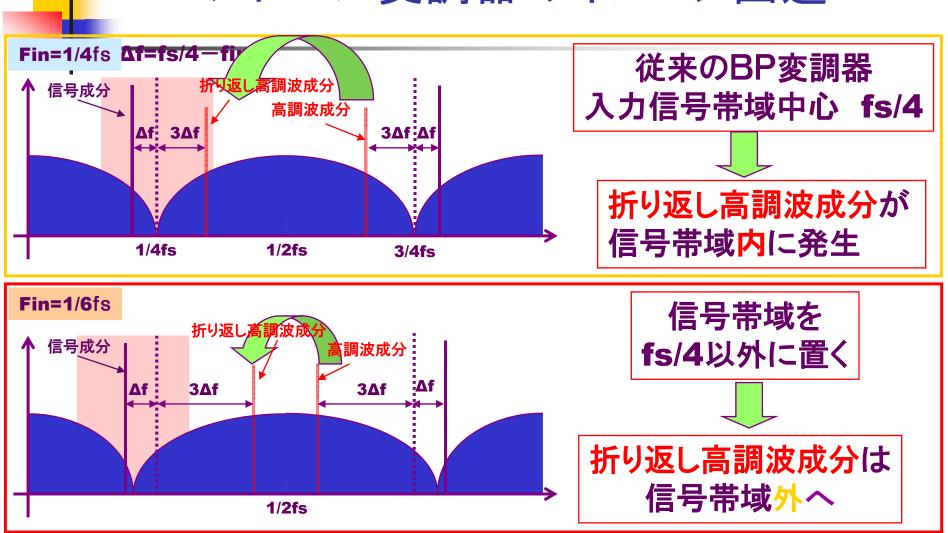

#### バンドパス変調器のイメージ回避

#### 発表内容

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

#### 広帯域 連続時間ΔΣAD変調器

- 近年、広帯域のため連続時間のΔΣADCの学会発表多し。

- 変調器内オペアンプ帯域: スイッチド・キャパシタ(SC):fsの10倍程度必要。 連続時間(CT):fsと同程度でよい。

- SCを用いた場合より10倍程度高速クロック動作可能。

連続時間ΔΣAD変調器を超低消費電力化のために 用いることもあり。

## 連続時間ΔΣAD変調器は

#### 容易に実現できる

群馬大客員教授 小室貴紀氏

大学院学生の実習 デスクルート回路試作 ノイズシェープ 波形が簡単に 得られた

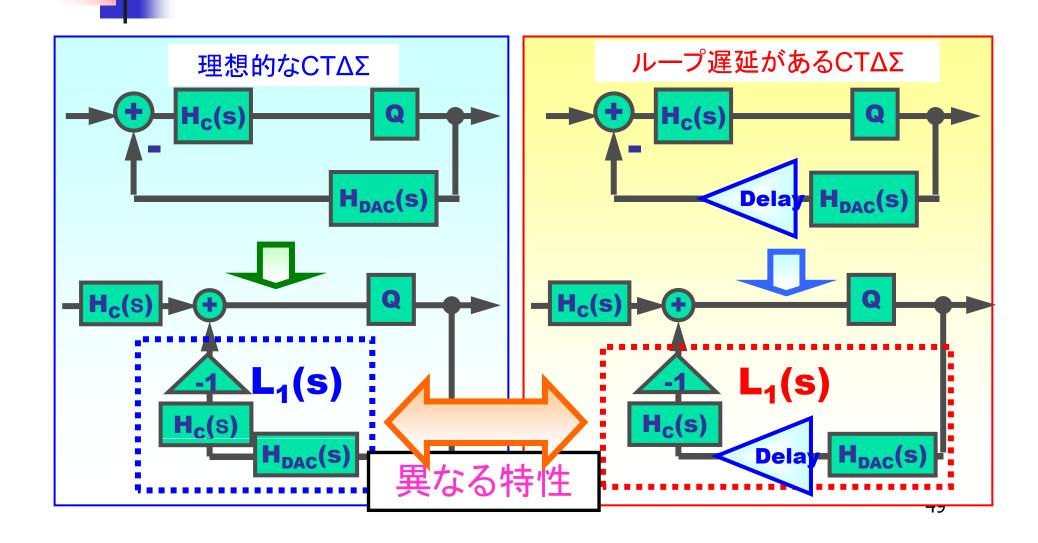

#### 連続時間ΔΣAD変調器の設計

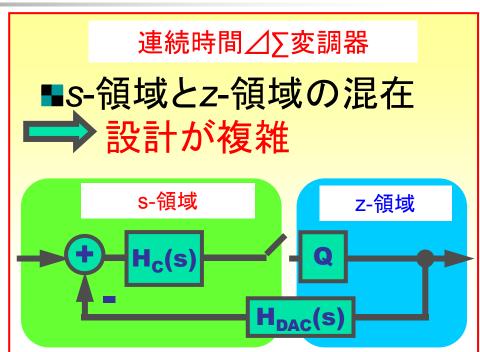

離散時間フィルタを設計し、インパルス応答不変変換を用い 連続時間フィルタへ変換する。

DACの出力時間波形も伝達関数に影響。

#### フィードバック伝達関数L<sub>1</sub>のインパルス応答

- L<sub>1</sub>のインパルス応答が不変となるCT-DT変換を求める

- L<sub>1</sub>の一致⇔ノイズ伝達関数NTFの一致

#### 連続時間ΔΣ変調器の設計例

#### 膨大な計算必要

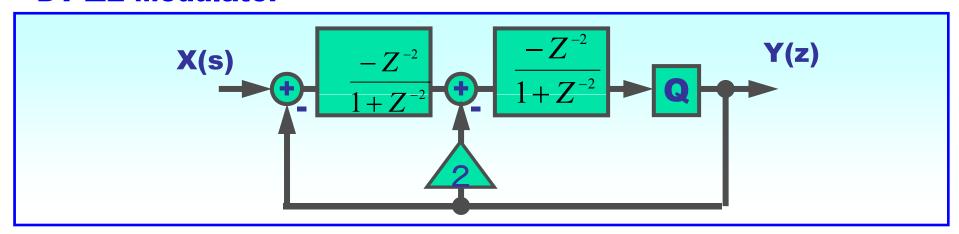

#### **DT ΔΣ Modulator**

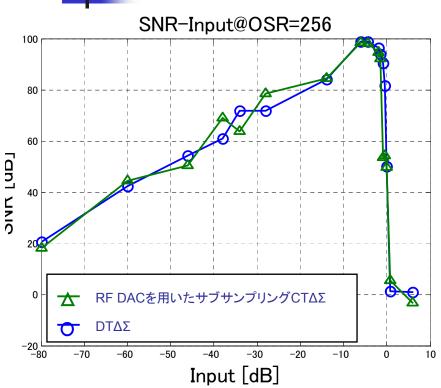

#### SNR-Input, SNR-OSRの シミュレーション結果

- ナノCMOSとΔ∑AD変換器

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

#### ● 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

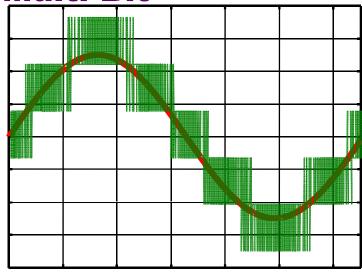

# 内部ADC/DACと フィードバックの効果

8はノイズ・シェープされない

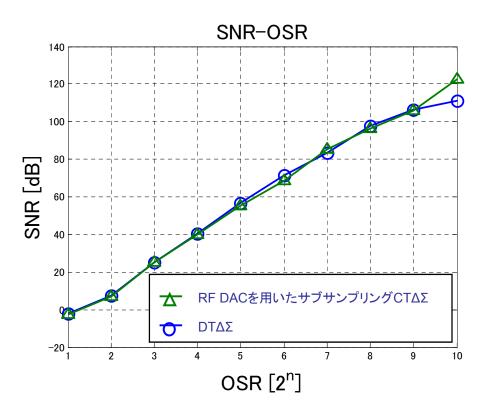

#### 変調器内部DACの出力波形

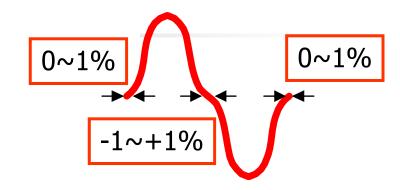

#### DACのジッタの影響

\_ ■ RF, Sine shaped DAC ⇒ DACのジッタの影響小

(サンプリングタイミングでスルーレートが0) Digital input 1 1 0 1 **NRZ DAC** 25% RTZ DAC **RF DAC** Sampling clock with jitter Clock jitter Ideal sampling clock

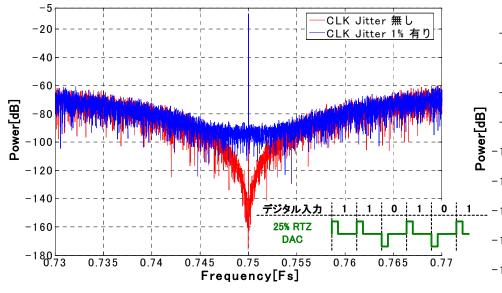

#### DACのジッタによる出力パワースペクトラム

- RF DAC使用の変調器

- 変化ほぼなし

- 25% RZ DAC使用の変調器

- ノイズフロアが大きく上昇

#### 25% RZ DAC使用の変調器

#### RF DAC使用の変調器

# DACジッタの影響の対策

- Sine-Shaped DAC, RF DACを使用。

- マルチビットDACを使用。

- スイッチドキャパシタDACを使用。

- ナノCMOSとΔ∑AD変換器

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

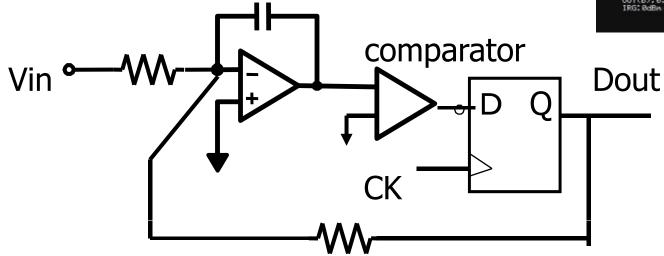

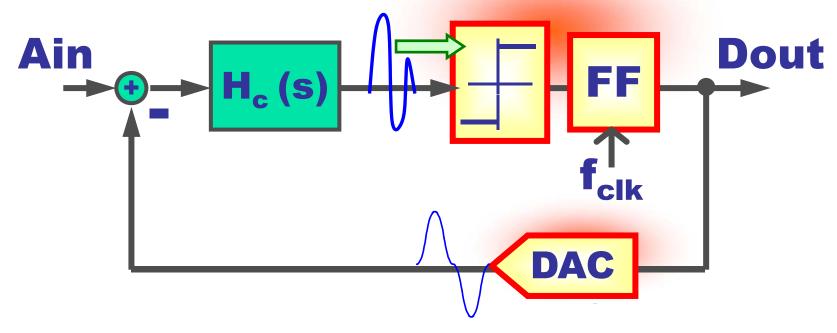

# ループ遅延(Excess Loop Delay)

- ADCとDACの間の遅延時間

- コンパレータ、フリップフロップ、DACでのトータルの遅延

- AD変換の精度劣化

# ループ遅延の影響と対策

- LPよりBPタイプのほうが影響大

- NRZ DAC より RF DAC のほうが影響大

- マルチビット化で影響軽減

- 位相進み回路で影響軽減

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

#### ΔΣ変調器内のADC/DAC

- シングルビット

- 高次フィルタが必要 (消費電力→大)

#### **Multi-Bit**

- マルチビット

- 低次フィルタで高精度(低消費電力)

- アンプのスルーレート緩和(低消費電力)

- DACのクロックジッタの影響小

- マルチビットDACの非線形性が問題

# マルチビットDACの非線形性

# 連続時間変調器の マルチビットDACの非線形性

- DWA(Data Weighted Averaging)

- ノイズシェープは難しい DACのトランジエント波形も影響するため

- 非線形性によるトーンは除去できる 別スライド参照

- DACの自己校正

- ナノCMOSとΔ∑AD変換器

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

# 連続時間変調器とサンプリング

サンプリングジッタの影響はノイズシェープ 変調器内フィルタはアンチエリアス機能

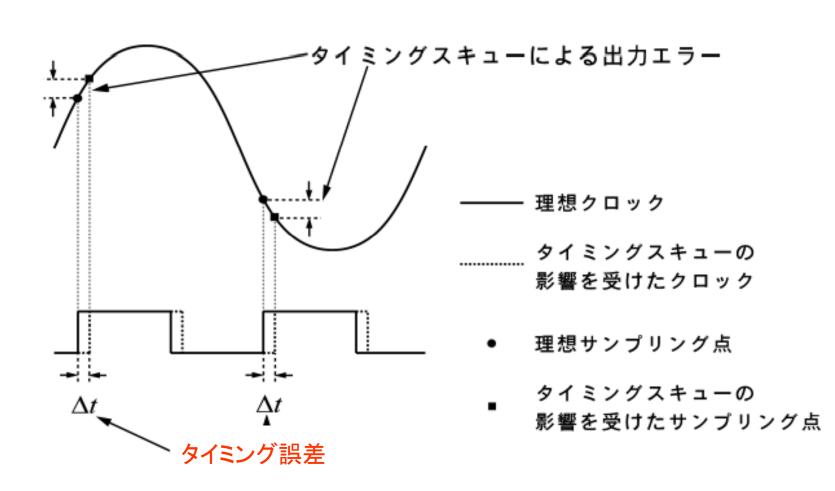

# サンプリングとタイミング誤差

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパス∆∑AD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

#### オーバーサンプリング

- アンチエリアス・アナログフィルタ要求を緩和 -サンプリング・ノイズ 入力信号スペクトル スペクトル 1倍 オーバ fs サンプリング 2倍 2fs アナログ・フィルタの 4倍 負担が軽減 高速サンプリングによりアナログフィルタ簡単化 60 4fs

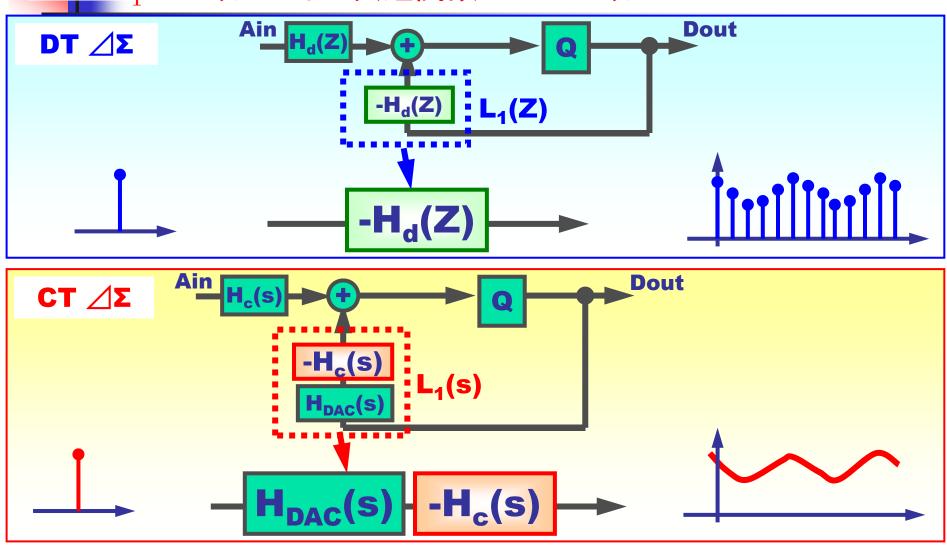

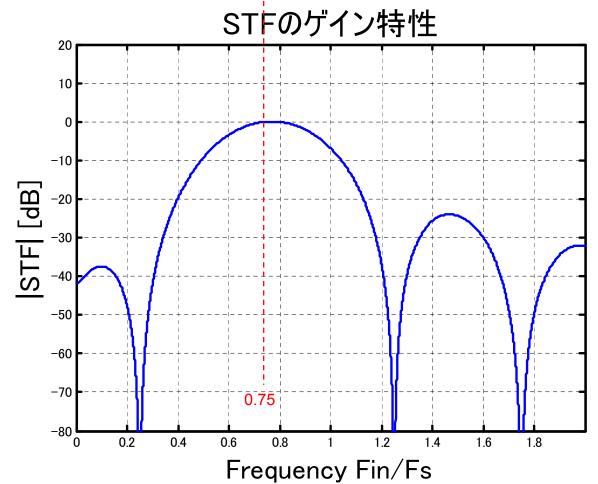

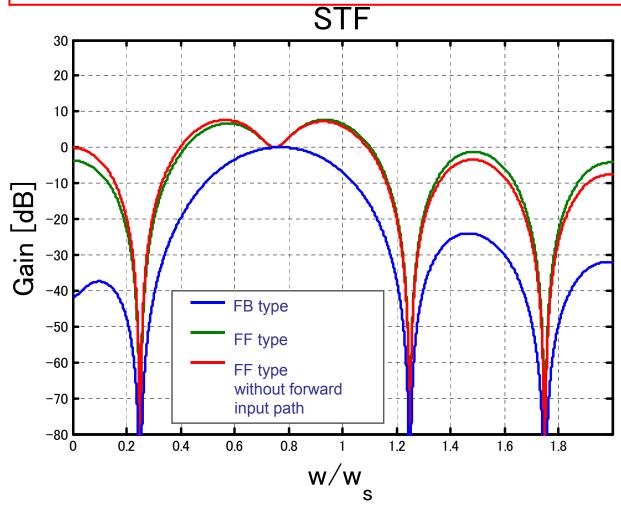

#### 信号伝達関数(STF)の周波数特性

#### アンチエイリアスフィルタ機能

4/3Fs中心のバンドパスフィルタ

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

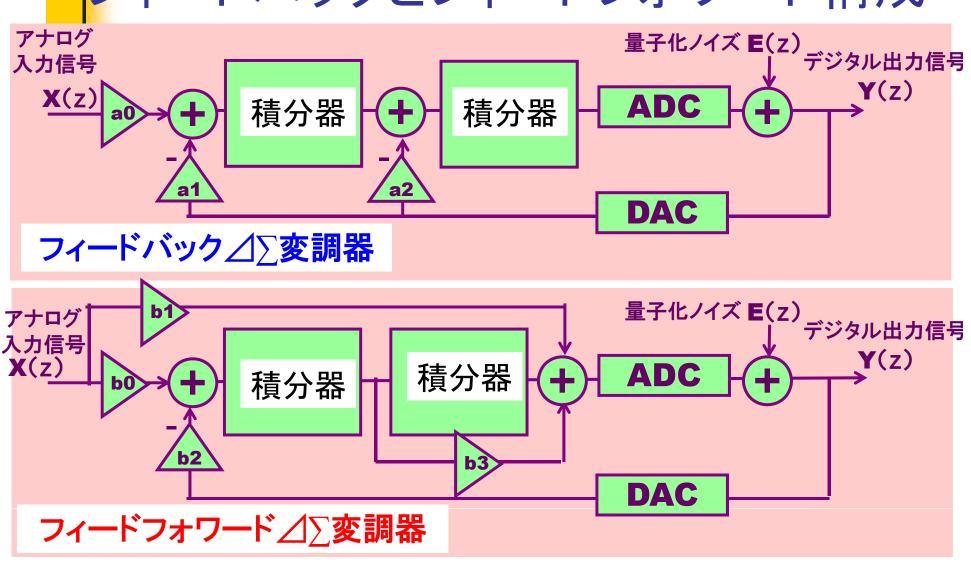

### \_フィードバックとフィードフォワード構成

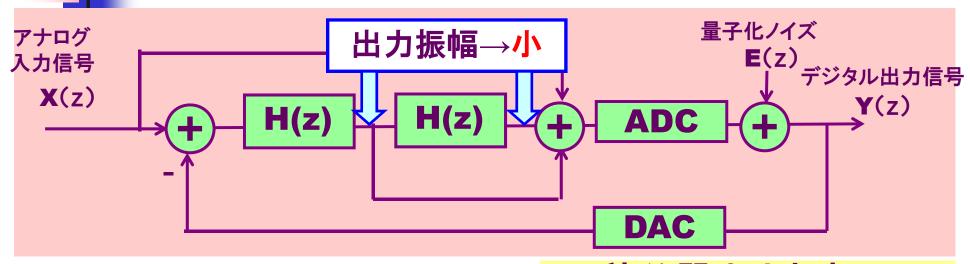

# フィードフォワードΔΣAD変調器

入力、積分器出力をフィードフォワードする構成

STF= 1

NTF=

$$\frac{1}{H^2(z)+H(z)+1}$$

積分器出力振幅→小

- •積分器の線形性向上

- •低消費電力化

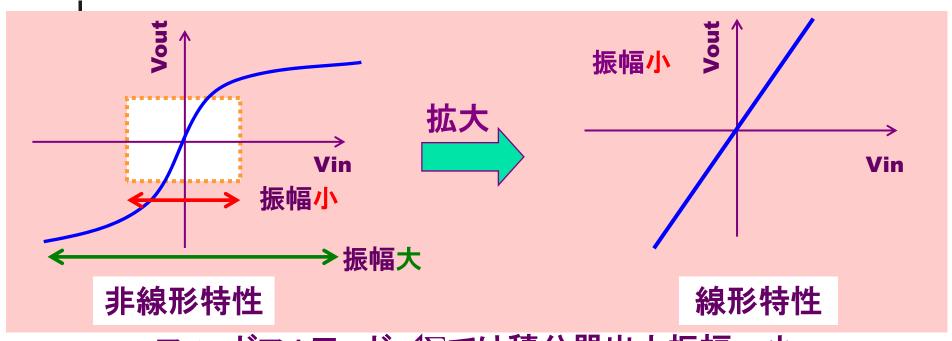

### 積分器の線形性の向上

フィードフォワード⊿∑では積分器出力振幅→小

- •高精度

- ・低消費電力化 (アンプの振幅→小)

#### 各トポロジの変調器のSTF

フィードフォワードタイプ ⇒STFのアンチエイリアシングフィルターの機能少ない

# カスケード型連続時間ΔΣ変調器

離散時間でのMASH型のような カスケード型が 連続時間変調器でも実現されている。

厳密な伝達関数の計算を基にしている。

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

### 変調器内 積分回路の構成

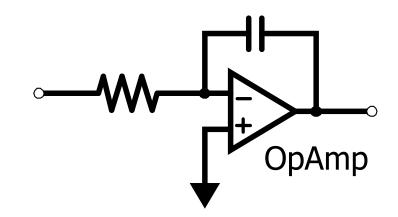

#### 能動RC回路

オペアンプ (閉ループ)

高線形性

消費電力 大

高周波動作 難

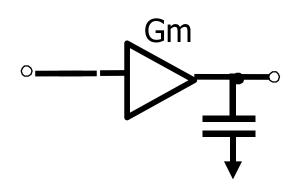

#### Gm一C回路

OTA回路 (開ループ)

低線形性

消費電力 小

高周波動作 可

### 変調器内積分回路(2)

- 線形性要求が厳しい初段に 能動RC積分回路 2段目以降に Gm-C 積分回路 を用いることが多い。

- フィードフォワード構成では 初段積分回路への要求緩和。 初段もGm-C積分回路を使用可になりえる。

# Gm-C フィルタ設計

消費電力 ノイズ 線形性 の3つのトレードオフ

### 内部フィルタのQ値

- LPタイプ変調器 LPフィルタ ではなく 積分器

- BPタイプ変調器 BPフィルタではなく 共振器

- Qが無限大が理想

- Q値が小さいとSNDRが劣化

- Qが負でもループは安定になりえる。

- サブサンプリングでは高いQ値が必要。

- **サノCMOSとΔ∑AD変換器**

- オーバーサンプリングとノイズシェープ

- 連続時間変調器と離散時間変調器

- バンドパスΔΣAD変調器

- 連続時間変調器の設計

- 内部DAC

- ループ遅延

- 内部ADC/DACのマルチビット化

- 内部ADCサンプリングジッタの影響

- 連続時間変調器のアンチエリアス特性

- フィードバックとフィードフォワード構成

- 内部の積分器の回路実現

- まとめ

# まとめ

広帯域デルタシグマAD変換器として連続時間変調器が有力。

低消費電力 高周波化 内部にアンチエリアス機能 複雑な係数計算 DACジッタの影響 ループ遅延の影響

学会レベルで問題点の解析、様々なアイデア。 産業界での実用化が期待される。