## I,Qパスを分離した複素バンドパス $\Delta\Sigma$ AD 変調器アーキテクチャ Complex Bandpass $\Delta\Sigma$ AD Modulator Architecture Without I, Q-Path Crossing Layout

傘 昊 早川 晃 神宮 善敬 和田 宏樹 萩原 広之 小林 和幸 小林 春夫 松浦 達治 † 矢萩 孝一 † 工藤 純也 † 中根 秀夫 †

群馬大学工学部電気電子工学科 〒 376-8515 群馬県桐生市天神町 1-5-1 †(株) ルネサス テクノロジ 〒 376-8515 群馬県高崎市西横手町 111

H. San A. Hayakawa Y. Jingu H. Wada H. Hagiwara K. Kobayashi H. Kobayashi T. Matsuura K. Yahagi J. Kudoh H. Nakane

Electronic Engineering Department, Faculty of Engineering, Gunma University Tel: 0277-30-1788 Fax: 0277-30-1707 e-mail:{san,k\_haruo}@el.gunma-u.ac.jp †Advanced Analog Development Dept., Renesas Technology Corp.

概要 - この論文では、Bluetooth, WLAN 等の Low-IF 受信機への適用のためのスイッチドキャパシタ回 路を用いるマルチビット複素バンドパス  $\Delta\Sigma$ AD 変調 器の新しい構成を提案する。複素バンドパス  $\Delta\Sigma$ AD 変調器を実現の際には次の2つの問題が生じる。(i) 内部のI.Qアナログ経路間のミスマッチにより AD変 換器全体の SNR が劣化する。(ii) 複素変調器内部の 複素フィルタ部分及び I,Q 経路の DAC によるフィー ドバックで、I,Q 経路をクロスする信号線が多く、レ イアウト設計が複雑になり、チップ面積が増大する。 この論文では I,Q 経路を完全に分離できる構成を提 案し、上記の問題を解決する。変調器内にマルチプ レクサを設けて信号経路・回路を I,Q 用にサンプリ ング毎に切り替えて使用する。対称となる2つの回 路をあるタイミングではI経路用、Q経路用として 用い、次のタイミングではマルチプレクサで切り替 えて、それぞれ Q 経路用、I 経路用として用いるの で、2つの経路間のミスマッチの影響が軽減される。 この回路構成は結果的に I,Q 回路のクロス部分を分 離するので、従来法に比べ回路のレイアウト設計が 容易になる。Matlab によるシミュレーションで提案 手法の有効性を確認した。

**キーワード**: 複素バンドパス  $\Delta \Sigma$ AD 変調器回路、I,Q 経路間ミスマッチ、マルチプレクサ、ダイナミックマッチング

#### I はじめに

携帯電話や無線 LAN 等の通信システムの RF 受信 回路において、低中間周波数 (Low-IF) 受信機アー キテクチャ[1] は有力な方式の一つであるが、この方 式で2つの「1入力1出力 ΔΣAD 変調器」を使用 すると、信号成分のみならずイメージ成分も AD 変 換を行うため非効率である。一方、複素バンドパス ΔΣAD 変調器は信号成分のみの AD 変換を行うた め、より低消費電力で AD 変換器が実現でき、この アプリケーションに適している [2]-[4]。また  $\Delta \Sigma AD$ 変調器の内部 ADC/DAC をマルチビットで構成すれ ば、内部オペアンプの性能要求が緩和され、低次の ループフィルタで高 SNR が実現でき、さらなる低消 費電力化が可能なため、先に複素バンドパス変調器 用の DWA(Data-Weighted Averaging) アルゴリズ ムを開発した[6,7,8]。これらの背景のもとで、現在 スイッチドキャパシタ回路を用いて、Low-IF 受信機 用マルチビット複素バンドパス ΔΣAD 変調器を開発 しており、それを効率的に実現できる構成を考案し たので報告する。

## II 従来の複素バンドパス $\Delta\Sigma$ AD 変調器の構成

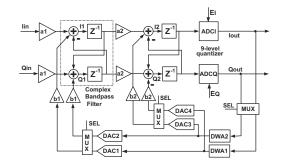

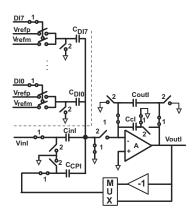

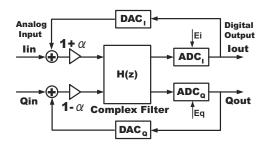

図1に我々が先に検討した従来の2次複素バンドパス  $\Delta\Sigma$ AD変調器の構成を示す[5]。複素変調器は2次複 素フィルタ、2つの3bit ADCと4つの3bit DACに よって構成される。そのマルチビットDACの非線形

図 1: 従来式離散時間 2 次複素バンドパス  $\Delta\Sigma$ AD 変調器  $(a_1 = 1/3, b_1 = -2/3, a_2 = 3/2, b_2 = 2.)$

性の影響を抑えるため、我々が開発した DWA アルゴリズムを適用し、4つの DAC によるフィードバック経路に MUX 回路と DWA 用デジタル回路を加える [6,7,8]。

図 1 に示す複素  $\Delta\Sigma$  変調器の入出力関係式は次のようになる。

$$I_{out} + jQ_{out} = z^{-2} \left[ \frac{1}{2} (I_{in} + jQ_{in}) + (z - j)^2 (E_I + jE_Q) \right].$$

また図1の内部の信号の関係式は次のようになる。

$$I_{1}(n+1) = a_{1} \cdot I_{in}(n+1)$$

$$+ b_{1} \cdot DAC1(n+1) - Q_{1}(n) \qquad (1)$$

$$Q_{1}(n+1) = a_{1} \cdot Q_{in}(n+1)$$

$$+ b_{1} \cdot DAC2(n+1) + I_{1}(n) \qquad (2)$$

$$I_{2}(n+1) = a_{2} \cdot I_{1}(n)$$

$$+ b_{2} \cdot DAC3(n+1) - Q_{2}(n) \qquad (3)$$

$$Q_{2}(n+1) = a_{2} \cdot Q_{2}(n)$$

$$+ b_{2} \cdot DAC4(n+1) + I_{2}(n). \qquad (4)$$

ここで DAC1 と DAC4 は ADCI によるフィードバックで、DAC2 と DAC3 は ADCQ によるフィードバックである。

図1に示す構成のチップ実現に際し2つの問題が 生じた。

(1) **レイアウトの複雑さ:** 図1に示すように、複素 変調器回路では、内部の複素フィルタ部分及び I,Q 経路の 4ch DAC によるフィードバックで、 I,Q 信号のラインはクロスする箇所が多い。その 結果、レイアウト上で配線が長くなり、ドライブ回路で電力消費が増え、またチップ面積も大きくなってしまう。

(2) I,Q 経路ミスマッチ: 図1の回路のチップ実現に際し、前進(フォワード)経路の上段のI経路と下段のQ経路で、製造上のバラツキによりアナログ回路特性のミスマッチが生じる。これによりイメージ帯域の量子化ノイズが信号帯域に回り込み、変調器全体の精度(SNR)を劣化させてしまう(付録1)。このI,Qミスマッチの影響を軽減する方式はいくつか提案されているが[10]-[13]、我々の構成には必ずしも有用ではない(直接適用できない)。なお、フィードバック経路のDAC間のミスマッチに関しては、提案DWAアルゴリズム[6,7,8]により2つのDACをサンプル周期毎に交互にI,Q経路に取り替えて使用するので、その影響はキャンセルされる。

この2つの問題を解決する構成を考案し、その有効性をMatlabによるシミュレーションで確認した。

#### III 提案する複素バンドパス $\Delta\Sigma$ AD 変調器構成

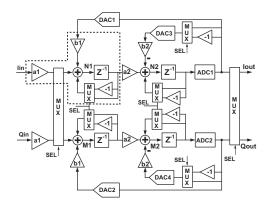

図 2 に提案する複素バンドパス  $\Delta\Sigma$ AD 変調器の構成を示す。まず、理想的な場合、この構成が図 1 と等価な複素バンドパス  $\Delta\Sigma$ AD 変調器であることを示す。 時刻 n=2k-1 の時 (図 3):

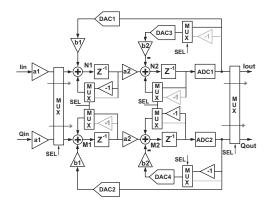

アナログ信号  $I_{in}$  が上半部の回路、 $Q_{in}$  が下半部の回路に入力される。またデジタル出力  $I_{out}$  が上半部の回路 (ADC1) から、 $Q_{out}$  が下半部 (ADC2) から出力される。内部の信号の関係式は以下のようになる。

$$\begin{split} N_1(2k) &= a_1 \cdot I_{in}(2k) \\ &+ b_1 \cdot DAC1(2k) - N_1(2k-1) \quad (5) \\ M_1(2k) &= a_1 \cdot Q_{in}(2k) \\ &+ b_1 \cdot DAC2(2k) + M_1(2k-1) \quad (6) \\ N_2(2k) &= a_2 \cdot N_1(2k-1) \\ &+ b_2 \cdot DAC2(2k) + N_2(2k-1) \quad (7) \\ M_2(2k) &= a_2 \cdot M_1(2k-1) \\ &+ b_2 \cdot DAC4(2k) - M_2(2k-1). \quad (8) \end{split}$$

ここで次のような関係を与える。

$$N_1(2k-1) = Q_1(2k-1), M_1(2k-1) = I_1(2k-1)$$

$N_2(2k-1) = I_2(2k-1), M_2(2k-1) = Q_2(2k-1).$

図 2: 提案する複素バンドパス  $\Delta\Sigma$ AD 変調器の構成.

図 3: 提案する変調器の動作状態 1 (時刻 n = 2k-1).

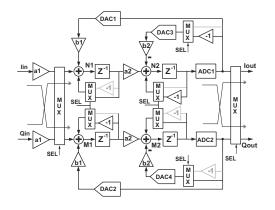

図 4: 提案する変調器の動作状態 2 (時刻 n=2k).

また、DAC1 と DAC3 は ADC1(信号 I) によるフィードバックで、DAC2 と DAC3 は ADC2(信号 Q) によるフィードバックであるので、式 (5) と (1)、式 (6) と (2)、式 (8) と (3)、式 (7) と (4) が一致する。

#### 時刻 n = 2k のとき (図 4):

アナログ信号  $I_{in}$  が下半部、 $Q_{in}$  が上半部の回路 に入力される。デジタル出力  $I_{out}$  が下半部の回路 (ADC2) から、 $Q_{out}$  が上半部 (ADC1) から出力される。内部の信号の関係式は以下のようになる。

$$N1(2k+1) = a_1 \cdot Q_{in}(2k+1)$$

$$+ b_1 \cdot DAC1(2k+1) - N_1(2k) \quad (9)$$

$$M_1(2k+1) = a_1 \cdot I_{in}(2k+1)$$

$$+ b_1 \cdot DAC2(2k+1) + M_1(2k) \quad (10)$$

$$N_2(2k+1) = a_2 \cdot N_1(n)$$

$$+ b_2 \cdot DAC3(2k+1) + N_2(2k) \quad (11)$$

$$M_2(2k+1) = a_2 \cdot M_1(2k)$$

$$+ b_2 \cdot DAC4(2k+1) - M_2(2k) \cdot (12)$$

ここで次のような関係を与える。

$$N_1(2k) = I_1(2k),$$

$M_1(2k) = Q_1(2k)$

$N_2(2k) = Q_2(2k),$   $M_2(2k) = I_2(2k).$

また、DAC1 と DAC3 は ADC1(信号 Q) によるフィードバックで、DAC2 と DAC3 は ADC2(信号 I) によるフィードバックであるので、式 (10) と (1)、式 (9) と (2)、式 (11) と (3)、式 (12) と (4) が一致する。

以上により提案構成が図 1 と等価であることが示された。また、図 2 に示されているように、図 1 での前進経路の  $Z^{-1}$  ブロックのクロス部分、DAC によるフィードバック部分のクロスする経路がなくなり、I,Q パスは完全に分離した構成となっている。したがって変調器のレイアウトの際に配線距離が短くなりチップ面積も小さくなる。

なおこの回路実現の注意点は以下のようになる。

- (i) MUX は MOS スイッチで容易に実現できる。

- (ii) 前進経路の複素フィルタの内部及びフィードバック部のDACでは複素信号処理上での信号の極性を保つため[14]、MUX回路を用いて1周期ごとに1倍と1倍の交互の動作を行う。その実際の回路実現では、差動信号の2つ出力端子を1クロックごとにチョッピングすればよい。

図 5: 提案変調器での複素バンドパス・フィルタの SC 回路実現(図2で点線で囲んだ部分).

## IV I、Q 経路ミスマッチによる SNR 劣化の軽減

図 2 の提案構成では、たとえば  $N_1(n)$  に対して下式 を満たしている。

$$n = 2k - 1$$

の時  $N_1(2k - 1) = Q_1(2k - 1),$

$n = 2k$  の時  $N_1(2k) = I_1(2k).$

また、ADC1 は n=2k-1 の時  $I_{out}$  を出力し、n=2k の時  $Q_{out}$  を出力する。各 DAC もサンプル時刻毎に I 経路用、Q 経路用と切り替わる。このような動作により変調器内の I, Q 経路 (各対応回路間) のミスマッチによる SNR 劣化への影響が軽減される。

このブロックレベルでの構成・動作に加えて、回路レベルでもダイナミック・マッチングによりミスマッチの影響を軽減する。図1での $Z^{-1}$ ブロックを[9]に示されたスイッチド・キャパシタ(SC)回路で実現する方式を用いた複素バンドバス・フィルタの回路構成を図5で示す。ミスマッチがない理想変調器では、図1と図5で次が成立する。

$$\frac{C_{inI}}{C_{outI}} = \frac{C_{inQ}}{C_{outQ}} (= a_1),$$

$$\sum_{n=0}^{7} C_{DIn} \qquad \sum_{n=0}^{7} C_{DQn}$$

$$C_{outI} = \frac{n}{C_{outQ}} (= b_1),$$

$$C_{CPI} = C_{CPQ} = C_{outI} = C_{outQ}.$$

実際は製造上のバラツキで容量の比が上式を満たさないので、それが変調器のI,Q 経路間のミスマッチとなり、変調器全体の精度(SNR)を劣化させてしま

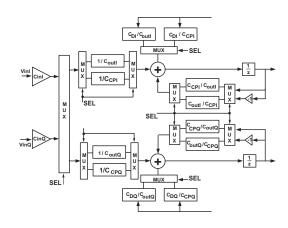

図 6: 変調器の一段目フィルタの容量ミスマッチ影響 軽減のための提案する方式の等価回路.

う。そこで I,Q 経路のミスマッチ (容量のバラツキ) による SNR の劣化を軽減するために、提案した図 2 の構成の一段目のフィルタ回路に対して次のような動作をさせる (図 6)。

- (i)  $C_{inI}$  と  $C_{inQ}$  はそれぞれ I,Q 経路に固定する。 入力信号  $I_{in}$ 、 $Q_{in}$  を各容量  $C_{inI}$ 、 $C_{inQ}$  に入力 した後、入力部 MUX を通して交互的に上下の 経路に伝達する。シミュレーション結果により、  $C_{inI}$  と  $C_{inQ}$  のミスマッチの影響が小さいため である。

- (ii)  $C_{OUTI}$  と  $C_{CPI}$ 、および  $C_{OUTQ}$  と  $C_{CPQ}$  を MUX によりサンプリング毎に交互に入れ替える。 $C_{CPI}$  と  $C_{CPQ}$  及び  $C_{OUTI}$  と  $C_{OUTQ}$  のミスマッチの影響軽減のためである。

このような構成・動作により、さらに経路間ミスマッチの影響が軽減できる。なお、2段目フィルタのI,Q経路ミスマッチの影響は小さいので、上記は1段目フィルタだけに用いる。

## V シミュレーションによる提案方法の効果の確認

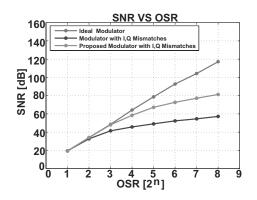

提案手法の有効性を確認するため下記三通りの場合 について MATLAB シミュレーションを行った。

- (1) I,Q経路間のミスマッチがない理想変調器の場合。

- (2) 変調器内部に I,Q 経路間のミスマッチと内部 3 ビット DAC に非線形がある場合。

図 7: 3つのケースの場合の変調器の SNR の比較 (表 1 のパラメータ値使用).

図 8: 理想 DAC の場合の 3 つのケースの変調器の SNR の比較 (表 2 のパラメータ値使用).

表 1: I, Q 経路容量ミスマッチのパラメータ 1

| 1. 1, 6, 在路台至入八十万万0万1万万 |              |             |

|-------------------------|--------------|-------------|

|                         | I            | Q           |

| $C_{in}$                | (1-0.023)*1  | (1-0.023)*1 |

| $C_{out}$               | (1+0.014)*3  | (1-0.028)*3 |

| $C_{CP}$                | (1-0.035)*3  | (1+0.028)*3 |

| $C_{D0}$                | (1-0.0004)*2 | (1-0.018)*2 |

| $C_{D1}$                | (1-0.0014)*2 | (1+0.014)*2 |

| $C_{D2}$                | (1+0.0018)*2 | (1+0.008)*2 |

| $C_{D3}$                | (1-0.0006)*2 | (1+0.014)*2 |

| $C_{D4}$                | (1+0.0012)*2 | (1+0.012)*2 |

| $C_{D5}$                | (1+0.0012)*2 | (1-0.006)*2 |

| $C_{D6}$                | (1-0.018)*2  | (1-0.024)*2 |

| $C_{D7}$                | (1-0.000)*2  | (1+0.000)*2 |

(3) 変調器内部のミスマッチは (2) と同じ条件であるが、提案した回路構成を用いる場合。

図7に各場合のSNRの比較結果を示す。理想的な変調器回路では、SNRはOSRの増加に伴い増加する。I,Q経路間にミスマッチがある場合(表1)、従来式回路では、OSRを増加してもSNRが飽和してしまう。一方、提案回路方式ではSNRが大きくなり、I,Q間ミスマッチの影響が軽減されていることが分かる。

また、DAC は理想的で変調器内複素フィルタの I,Q 経路間ミスマッチだけがある場合 (表 2) の結果を図 8 に示す。

表 2: I, Q 経路容量ミスマッチのパラメータ 2

|           | I           | Q          |

|-----------|-------------|------------|

| $C_{in}$  | (1-0.03)*1  | (1+0.03)*1 |

| $C_{out}$ | (1+0.014)*3 | (1-0.03)*3 |

| $C_{CP}$  | (1-0.03)*3  | (1+0.02)*3 |

#### VI まとめ

携帯電話、無線 LAN、Bluetooth 用の低 IF 受信機への応用のための離散時間複素バンドパス  $\Delta\Sigma$ AD 変調器の新しい回路構成を提案した。従来方式に対し、アナログ MUX 回路を追加することで、複素バンドパスフィルタ内の I,Q 経路間のミスマッチによる SNRの劣化を軽減できる。複素変調器の I,Q 経路間を完全に分離し、回路構成・レイアウト設計が容易になる。提案した回路構成を用いて高性能の複素バンドパス  $\Delta\Sigma$ AD 変調器を実現していく。

謝辞 有意義なご討論をいただきました堀田正生氏、 塚田敏郎氏、益子耕一郎氏、和田淳氏、小澤時典氏、 今泉栄亀氏、杉原仁氏、櫻澤出氏および本研究を支 援していただいています (株) 半導体理工学研究セン ター (STARC) に感謝いたします。

#### 参考文献

J. Crols, M. Steyeart, "Low-IF Topologies for High-Performance Analog Front Ends of Fully Integrated Receivers," *IEEE Trans. on Circuits & Systems II*, vol.45, no.3, pp.269-282 (March 1998).

- [2] F. Munoz, K. Philips, A. Torralba, "A 4.7mW 89.5dB DR CT Complex  $\Delta\Sigma$  ADC with Built-in LPF", ISSCC Digest of Technical Papers, vol.47, pp.500-501 (Feb. 2004).

- [3] N. Yaghini, D. Johns, "A 43mW CT Complex ΔΣ ADC with 23MHz of Signal Bandwidth and 68.8 SNDR," ISSCC Digest of Technical Papers, vol.47, pp.502-503 (Feb. 2004).

- [4] S. A. Jantzi, K. W. Martin, A. S. Sedra, "Quadrature bandpass ΣΔ modulator for digital radio," *IEEE Journal of Solid-State Circuits*, vol.32, pp.1935-1949 (Dec. 1997).

- [5] 早川晃、傘昊、小林春夫、神宮善敬、小林和幸、"離散時間マルチビット複素バンドパス ΣΔAD 変調器の設計"、電子情報通信学会 集積回路研究会、大阪(2004年7月).

- [6] H. San, H. Kobayashi, S. Kawakami, N. Kuroiwa, H. Wada, "An Element Rotation Algorithm for Multi-bit DAC Nonlinearities in Complex Bandpass Delta-sigma AD Modulators", IEEE 17th International Conference on VLSI Design, pp.151-156, Mumbai, India, (Jan. 2004).

- [7] H. San, H. Kobayashi, S. Kawakami, N. Kuroiwa, "A Noise-shaping Algorithm of Multi-bit DAC Nonlinearities in Complex Bandpass ΔΣAD Modulators," *IEICE Trans. on Fundamentals*, vol.E87-A, no.4, pp.792-800 (April 2004).

- [8] 和田宏樹、小林春夫、傘昊、「マルチビット複素バンドパス ΔΣAD 変調器 1 次 DWA アルゴリズムの実現回路の検討」電気学会 電子回路研究会、pp.1-6, 函館 (2004 年 6 月).

- [9] L. Longo, B. Horng, "A 15b 30kHz Bandpass Sigma-Delta Modulator," ISSCC Digest of Technical Papers, pp.226 - 227 (Feb. 1993).

- [10] R. Schreier, "Quadrature Mismatch-shaping", Proc. of ISCAS, vol.4, pp.675 - 678 (May 2002).

- [11] J. Riches, N. Erdol, "Mismatch Cancellation in Quadrature Bandpass ΔΣ Modulators Using an Error Shaping Technique", *IEEE Trans. on Circuits* and Systems II, vol.49, pp.73-85 (Feb. 2002).

- [12] L.Breems, E.Dijkmans, H. Huijsing, "A Quadrature Data-dependent DEM Algorithm to Improve Image Rejection of a Complex ΔΣ Modulator", IEEE Journal of Solid-State Circuits, vol.36, pp.1879 -1886 (Dec. 2001).

- [13] R. Maurino, C. Papavassiliou, "Multibit Quadrature Sigma-Delta Modulator with DEM Scheme", Proc. of ISCAS, vol.1, pp.I1136-1139 (May 2004).

- [14] K. W. Martin, "Complex Signal Processing is Not Complex," *IEEE Trans. on Circuits & Systems I*, vol.51, pp.1823-1836 (Sep. 2004).

図 9: I, Q経路ミスマッチ (α) がある複素 AD 変調器.

# 付録 1: 複素 $\Delta\Sigma$ AD 変調器での I, Q ミスマッチ による精度劣化

複素信号処理の考え方 [14] を用いて I, Q 経路ミスマッチのより SNR 劣化する理由を考察する。図 9 でミスマッチがない場合  $(\alpha=0)$  は次の関係式が得られる。

$$\begin{split} I_{out} + jQ_{out} &= \\ \frac{H}{1+H}(I_{in} + jQ_{in}) + \frac{1}{1+H}(E_i + jE_q). \end{split} \label{eq:lout}$$

ミスマッチがある場合  $(\alpha \neq 0)$  は次のようになる。

$$\begin{split} I_{out} + jQ_{out} &= \\ &\frac{H + (1 - \alpha^2)H^2}{1 + 2H + (1 - \alpha^2)H^2} (I_{in} + jQ_{in}) \\ &+ \frac{\alpha H}{1 + 2H + (1 - \alpha^2)H^2} (I_{in} - jQ_{in}) \\ &+ \frac{1 + H}{1 + 2H + (1 - \alpha^2)H^2} (E_i + jE_q) \\ &+ \frac{\alpha H}{1 + 2H + (1 - \alpha^2)H^2} (E_i - jE_q). \end{split}$$

このときイメージ帯域の量子化ノイズ  $(E_i - jE_q)$  が 信号帯域内に回り込んで SNR を劣化させてしまうことがわかる。上式からその伝達関数は

$$\frac{\alpha H}{1 + 2H + (1 - \alpha^2)H^2}$$

である。