#### 第339回 アナログ集積回路研究会講演

# 2017年版 第4回 半導体技術の概要と動向

- 1)概要

- 2)高集積化技術動向 MPU、DRAM、NANDの高集積化推移

- 3)微細化技術動向 ITRSロードマップ、ITRSにおける寸法定義 スケーリング則 微細化に伴う高性能化技術

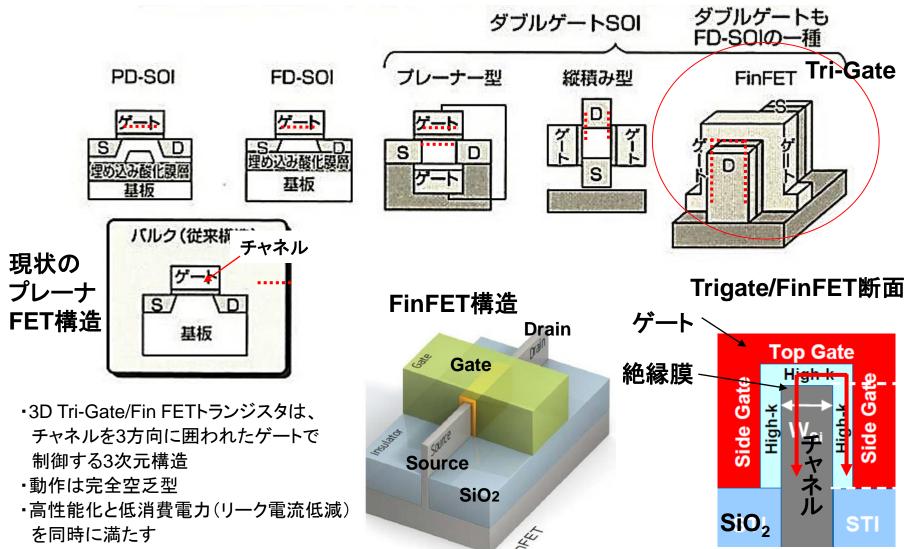

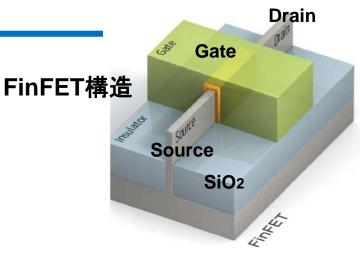

- 3D FinFET技術

- 4) NANDのチップ内3D技術

- 5)パッケージ内3次元実装技術 パッケージ内3次元実装技術概要 チップ積層ワイヤボンディング実装、PoP実装.TSVなど

2017.10.24 群馬大学非常勤講師 東京電機大学非常勤講師 中谷 降之

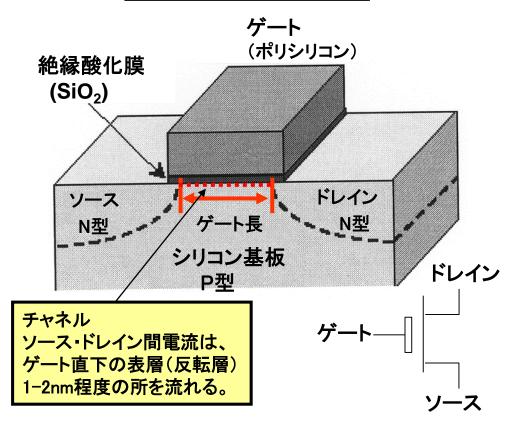

## MOSトランジスタ(FET)の構造

MOSトランジスタの基本構造はバイポーラトランジスタに比べてシンプル。P型MOSとN型MOSがある。N型MOSトランジスタの場合

- ・P型基板に、N型のソース領域(ウェル)とドレイン領域(ウェル)および薄い酸化膜上にゲート電極を形成

- ・ゲート印加電圧ないときは、ソースとドレイン間に空乏層が形成されソースとドレイン間は導通せず

- ・ゲートにプラス電圧印加すると、ゲート電極下に反転層(N層)が現れ、ソースとドレイン間にチャネル形成され導通

#### N型MOS トランジスタ

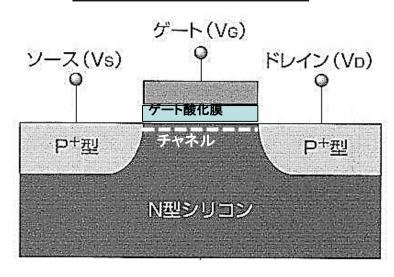

#### P型MOSトランジスタ

不純物の例

N:リン(P)

P:ボロン(B) など

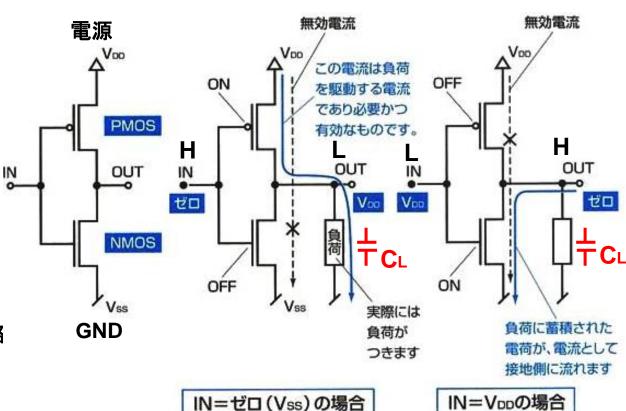

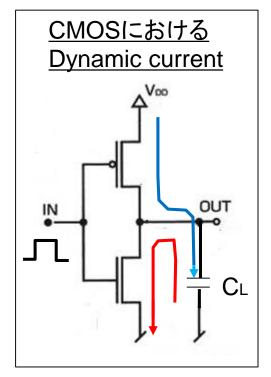

### CMOS回路

CMOSとは P型MOSトランジスタと N型MOSトランジスタから構成

入力Lo(ゼロレベル) だと P型MOSがOn N型MOSがOff すなわち 出力がH(VDD電源レベル)

入力がH (VDD) だと P型MOSがOff N型MOSがOn すなわち 出力がL(ゼロ)

入力と出力の論理が反転 (インバータ)するデジタル回路 MOS: Metal Oxide Semiconductor CMOS: Complementary (相補型)MOS

#### CMOSインバータ

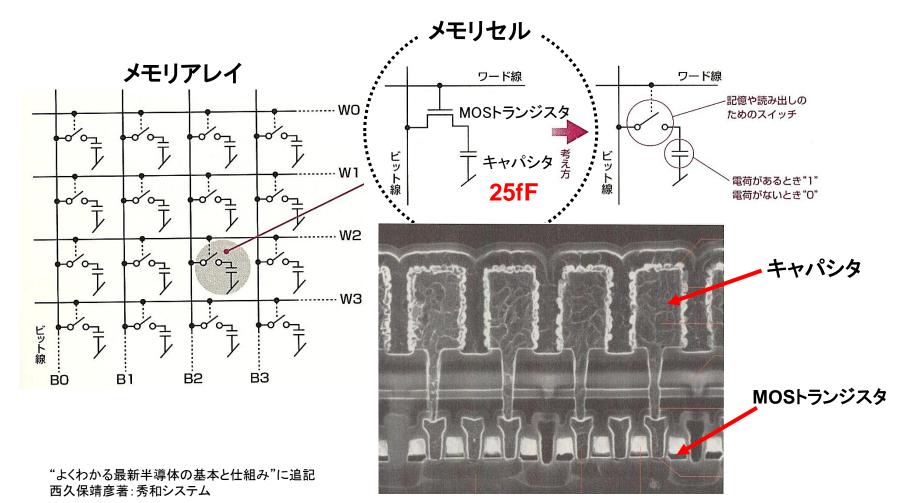

- ・DRAMのメモリセルは、MOSトランジスタ1個とキャパシタ1個から構成される揮発性メモリ

- ・キャパシタに電荷が蓄積された状態を"1"、ない状態を"O"として記憶

- ・MOSトランジスタはキャパシタ電荷の記憶や読み出しのスイッチとして働く。

- ・例えば、4GビットのDRAMでは、40億個のメモリセルが1チップ上に作られている。

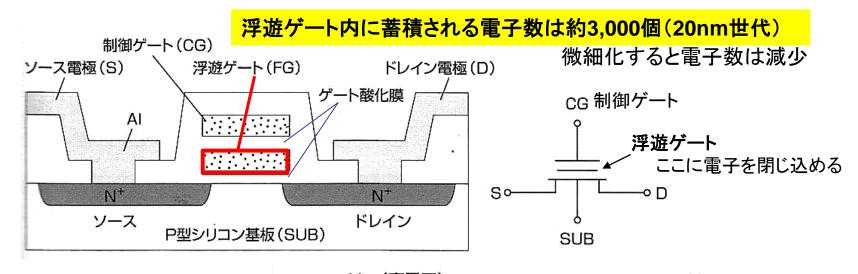

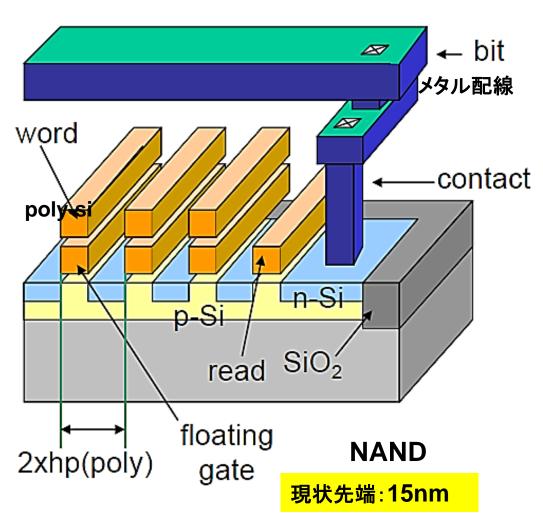

### フラッシュメモリ

- ・フラッシュメモリは、酸化絶縁膜(SiOゥ)に囲まれた浮遊(フローティング)ゲート電極内 電子蓄積でデータを蓄え、電源を切ってもデータは消えない不揮発メモリ。

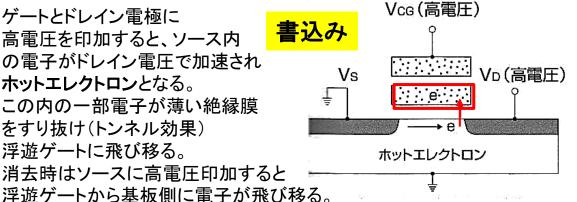

- ·ゲート電極に高電圧をかけ 浮遊ゲートへの電子の"トンネル効果"を用いて書込む

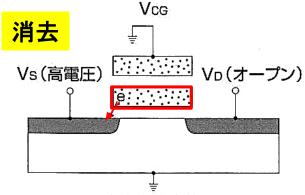

ゲートとドレイン電極に 高電圧を印加すると、ソース内 の電子がドレイン電圧で加速され ホットエレクトロンとなる。 この内の一部電子が薄い絶縁膜 をすり抜け(トンネル効果) 浮游ゲートに飛び移る。 消去時はソースに高電圧印加すると

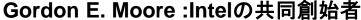

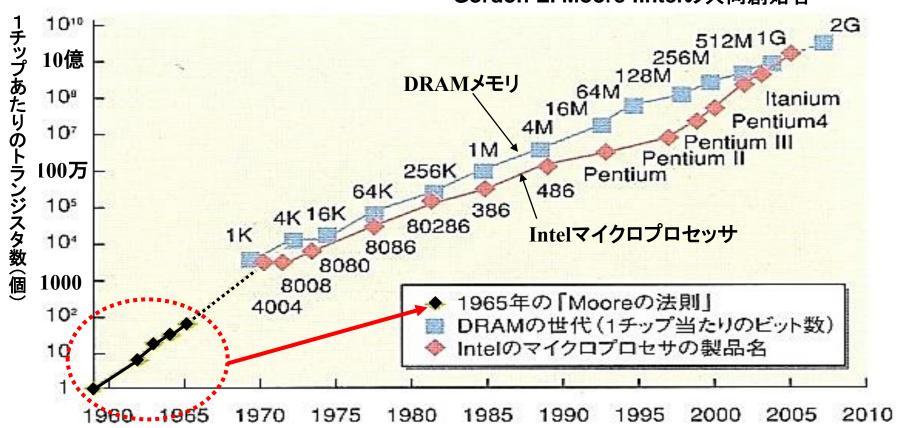

## 半導体(LSI)の高集積化推移

ムーアの法則: 1965年に集積度は18~24ヶ月(1世代)で2倍増加すると提唱。

1965年以降、現在にいたるまで半導体はムーアの法則により高集積化している。 現在、1チップLSI中に数十億個のトランジスタが集積されている。

日経エレクトロニクス

### マイクロプロセッサに集積されるトランジスタ数

- 1971年世界初のマイクロプロセッサは、約2,300個のトランジスタが集積されていた。

- 2017年発売のiPhone8用A11プロセッサでは約 43億個のトランジスタを集積(10nmFinFETプロセス)

- -2017年発売のゲーム器(xBoxone x)プロセッサでは約70億個のトランジスタを集積(16nmFinFETプロセス)

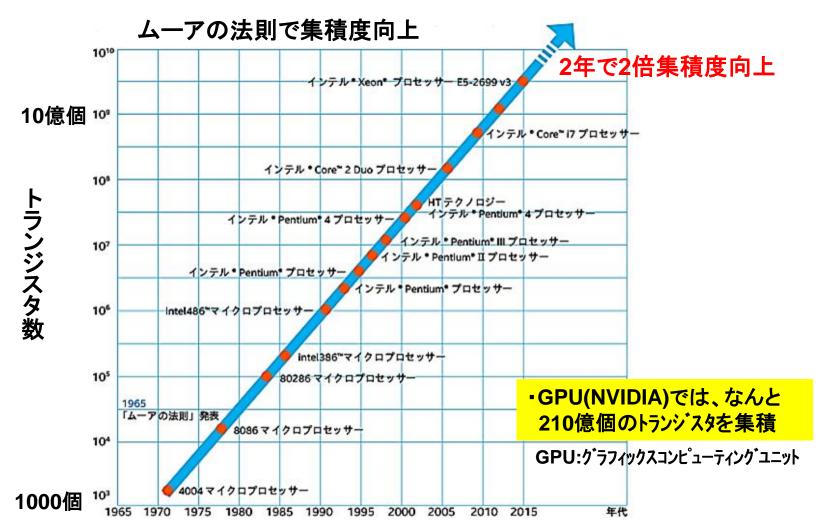

### DRAMの大容量化

- ・DRAMは約2年半で世代交代し、容量が2倍へ高集積化

- •2016年、4Gbitから8Gbit世代に移行

- ・DRAMの微細化による大容量化はほぼ限界。16Gbitは難しい

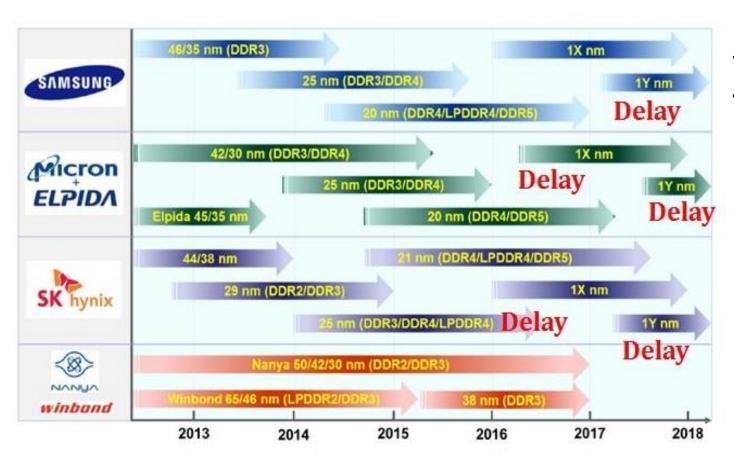

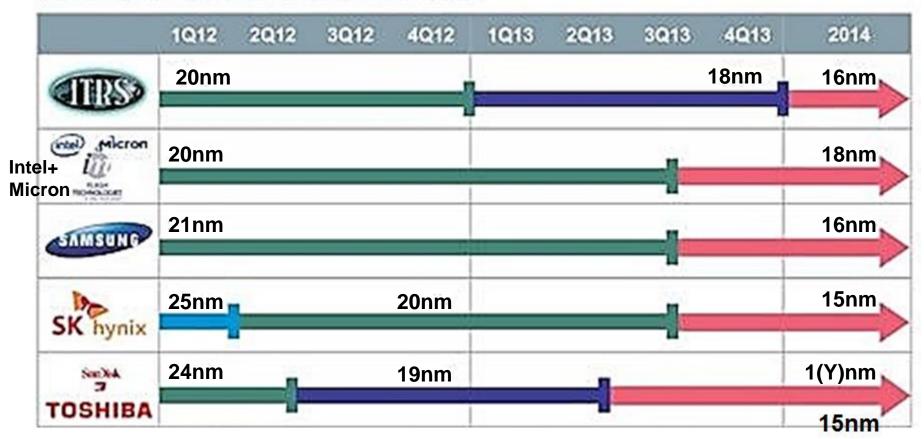

## DRAM各社のプロセスロードマップ

DRAMの製造プロセスの微細化は16nm世代で限界に直面。結果大容量化も行きづまり DRAM微細化ではSamsungが先行

### ■ DRAM Process Node Roadmap (Manufacturers)

1X:約18nm

1Y:約15nm

年

2010

2011

2012

2013

2014

2015

2016

2017

2017/6

2017/6

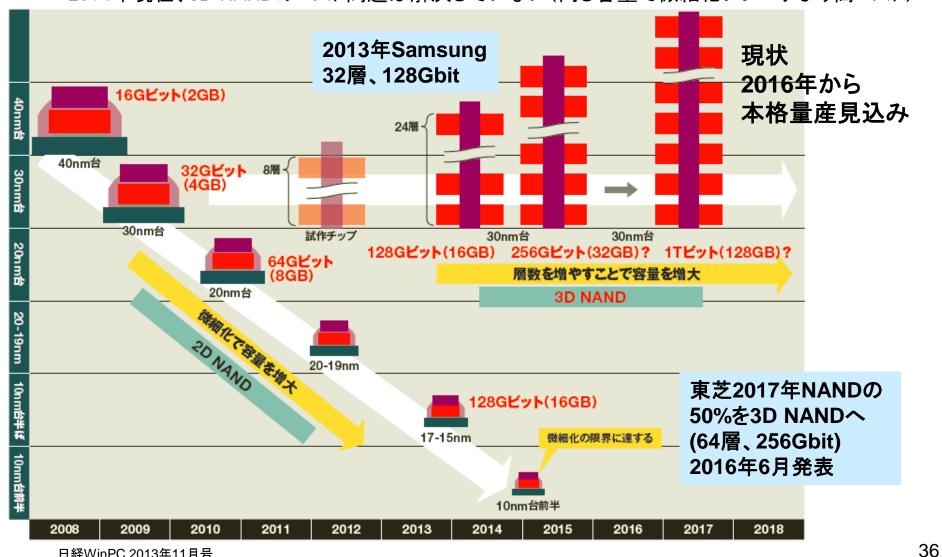

### NANDの大容量化

- ・プレーナ型による微細化は2016年、128Gbit(MLC)14nmプロセスで行き止まり

- チップ内3次元3D NANDは32層128Gb(TLC)から始まり、毎年2倍容量アップ

プロセス

32nmプレーナ

24nmプレーナ

19nmプレーナ

20nmプレーナ

16nmプレーナ

32層3D NAND

48層3D NAND

64層3D NAND

64層3D NAND

96層3D NAND

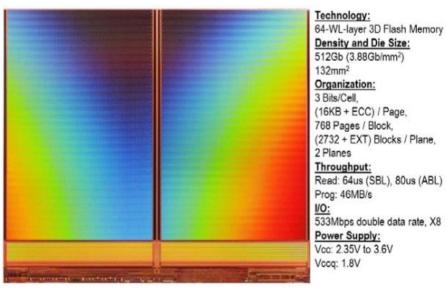

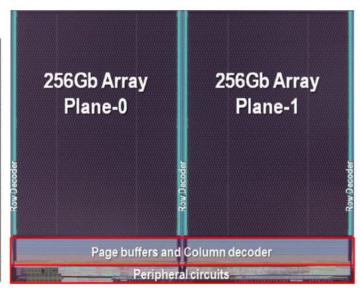

- 2017年ISSCCでは64層512Gbit発表。2017年6月からサンプル出荷

- •2017年6月にはQLC(4bit/cell)として768Gbit/chip発表

- •768Gbit/chipを薄くして16枚パッケージ内積層し

ISSCCに見るNAND大容量化推移

多値レベル

MLC

MLC

MLC

TLC

MLC

TLC

TLC

TLC

QLC

TLC

1.5TByte(12.3Tbit)/パッケージ

容量

32Gb

64Gb

64Gb

128Gb

128Gb

128Gb

256Gb

512Gb

768Gb

256Gb

| 5120<br>1321<br>3.88G                             | AND RESIDENCE OF THE PARTY OF T |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cell Array<br>256Gb<br>Plane-0<br>Row<br>Decoders | Cell Array<br>256Gb<br>Plane-1<br>Row<br>Decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bitline Control (16KB) Periphera                  | Bitline Control (16KB) Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 768GbはVLSIシンポジウム、96層はプレスリリース(東芝)

# 64層512Gb3D NANDチップ(東芝)

ISSCC2017

多値化

SLC:1bit/cell

MLC:2bit/cell

TLC:3bit/cell

QLC:4bit/cell

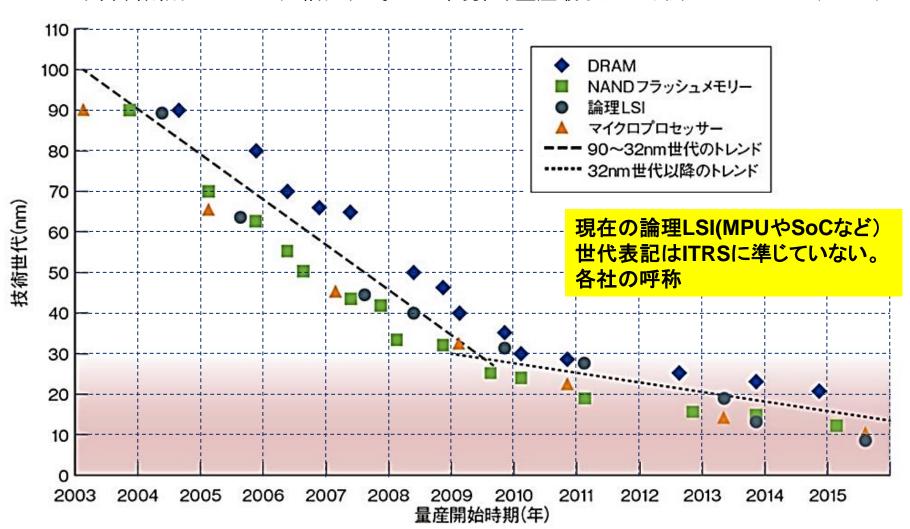

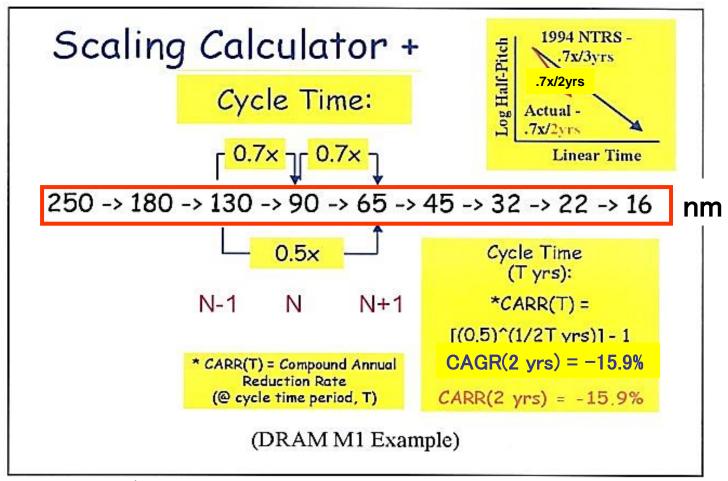

### 半導体の微細化トレンド

- ・微細化は2003~2009年頃までは、約3年毎にx0.7倍で微細化が進んできた すなわち同じチップ面積とすると、約3年で集積度が2倍向上

- ・32nm以降、微細化ペースが大幅ダウン。2016年現在、量産最小加工寸法は15nmレベル(NAND)

### 微細化ロードマップ:国際半導体技術ロードマップ(ITRS)

- ・ITRSは、ムーアの法則を継続し微細化を継続するために何が必要か、グローバル規模で議論され、重要な技術的課題を抽出し、それぞれの課題ごとに15年先まで見据えた定量的な表を多数作製し、毎年その表の更新を重ねてきた。2016年2月でITRSが終焉。原因あれこれ

- ・継続的微細化の行きづまり。15年先のロードマップ意味なくなった

- ・ロードマップ可能なのは連続性のある技術範囲。これまでも非連続な技術は予測と大きくずれた

- ・半導体企業の淘汰(ファブライト、ファウンドリ化)。先端設備可能なのは数社

#### **ITRS2013 Edition**

- 1. Executive Summary

- 2. System Drivers

- Design

- 4. Test & Test Equipment

- 5. Process Integration, Devices & Structures

- 6. RF and A/MS Technologies

- 7. Emerging Research Devices

- 8. Emerging Research Materials

- 9. Front End Processes

- 10. Lithography

- 11. Interconnect

- 12. Factory Integration

- 13. Assembly & Packaging

- 14. Environment, Safety & Health

- 15. Yield Enhancement

- 16. Metrology

- 17. Modeling & Simulation

- **18. MEMS**

#### 化

#### ITRS2.0 2015 Edition

終焉 2016年 2月

- 1.System Integration

- 2.Heterogeneous Integration

- 3. Heterogeneous Components

- 4. Outside System Connectivity

- 5. More Moore

- 6.Beyond CMOS

- 7. Factory Integration

#### ポストITRS

半導体の微細化だけではなく、幅広い技術進歩へのアプローチを検討し、IoTに代表される新しいエレクトロニクス市場にマッチしたロードマップを提供。現在、様々な動きがある。

### **Memory Trends:ITRS2.0 2015 Edition**

| DRAM TECHNOLOGY                                     | DRAM現状HP=20nmプロセス。以後の微細化は難しい |          |         |         |         |         |         |

|-----------------------------------------------------|------------------------------|----------|---------|---------|---------|---------|---------|

| YEAR OF PRODUCTION                                  | 2015                         | 2017     | 2019    | 2021    | 2024    | 2027    | 2030    |

| Half Pitch (Calculated Half pitch) (nm)             | 24                           | 20       | 17      | 14      | 11      | 8.4     | 7.7     |

| DRAM cell size (µm²)                                | 0.00346                      | 0.00240  | 0.00116 | 0.00078 | 0.00048 | 0.00028 | 0.00024 |

| DRAM cell FET structure                             | RCAT+Fin                     | RCAT+Fin | VCT     | VCT     | VCT     | VCT     | VCT     |

| Cell Size Factor: a                                 | 6                            | 6        | 4       | 4       | 4       | 4       | 4       |

| Array Area Efficiency                               | 0.55                         | 0.55     | 0.5     | 0.5     | 0.5     | 0.5     | 0.5     |

| V <sub>int</sub> (support FET voltage) [V]          | 1.1                          | 1.1      | 1.1     | 1.1     | 0.95    | 0.95    | 0.95    |

| Support min. $V_m$ (25C, $G_{m,max}$ , $V_d$ =55mV) | 0.40                         | 0.40     | 0.40    | 0.40    | 0.37    | 0.37    | 0.37    |

| Minimum DRAM retention time (ms)                    | 64                           | 64       | 64      | 64      | 64      | 64      | 64      |

| DRAM soft error rate (fits)                         | 1000                         | 1000     | 1000    | 1000    | 1000    | 1000    | 1000    |

| Gb/1chip target                                     | 8G                           | 8G       | 16G     | 16G     | 32G     | 32G     | 32G     |

#### プレーナ型NANDはHP=14nmプロセスまで以後は3D NAND

| NAND Flash                                        | プレープ 至17111213111 = 1 平11111プロセスなで次次は300 1771110 |          |          |          |          |          |          |

|---------------------------------------------------|--------------------------------------------------|----------|----------|----------|----------|----------|----------|

| Year of Production                                | 2015                                             | 2016     | 2020     | 2022     | 2024     | 2028     | 2030     |

| 2D NAND Flash uncontacted poly 1/2 pitch - F (nm) | 15                                               | 14       | 12       | 12       | 12       | 12       | 12       |

| 3D NAND minimum array 1/2 pitch -F (nm)           | 80nm                                             | 80nm     | 80nm     | 80nm     | 80nm     | 80nm     | 80nm     |

| Number of word lines in one 3D NAND string        | 32                                               | 32-48    | 64-96    | 96-128   | 128-192  | 256-384  | 384-512  |

| Dominant Cell type (FG, CT, 3D, etc.)             | FG/CT/3D                                         | FG/CT/3D | FG/CT/3D | FG/CT/3D | FG/CT/3D | FG/CT/3D | FG/CT/3D |

| Product highest density (2D or 3D)                | 256G                                             | 384G     | 768G     | 1T       | 1.5T     | 3T       | 4T       |

| 3D NAND number of memory layers                   | 32                                               | 32-48    | 64-96    | 96-128   | 128-192  | 256-384  | 384-512  |

| Maximum number of bits per cell for 2D NAND       | 3                                                | 3        | 3        | 3        | 3        | 3        | 3        |

| Maximum number of bits per cell for 3D NAND       | 3                                                | 3        | 3        | 3        | 3        | 3        | 3        |

### **Logic Trends:ITRS2.0 2015 Edition**

・2016年現在、Logicの最先端は14/16nm FinFETプロセス。ITRS定義ではHP(ハーフピッチ)=28nm 2017年、10nmFinFETプロセス。ITRS定義によるHP=18nm

| YEAR OF PRODUCTION                                             | 2015            | 2017            | 2019           | 2021                   | 2024         | 2027         | 2030         |

|----------------------------------------------------------------|-----------------|-----------------|----------------|------------------------|--------------|--------------|--------------|

| Logic device technology naming                                 | P70M56          | P48M36          | P42M24         | P32M20                 | P24M12G1     | P24M12G2     | P24M12G3     |

| 半導体メーカの呼<br>Logic industry "Node Range"<br>Labeling (nm)       | <mark>称</mark>  | "11/10"         | "8/7"          | "6/5"                  | "4/3"        | "3/2.5"      | "2/1.5"      |

| Logic device structure options                                 | FinFET<br>FDSOI | FinFET<br>FDSOI | FinFET<br>LGAA | FinFET<br>LGAA<br>VGAA | VGAA,<br>M3D | VGAA,<br>M3D | VGAA,<br>M3D |

| LOGIC DEVICE GROUND RULES ITRS正式定義                             |                 |                 |                |                        |              |              |              |

| MPU/SoC Metaix ½ Piicn (nm)[1,2]                               | 28.0            | 18.0            | 12.0           | 10.0                   | 6.0          | 6.0          | 6.0          |

| MPU/SoC Metal0/1 ½ Pitch (nm)                                  | 28.0            | 18.0            | 12.0           | 10.0                   | 6.0          | 6.0          | 6.0          |

| Contacted poly half pitch (nm)                                 | 35.0            | 24.0            | 21.0           | 16.0                   | 12.0         | 12.0         | 12.0         |

| L <sub>g</sub> : Physical Gate Length for HP<br>Logic (nm) [3] | 24              | 18              | 14             | 10                     | 10           | 10           | 10           |

| L <sub>g</sub> : Physical Gate Length for LP<br>Logic (nm)     | 26              | 20              | 16             | 12                     | 12           | 12           | 12           |

| FinFET Fin Half-pitch (new) =0.75<br>or 1.0 M0/M1 (nm)         | 21.0            | 18.0            | 12.0           |                        |              |              |              |

| FinFET Fin Width (nm)                                          | 8.0             | 6.0             | 6.0            |                        |              |              |              |

| FinFET Fin Height (nm)                                         | 42.0            | 42.0            | 42.0           |                        | END OF       | 2D           | DOMAIN       |

| Footprint drive efficiency - FinFET                            | 2.19            | 2.50            | 3.75           |                        |              |              |              |

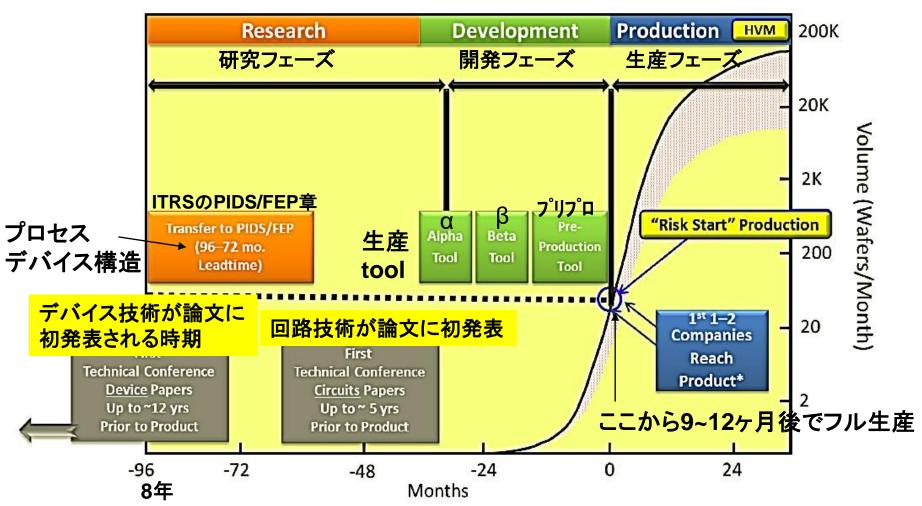

### ITRS定義: Research, Development, Production

- •Production(生産フェーズ)は、先行する1~2社が2万枚/月のウェハ生産(リスク生産)に至る時

- ・回路に関する新技術は、初論文から製品になるのに~5年かかる

- ・デバイスに関わる新技術は、初論文から製品化に至るのに~12年かかる

- ・近年、一社が2万枚/月に達してから2社目が2万枚/月に達するのに4年もかかる例あり(Intel先行)

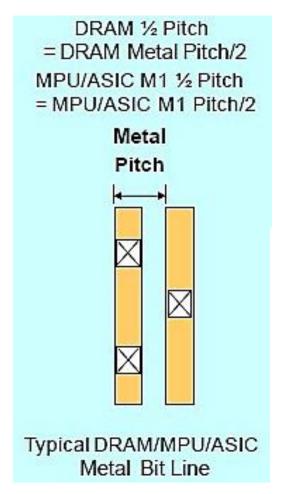

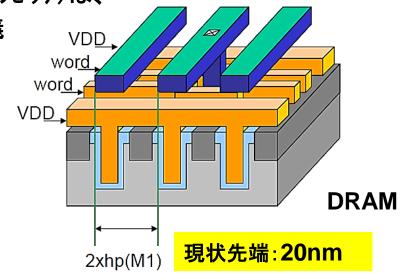

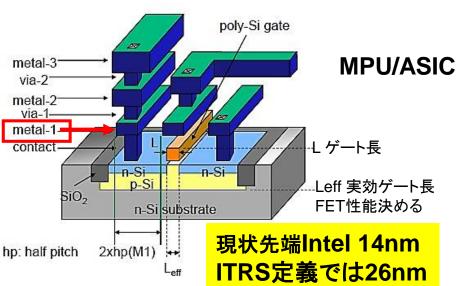

### ITRSによるDRAMとMPU/ASICの寸法定義

DRAMおよびMPU/ASICでの1/2Pitch(hp:ハーフピッチ)は、 最下層メタル配線(M1)配線ピッチの1/2で定義

bit

bit

bit メタル配線

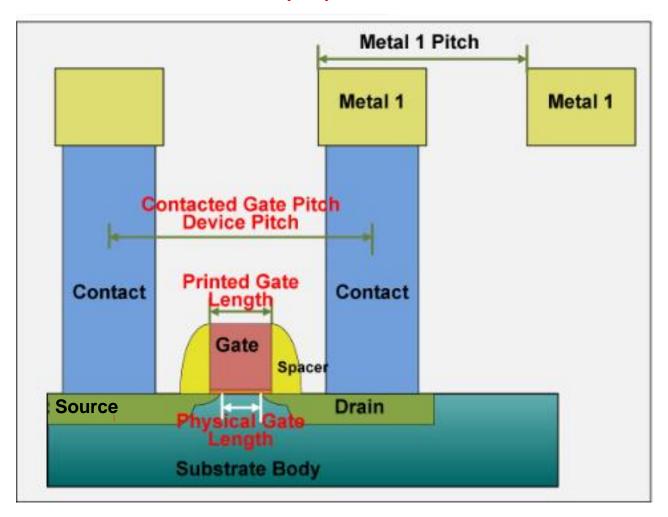

### トランジスタの寸法定義詳細

- ・半導体プロセスでは、配線層のことをメタルと呼ぶ。

- ・配線は、最も下のトランジスタに近い配線が「M1(Metal 1)」で、現在では「M10(Metal 10)」以上

- ・配線は、最下層のM1が最も配線幅やピッチが狭く、上層になるほど配線幅やピッチは広くなる

- -ITRSでは最下層のM1ピッチの1/2(HP)で寸法を定義

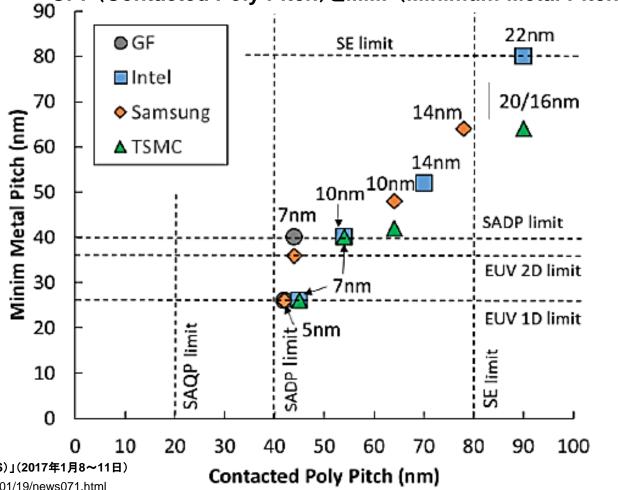

### ロジックプロセス各社呼称とITRS定義の関係

- •Intelの10nm呼称は、ITRS定義の20nm相当

- ・Intelの10nm呼称は、他社(Samsung,TSMC,GF)の7nm相当

- •Intelの7nm呼称は他社の5nm相当

GLOBALFOUNDIES(GF)、Intel、Samsung、TSMC各社のCPP(Contacted Poly Pitch)とMMP(Minimum Metal Pitch)

「Industry Strategy Symposium(ISS)」(2017年1月8~11日)

http://eetimes.jp/ee/articles/1701/19/news071.html

### ITRSによるNANDの寸法定義

NANDフラッシュでの1/2Pitch(hp:ハーフピッチ)は、ポリシリコン(フローティングゲート)ピッチの1/2で定義

### 微細化:スケーリング

- ・半導体の微細化は、最小加工寸法が1世代(約2年)でx0.7倍づつ縮小(スケーリング)

- •ITRS定義による微細化はNANDが最も進んでいる

- ・近年、ロジック(MPUやSOC)LSIで使用される22nm,16nm,14nm表記は、ITRS定義ではなく 実効ゲート長。(3D FinFETではプレーナ相当ゲート長) M1ハーフピッチ

20

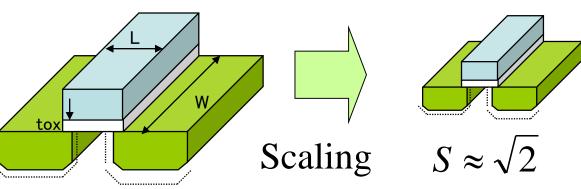

## トランジスタの微細化:デナードのスケーリング則

#### R. Dennard のスケーリング理論(1974年)

- ·スケーリングファクタをS

- ・各ディメンジョンを1/Sに縮小

- 動作電圧を1/Sとして、チャネル電界を一定とする理論。

#### 微細化で顕在化しつつある問題

- 短チャネル効果による リーク電流増大の顕在化

- ・スケーリングによりゲート遅延は 短縮されるが、配線遅延増大が顕在化

#### 短チャネル効果:

ゲート長(L)が短くなり、ドレイン電界の影響が 大きくなり、漏れ電流が増大する効果。

微細化が進み、スケーリングパラメータが、 右表から乖離してきた。 例えば電源が1/Sで下がらないなど。

#### スケーリング則はLSIの黄金則である

動作電圧も1/Sにする

#### トランジスタのスケーリングパラメータ

| Device/Circuit parameter    | Scaling Factor                      |

|-----------------------------|-------------------------------------|

| Device dimensions L, W, Tox | 1/S                                 |

| Doping concentration        | S~S <sup>1.5</sup>                  |

| Voltage                     | 1/S                                 |

| Field                       | 1                                   |

| Current                     | 1/S                                 |

| Gate Delay                  | 1/S                                 |

| Power dissipation/device    | 1/S <sup>3</sup> ~ 1/S <sup>2</sup> |

東工大松澤先生講義テキストから 21

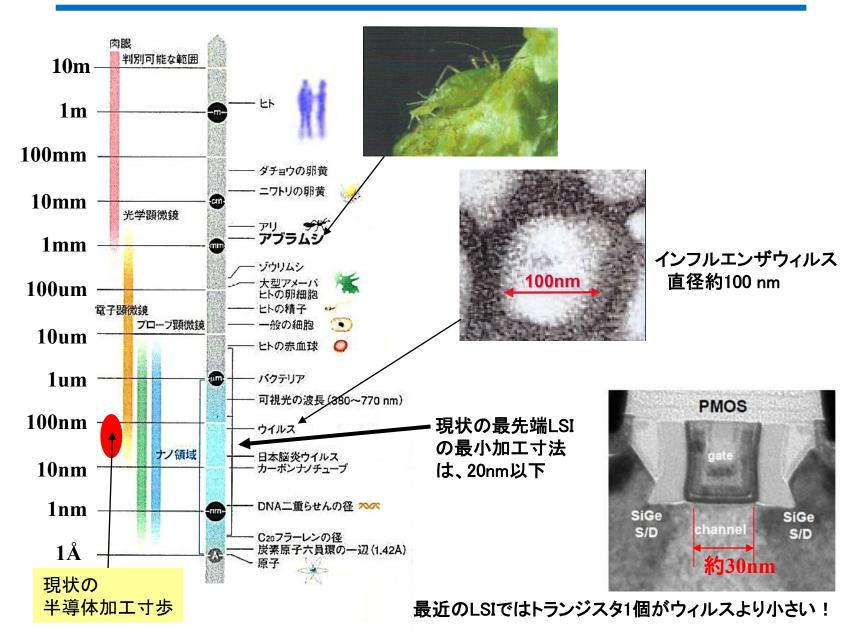

### 様々な物質のサイズと半導体の微細化:

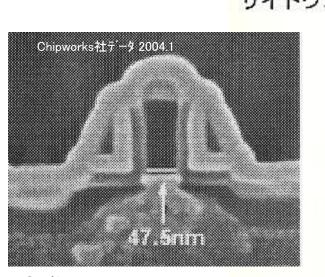

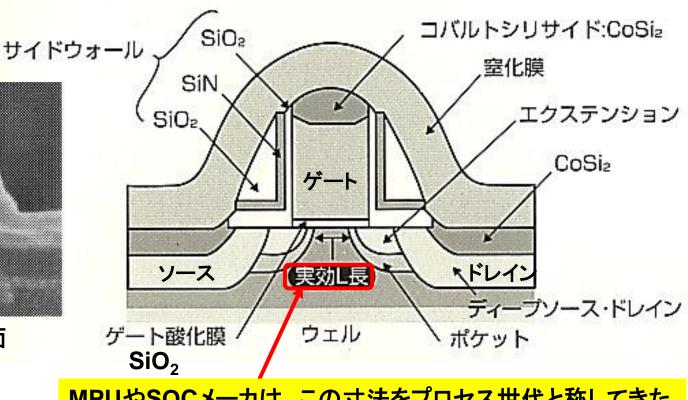

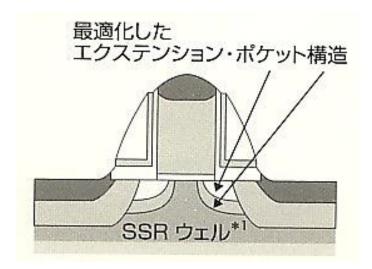

### MOS FETは微細化に伴い構造は複雑化

- ・130nm以降の微細化では、様々な性能劣化対策のためMOS FET構造が複雑化

- ・実効ゲート長(実効L長)によりトランジスタ性能(動作速度)が決まる。 このためプロセス技術で実際のゲート長よりも短くする技術(エクステンション、ポケット構造など)

- ・微細化するとソース、ドレイン、ゲートが高抵抗化対策のためシリサイドCoSiO<sub>2</sub>技術など

実際のMOS FET断面 90nmプロセスで 実効ゲー長は47.5nm

MPUやSOCメーカは、この寸法をプロセス世代と称してきた

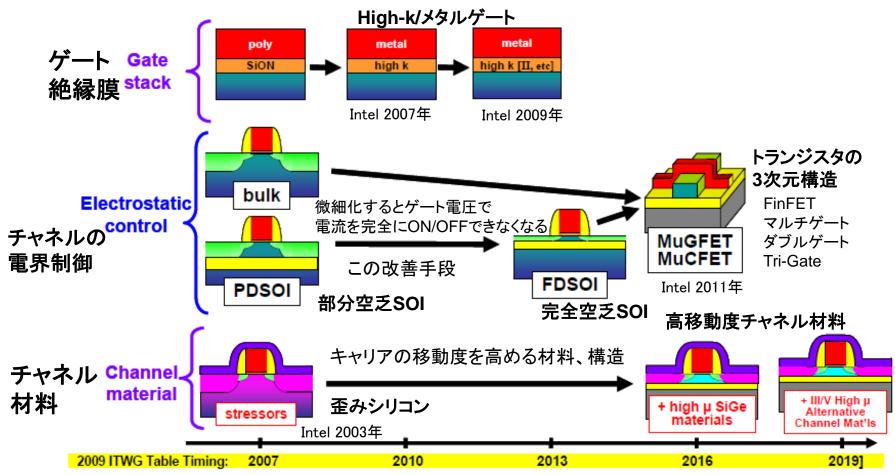

### 微細化トランジスタにおける高性能化技術

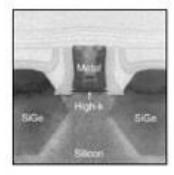

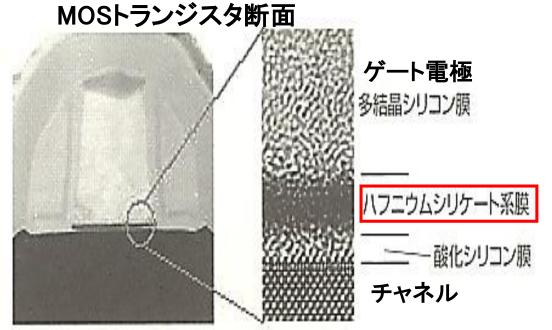

90nm以降の微細化では、特性劣化やリーク電流増加問題に対し新たな技術が採用90nm以降で歪シリコン技術が、45nm以降ではHigh-k/メタルゲート技術が、22nm以降では3Dトランジスタ構造であるマルチゲート(MuGFET)技術が量産使用。

(See also PIDS, FEP, ERD, and ERM chapters' text and tables for additional detail)

### Intelは微細化や高性能化でリードしてきた

•Intelは微細化、高性能化技術を他社に先駆け導入してきた。 歪シリコン、High-k MGや3DTri-Gate(FinFET)技術は約3年半先行

・2014年頃から、TSMCやSamsungなどが追い上げ、時間差が縮小へ

2003

90 nm

2005

65 nm

2007

45 nm

2009

32 nm

2011

22 nm

Invented SiGe Strained Silicon Strained Silicon

2<sup>nd</sup> Gen. SiGe

Invented Gate-Last High-k Metal Gate

2<sup>nd</sup> Gen. Gate-Last High-k Metal Gate

First to Implement Tri-Gate

Strained Silicon

High-k Metal Gate

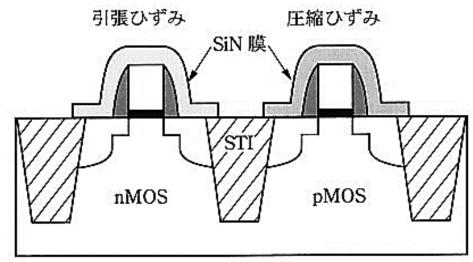

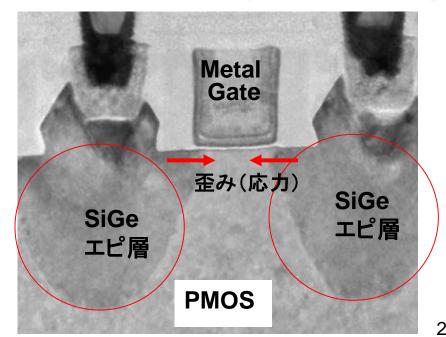

### 高性能化技術: 歪シリコン技術

#### MOSトランジスタのチャネル部に物理的ひずみを印加してキャリア移動度を高める。

#### 局所ひずみ印加方法

ー軸性ひずみの場合は、NMOSとPMOSで印加 すべき歪方向が異なる。

SiN膜の成膜条件を工夫し、2種類の膜を堆積。 NMOSが引っ張りひずみ、PMOSが圧縮ひずみ を印加すると移動度が高まる。

PMOSでは55%も移動度が高まる。

#### <u>Intel第4世代歪みシリコン技術(32nm)</u>

SiGeエピ層のGeがチャネルに歪み与える

GeはSiに比べて約 4%原子サイズが大きい。 このためSiに物理的歪が加わり、電子やホール がSi原子の間を通りやすくなり移動度が高まる。

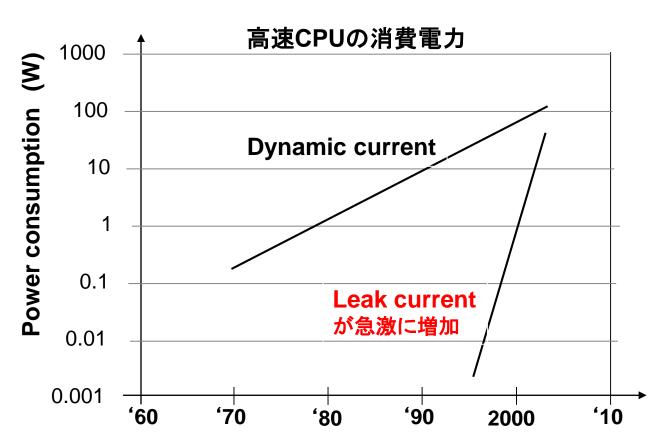

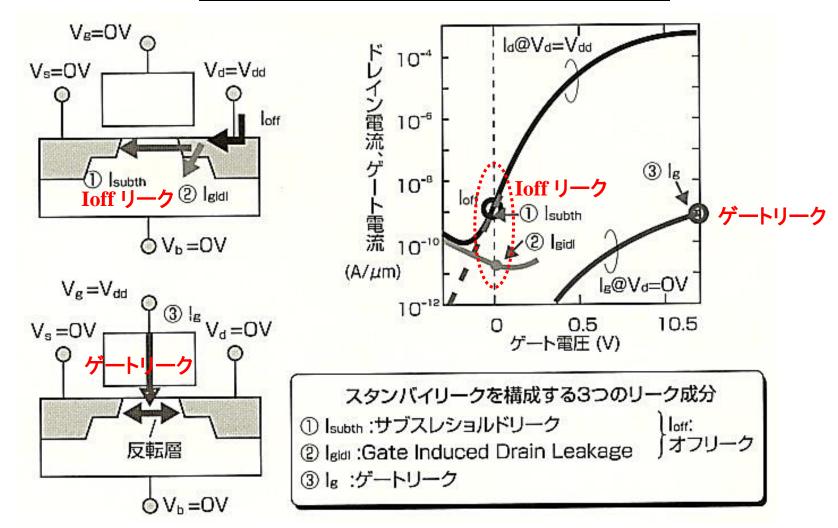

## トランジスタの微細化問題:リーク電流の増加

微細化でリーク電流による消費電力増大が大きな問題に(特にスマホなどの携帯機器)

消費電力  $P_d pprox fC_L V_{dd}^2 + I_{leak} V_{dd}$

f:動作周波数、CL:容量、

Vdd:電源電圧、Ileak:漏れ電流

容量のスイッチング電力

微細化により影響が顕著に

東工大松澤先生講義テキストから 27

### 微細化における問題点:リーク電流の増大

#### 微細化によるスタンバイリーク電流の増大

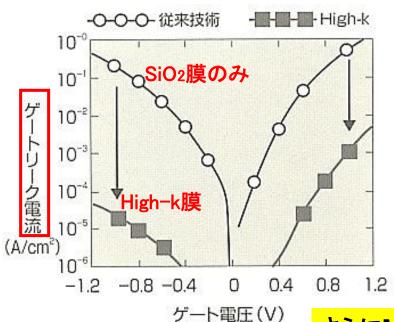

## ゲートリーク電流対策: HKMG(High-k/Metal Gate)

#### ゲートリークの低減(High-k材料)

ゲート酸化膜が薄くなり(1nm)、トンネル電流(リーク)が増大する。 そこで、High-Kゲート絶縁膜使用により ゲート酸化膜の厚みを確保して、 大幅なゲートリークを低減。 (SiO<sub>2</sub>酸化膜のみより2桁以上の低減)

### 代表的なゲート絶縁膜の誘電率

$SiO_2$ (二酸化シリコン)の比誘電率=3.9

Si<sub>3</sub>N<sub>4</sub>(窒化シリコン)=7

HfSiO(ハフニウムシリケート)=12~20

HfO(ハフニウム酸化物)=20~24

さらにMG(Metal Gate):ゲート材料をポリシリコンから メタル材料にかえてトランジスタ性能を向上

### loff リーク電流対策

#### ボデ<u>ィバイアス</u>:

サブスレッショルドリークの低減。 ウェルにバイアス印加し閾値を上昇。 (NMOSでは負電圧印加)

#### 90nm以降でのボディバイアス技術

- 1.エクステンション/ポケット構造の最適化に よりショートチャンネル効果およびGIDLを 抑制

- 2.SSRウェル\*<sup>1</sup>採用 (表面は低濃度、深部 で高濃度の逆傾斜構造)

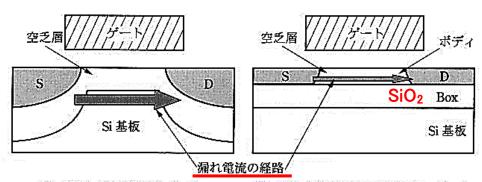

#### SOI(Silicon on Insulator):

SOI基板では、埋め込み酸化膜(BOX)上の 薄いSi層にチャネルが形成される。 これがドレイン一ソース間の電流通路となるが、 この通路が極めて薄いため、ゲート電界で完全 制御され漏れ電流が抑えられる。 右図のFD SOI(完全空乏型SOI)

(a) バルク MOSトランジスタ

(b) 完全空乏型 SOI MOSトランジスタ

SOI技術はIBM、AMDやSTMなどが 積極的に利用。 IntelはSOI技術は使用していない。

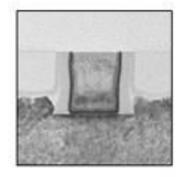

### 3D Tri-Gate/FinFETトランジスタ

従来の2次元構造FETではゲート電圧でS-D間の電流を完全にON/OFF制御できなくなる。 このためチャネル周囲をゲートで囲うTrigate/FinFETなどの3次元構造が必要となる

高性能化 **FinFET**

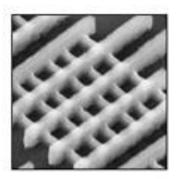

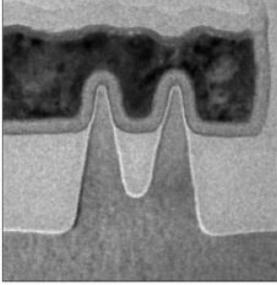

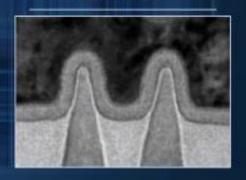

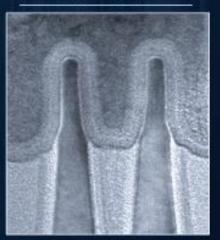

### Intel 第一世代22nmFinFETと第2世代14nmFinFET

2011年後半~

22nm FinFET

2013年後半~ 14nm FinFET

60nm Finピッチ

Finの本数で 駆動能力調整 42nm Fin ピッチ

42nmFin 高さ

34nm Fin高さ

Gateピッチ:90nm

配線ピッチ:80nm

SEM

Si Substrate

Gateピッチ:70nm

配線ピッチ:52nm

Si Substrate

Si基板

Si基板

第2世代は 狭ピッチ化 高Fin化

断面写真

### IntelのFinFETプロセス

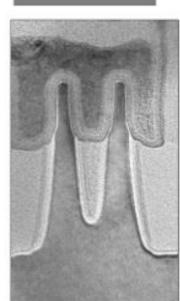

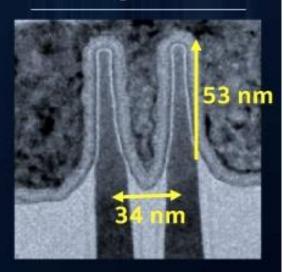

IntelはIEDM2006で22nmTri-Gate技術を発表 2011年に22nmで第1世代、2013年に14nmで第2世代、 2017年に10nmで第3世代量産開始 Intelの10nmは、フィンピッチが34nm、フィンの高さが53nm、 メタルピッチは最小で36nm、ゲートピッチは54nm Intel10nmは他社のFinFET 7nmプロセス相当

第1世代(2011年~)

第2世代(2013年~)

第3世代(2017年~)

## 22 NM

Finの高さ:34nm Finピッチ: 60nm

Fin幅:8nm

## 14 NM

Finの高さ: 42nm Fint<sup>°</sup>ッチ: 42m

Finの高さ:53nm

Fint<sup>®</sup>ッチ: 34nm

高性能化 FinFET

#### Intel22nm/14nm

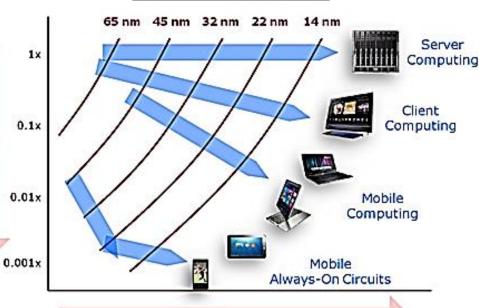

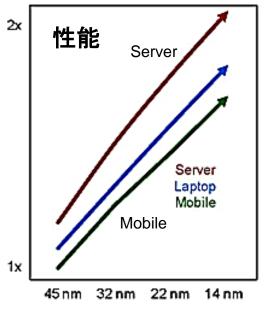

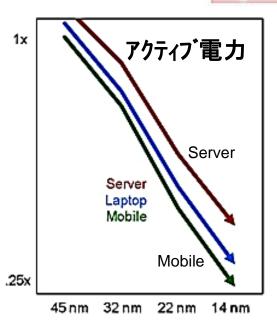

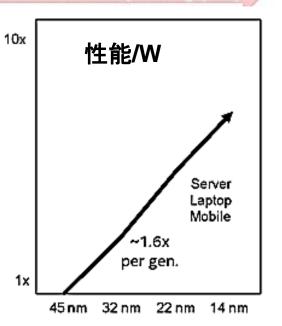

### 3D FinFETプロセス特徴

- •Intelは2014年に第2世代FinFET量産 22nmから14nmに微細化

- •FinFETは、高性能に活かす事も 低リーク低消費電力に活かす事も可能。

#### 性能 vs リーク電流

Higher Transistor Performance (switching speed)

Lower Leakage Power

### プレーナ型NANDの微細化限界

- ・プレーナ型NANDは、ほぼ16nm世代で微細化の限界。以後はチップ内3D化が必須とのシナリオ東芝は2014年9月に、"プレーナNANDは15nmで終了し以後は3D化へ移行"と発表

- ・2009年当時、2011~2012年に微細化限界を迎えるとしたが、NANDの微細化のスローダウンで、 3D化は3~4年程度先延ばし

#### NAND FLASH ROADMAP SUMMARY

### 2013年に示されたNANDフラッシュのシナリオ

- -2014年に10nm代前半プロセスでプレーナ型NAND限界に達する

- 2015年に3D化に本格移行して256GbitNAND量産とのシナリオ

- ・2014年現在、3D NANDのコスト問題は解決していない(同じ容量で微細化プレーナより高コスト)

日経WinPC 2013年11月号

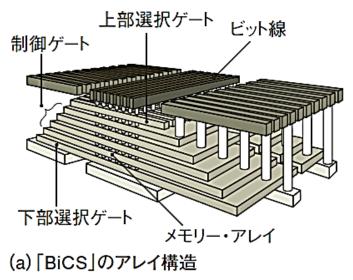

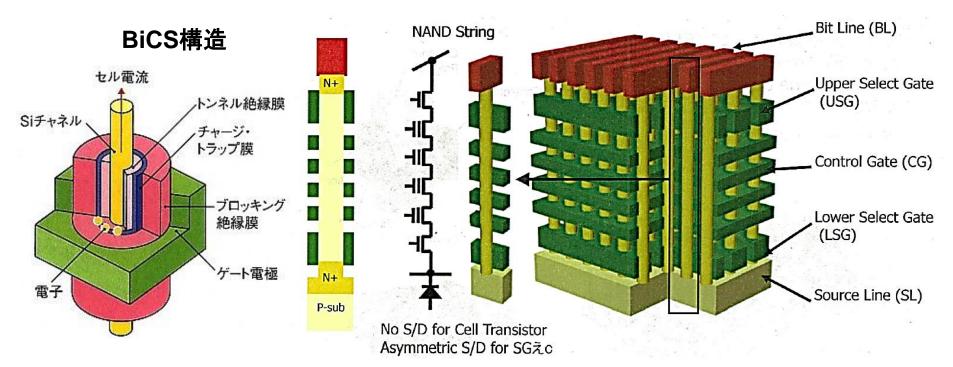

### 3D NAND技術は東芝が2007年に発表: BiCS Bit Cost Scalable

2007年に東芝が発表した3次元NANDフラッシュメモリ技術:BiCS BiCSは多層化しても製造コストが上がらない特徴(微細露光回数増えない)

図4 ●積層数を増やすほど低コストに 東芝の「BiCS」は、従来のセル積層技術とは異なり、積層数を増やすほどビット・コストを低減できる。1回のリソグラフィ工程で、複数の層を形成できるためである。同社のデータ。

ビット・コストの相対値=

$$\frac{1}{n}$$

( $C_f + nC_v$ )  $\left(\frac{1+A}{1-Y}\right)^{n-1}$   $n$ =層数  $C_f =$ 各層が共有する領域のコスト  $C_v$ =1層当たりのコスト  $A$ =1層当たりの歩留まり損

(b) [BiCS]のビット・コスト

# チップ内3D NANDフラッシュBiCSの構造

#### 東芝

#### BiCS概要:

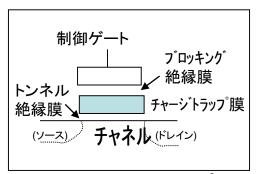

電極膜と絶縁膜を交互に積層し、この積層構造を貫通する 孔をRIE(反応性イオンエッチング)を用いて一度にあける。 孔の側面にメモリ膜(トンネル絶縁膜、チャージトラップ膜、 ブロッキング膜)を形成し、孔をポリシリコンで埋める。 積層電極膜、孔の側面に形成したメモリ膜、孔を埋めたポリ シリコンがチャネルとなり、セルが多層に一度に形成される。

チャージトラップ型 NANDフラッシュ

### 各社Vertical Channel 3D NAND構造

- 3次元NANDは2007年に東芝がBiCSとして発表

- •Samsung,Hynix,MicronがBiCS構造をベースに開発

- ・Samsungは2009年にBiCSの問題を改善したTCAT発表。2013年8月V-NANDとして量産開始

|                 | p-BiCS (Toshiba)                      | TCAT (Samsung)                                                                                         | 3D FG (Hynix)       | Micron            |

|-----------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------|-------------------|

| Structure       | Bit Line Source Line  SG  CG  PC  Sit | Poly Si Chausel  SML  SML  SML  SML  Control  Gate  (Will)  Tran SiN  Blocking Layer  CSL  Gate  p-Sub | CG FG CG            |                   |

|                 | Tanaka. H, VLSIT 2007                 | J. Jang, VLSIT 2009                                                                                    | S. Whang, IEDM 2010 | G. Hawk, FMS 2011 |

| Key<br>Features | - P+ SONOS Cell                       | - TANOS Cell                                                                                           | - Floating Gate     | ?                 |

| Key Issue       | - Large Cell Size<br>- Reliability    |                                                                                                        |                     | ?                 |

V-NANDとして 2013年商品化

# 東芝&Samsung 3D NAND ISSCC2017

#### 東芝3D NAND BiCS 512Gbit 64層

|                        | [1]     | [2]     | [4]                 | (5)                 | [6]                                    | This work                             |

|------------------------|---------|---------|---------------------|---------------------|----------------------------------------|---------------------------------------|

| ISSCC paper            | 2012    | 2013    | 2015                | 2016                | 2015                                   | 2017                                  |

| Technology             | 20 19nm | 20 20nm | 30 32WL layers      | 30 48 WL layers     | 30 Floating Gate<br>(No of layers mis) | 3D 64 WL layers                       |

| Bas percell            | 3       | 3       | 3                   | 3                   | 3                                      | 3                                     |

| Capacity               | 128Gb   | 129Gb   | 128Gb               | 256Gb               | 768Gb                                  | 512Gb                                 |

| Die size [mm²]         | 1706    | 1465    | 689                 | 976                 | 1792                                   | 132                                   |

| Bt density<br>[Gb/mm²] | 075     | 087     | 186                 | 262                 | 4 29                                   | 388                                   |

| Read operation time    | n/a     | 90us    | 45us<br>(4 KB page) | 45us<br>(4 K8 page) | n/a                                    | 64us (8 KB page)<br>80us (16 KB page) |

| Program<br>throughput  | 18MB/s  | n/a     | n/a                 | 53MB/s              | 44MB/s                                 | 46MB/s                                |

#### Samsung3D NAND BiCS 512Gbit 64層

|               | Previous work [3]                       | This work                               |

|---------------|-----------------------------------------|-----------------------------------------|

| Bits per cell | 3                                       | 4                                       |

| Density       | 256Gb                                   | 512Gb                                   |

| Chip size     | 97.6mm² (2.62Gb/mm²)                    | 128.5mm² (3.98Gb/mm²)                   |

| Technology    | 3D NAND with 48 stacked WL layer        | 30 NAND with 64 stacked WL layer        |

| Organization  | 16KB/Page,576Pages/Block,3776Blocks/Die | 16KB/Page,768Pages/Block.5748Blocks/Die |

| I/O Bandwidth | Max. 1Gb/s                              | +                                       |

| vcco          | 1.8V                                    | 1.8V(Legacy), 1.2V(Low power)           |

| tBERS         | 3.5ms (Typ.)                            | +                                       |

| tPROG         | 660us                                   | 700us                                   |

| tR (4KB)      | 45us                                    | 60us                                    |

40

# 3D NAND動向

3D NANDは当初予定より遅延。プロセスが予想以上に難しかった(エッチング工程や膜形成など)装置性能向上や、歩留まり向上にAI技術活用し、2017年やっと本格量産に至ってきた

- ・NAND3社(Samsung,東芝/WD、Micron-Intel)は64層256G~512Gbit(TLC)を量産開始

- 東芝は64層で768Gbit(QLC)サンプル提供(2017.6)

- 東芝は96層512Gbit(TLC)を開発

#### <u>Samsung Electronicsの3D NAND技術世代</u>

#### シリコンダイ面積 技術 発表年月 多值化方式 シリコン の特層数 (nbit/セル) ダイの記 世代 名称 憶容量 V1 24層 MLC(2bit/セ 128Gbit 133平方mm 2013年8月(FMS) (ISSCC2014) 2014年2月(ISSCC) 16) V2 32層 MLC版とTLC 128Gbit 68.9平方mm(TLC 2014年8月(FMS) (3bit/セル) 版、ISSCC2015) 2015年2月(ISSCC) 版がある V3 48厘 TLC(3bit/+2 256Gbit 97.6平方mm 2015年8月(FMS) ル) (ISSCC2016) 2016年2月(ISSCC) V4 64層 TLC(3bit/12 512Gbit 128.5平方mm 2016年8月(FMS) ル) (ISSCC2017) 2017年2月(ISSCC) V5 QLC (4bit/+2 不明 2017年8月(FMS) 1Tbit 未公表 (96層?) 16)

#### 東芝-Western Digital (WD)連合の 3D NAND技術世代

| 技術世代<br>名称 | ワード線<br>の積層数 | 多値化方<br>式(nbit/セ<br>ル)                  | シリコンダイの<br>記憶容量                 | シリコンダイ<br>面積                       | 発表年月                                |  |

|------------|--------------|-----------------------------------------|---------------------------------|------------------------------------|-------------------------------------|--|

| BICS1      | 24層          | MLC(2bit/<br>セル)                        | 不明                              | 不明                                 | 2012年2月<br>(SanDiskのアナリ<br>スト向け説明会) |  |

| BiCS2      | 48層          | 層 MLC(2bit/<br>セル)とTLC<br>(3bit/セ<br>ル) | 128Gbit (MLC)<br>£256Gbit (TLC) | 不明                                 | 2015年8月 (FMS)                       |  |

| BICS3      | 64層          | TLC(3bit/セ<br>ル)                        | 256Gbit(TLC) &<br>512Gbit(TLC)  | 132平方mm<br>(512Gbit,<br>ISSCC2017) | 2016年8月 (FMS)<br>2017年2月 (ISSCC)    |  |

| BiCS4      | 96層          | TLC(3bit/セ<br>ル)                        | 256Gbit(TLC)と<br>512Gbit(TLC)   | 不明                                 | 2017年6月 (リリー<br>ス)<br>2017年8月 (FMS) |  |

2017 Copyright by Akira Fukuda. All rights reserved.

2017 Copyright by Akira Fukuda. All rights reserves.

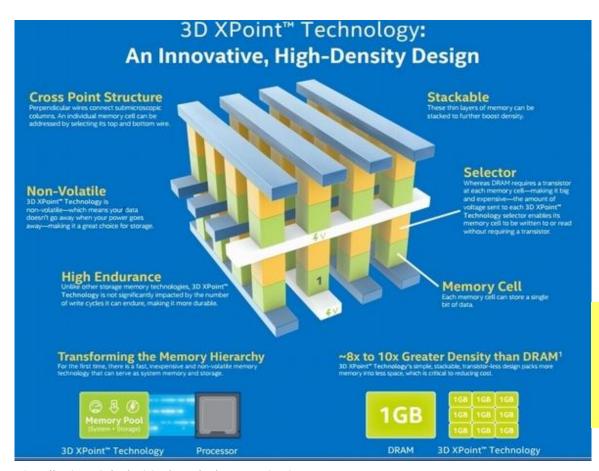

### Intel+Micro 128Gbit 3Dクロスポイントメモリ

- ·X,Y方向配線のクロス部分にメモリセルを形成。

- ・20nmプロセス、128Gビット容量で640億個の2層構造メモリセル

- ・メモリセルは抵抗変化する材料(ReRAMか相変化メモリと推測。詳細発表なし)

- ・NAND型フラッシュメモリよりも1000倍高速で、DRAMよりも8~10倍、記憶密度が高い

- NANDよりも1000倍の耐久性

### 20nmプロセス128Gbit 3D XPoint メモリ

Intel+Micronも 3DXPointメモリ量産にたいへん 苦労している様子。 新たな材料が数十以上も必要。

# 3次元(3D)実装技術のいろいろ

現在の量産レベル3次元実装は、ワイヤボンディングやパッケージオンパッケージ(PoP)積層レベル

| 平面構造 |                | Wire Bonding Type Flip Chip Type                                               |

|------|----------------|--------------------------------------------------------------------------------|

| 3次元  | チップ間<br>ビア経由接続 | Wire bonding Die-stacked Wire Bonding + Flip Chip (WLCSP) Type Package stacked |

| 構造   | チップ間<br>直接接続   | Wire Bonding + Flip Chip (WLCSP) Type  TSV                                     |

| 内蔵構造 |                | Chip Embedded + 3D Chip Embedded Type Type                                     |

|      |                | Package in Package                                                             |

WL : Wafer Level パッケージ内

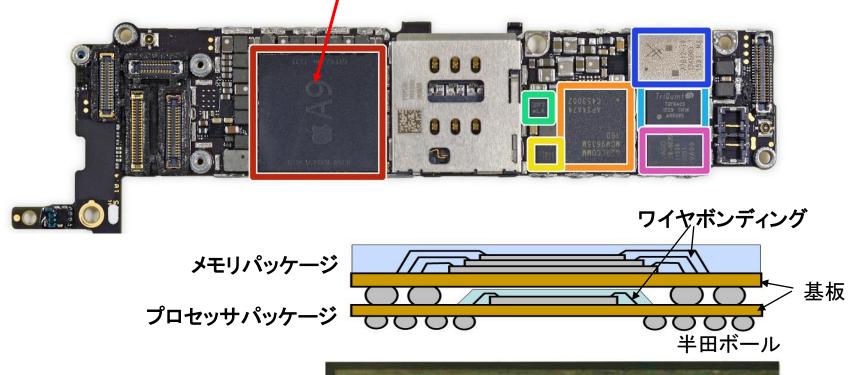

# 3次元実装技術: PoP(Package on Package)

現在のスマホ用プロセッサとDRAMでは、ほとんどこのPoP実装技術が使用されている

PoP(Package on Package)

iPhone 6S 回路基板 A9アプリケーションプロセッサ+2GB DRAM

一般的なPoP構造の例

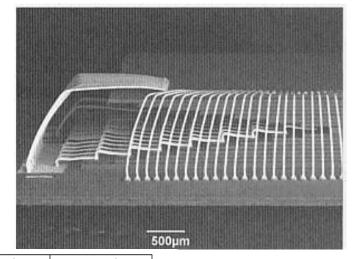

# NAND積層技術 ワイヤボンデング:東芝

2009年資料

#### 18 μ m極薄のNANDを33段ワイヤボンディングで積層

- ・東芝はダイシングしてから裏面を削るDBG技術 (Dicing before grinding)によりウェハを18μmまで極薄化。

- 15 μ mまでは動作確認済みだが、量産は18 μ m限界か。

- •TSV技術はコスト競争激しいNANDでは当面採用無理 TSV技術は高速DRAMの積層化など高速化でメリット大きい。

5段/2GB

50µm

2005年 2006年 2007年 2008年 2009年 2010年 要求容量 4GB 8GB **16GB** 32GB **64GB** SSDなど 容量記録デバイ -タの記録 MCP 1.4mm厚9段 1.2mm厚10段 PoP 1.0mm厚3段 1.0mm厚2段 1.0mm厚6段 17段/64GB 33段/128GB eMMC/eSD 9段/32GB

9段/8GB

25µm

17段16GB

$20\mu m$

19段/32GB

$18\mu m$

現状の最大容量 SDXCカード512GB 128Gbit Chipだと33枚 256Gbit Chipで17枚 のチップが必要

45

カード

チップ厚

3段/2GB

$70\mu m$

#### パッケージ内

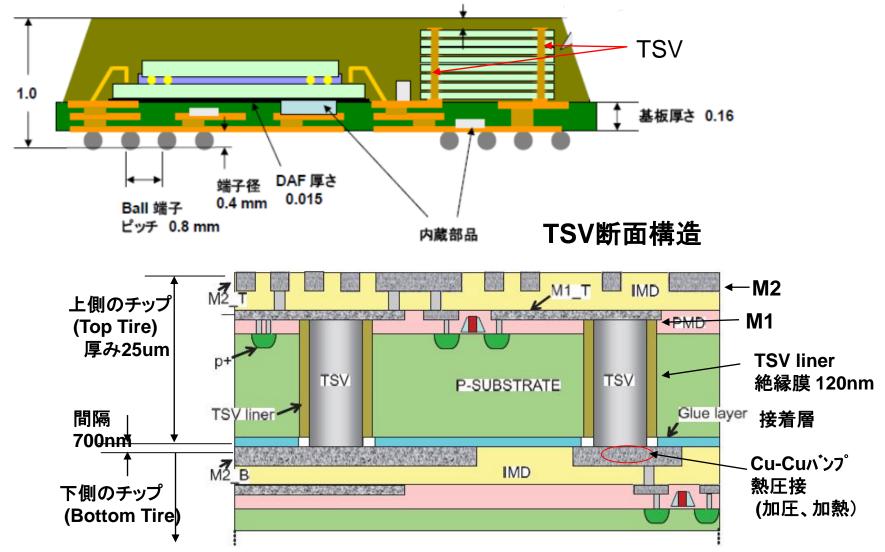

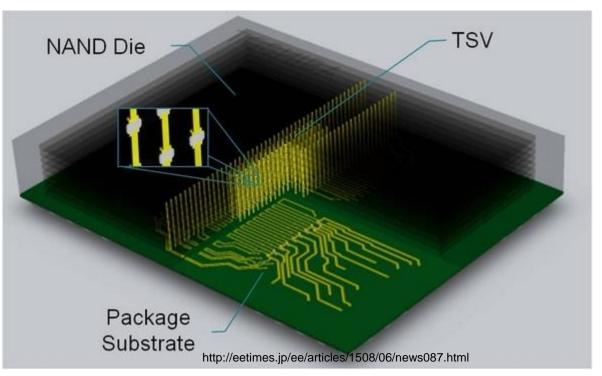

### 3次元実装技術: TSV(Through silicon Via:シリコン貫通ビア)

TSVはSi基板を薄化して、基板上下を貫通する穴を開け、Si基板を積層して接続する技術

IMD (Inter-Metal Dielectric) 層間絶縁膜 PMD(Pre-Metal Dielectric) 膜

2017年7月

- ・48層3D NAND にTSVを適用し、書き込みバンド幅と低消費電力性能を向上 ワイヤボンディングを用いた製品に比べて電力効率を約2倍向上

- ・512G bit(TLC)チップを単一パッケージ内に16段積層し、総容量1Tバイトの大容量化

- •BiCS FLASHはパッケージがNAND Dual x8 BGA-152で、インタフェース規格がToggle DDR

- ・容量512GB(8層)の製品と容量1TB(16層)の製品があり、サイズは512GBが14×18×1.35mm、後者が14×18×1.85mm

- ・サンプル出荷は2017年中に開始予定

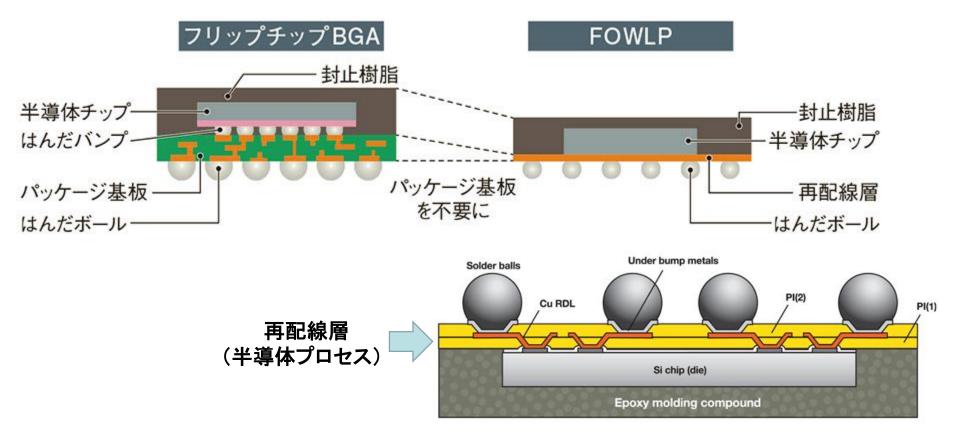

### **FOWLP (Fan-out Wafer Level Package)**

#### AppleがA10で採用 (iPhone7)

従来のフリップチップBGAに置き換わる実装方式として、「FOWLP」が注目を集めている。大きな違いはパッケージ基板がないこと。代わりにチップの端子から配線を引き出す再配線層を半導体工程で作り、外部端子につなげる。パッケージ基板がないため、「パッケージが薄い」、「配線長が短く伝送が速い」、「パッケージ基板の分、コストが安い」といった特性を実現できる

**TSMC**

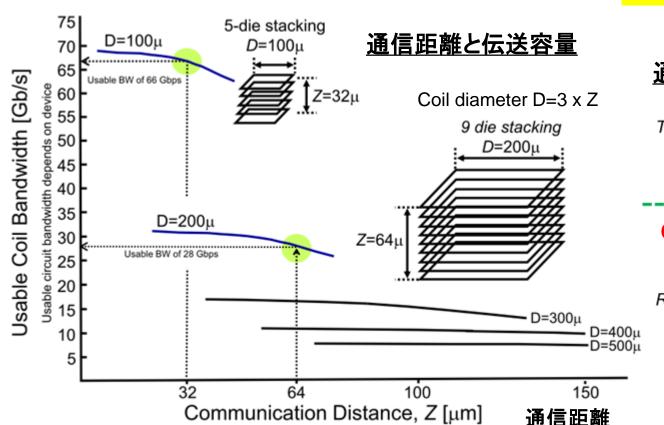

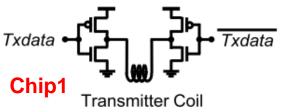

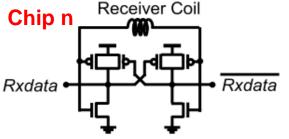

# チップ間、磁界結合: Thrue Chip Interface (TCI)

- ・慶応大学黒田先生チームが研究してきたチップ間、磁界結合技術が実用化に向かいだした

- ・従来コイル寸法が大きすぎたが、チップの薄化技術(DRAMを4µm厚に研磨しても正常動作)で、 8枚積層して60µmサイズのコイルで通信可能になった。

- ・チップの薄化以外に追加プロセス不要。 またTSVのようにESD対策ダイオードも不要

PEZY(国内ペンチャ)は 次期スパコンchipに、 このTCI技術を採用予定

#### 通信回路は極めてシンプル

送信、受信用コイルの 巻き数は4 turn

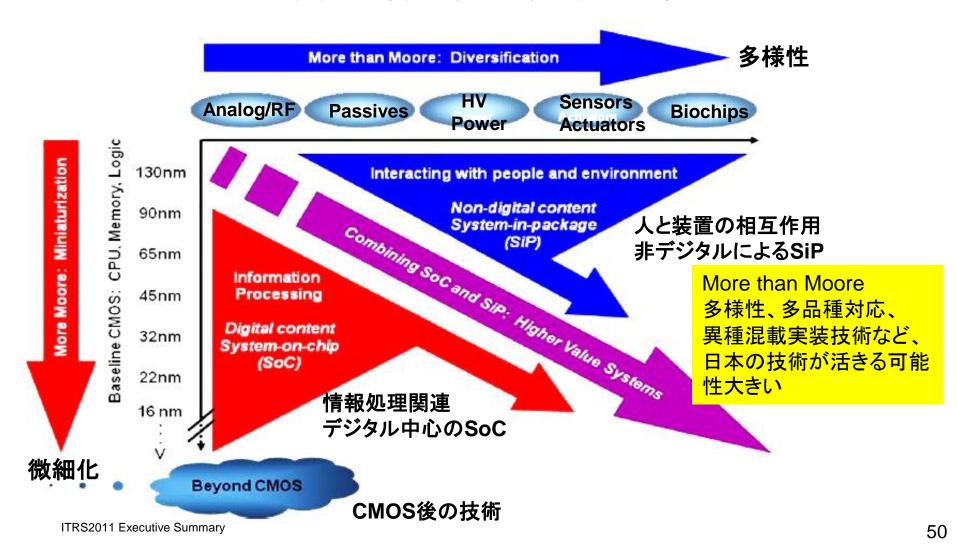

## More Moore Le More than Moore:

- •More Mooreによる微細化がスローダウン。等価スケーリングにてMooreの法則維持 今後はチップ内3次元化と高移動度チャネル材料がMore Mooreのキー

- ・近年More than Mooreの多様化に関する論文発表が多い。異種チップの融合など