第340回 アナログ集積回路研究会講演

# 2017年版 第5回 半導体製造プロセス

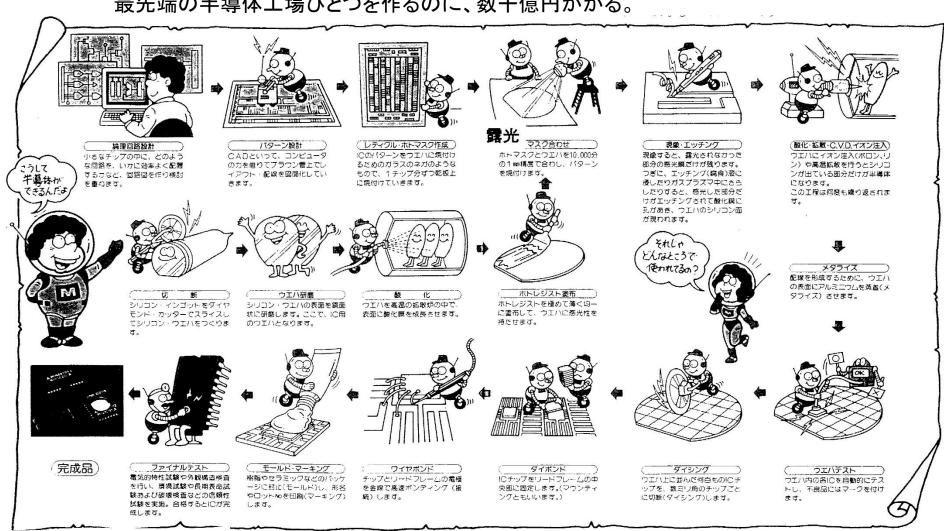

1)半導体製造プロセスの概要 製造プロセス概観 設計工程、マスク製作、ウェハ製造工程 前工程(トランジスタ工程、配線工程) 後工程(ダイシング、実装、試験)

- 2)SEM断面写真に見る最近のデバイス例

- 3)主な半導体製造装置 マスク描画、光露光、イオン注入、成膜、エッチング、 洗浄、ダイシング、試験装置

- 4)次期露光装置EUV概要と動向

2017.10.31 東京電機大学非常勤講師 群馬大学非常勤講師 中谷 降之

# 半導体製造プロセス

半導体は、最先端の技術を駆使して非常に複雑な工程を経て作られる。最先端の半導体工場ひとつを作るのに、数千億円かかる。

SEAJ/三菱電機資料

# 半導体の製造プロセス概要

1)<u>LSI設計</u>

CAD(EDA)ツール用いて回路設計し 原版マスクを作成

- 2)<u>シリコンウェハ製造</u> シリコンを精製して、インゴッド を作り、スライスしてウェハを 作成する工程

- 3)LSI製造(右図プロセス) シリコンウェハ上に多数のLSIを 作り込む前工程は、300~400 もの多数のプロセス・ステップから なっている。

後工程は、前工程により完成した ウェハを試験し、切り離して それぞれをパッケージに 搭載して最終検査までの工程

| 前工程    | 拡散工程                                         | フロントエンド: FEOL                           | 成膜            |

|--------|----------------------------------------------|-----------------------------------------|---------------|

|        | (ウェハエ程)                                      | (下地工程)                                  | 露光(フォトリソグラフィ) |

|        |                                              | (トランシ・スタエ程)                             | エッチング         |

|        |                                              | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 不純物添加         |

|        |                                              | バックエンド:BEOL                             | 熱処理           |

|        |                                              | (上地工程)                                  | CMP(化学機械的研磨)  |

|        |                                              | (配線工程)                                  | 洗浄            |

|        |                                              | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Į į           |

|        | G/W工程(ウ                                      | ェハプローブ試験)                               | ウェハ特性チェック     |

|        | <u>                                     </u> |                                         |               |

| 後工程    | 組立工程                                         |                                         | ダイシング         |

|        |                                              |                                         | <b>\</b>      |

|        |                                              |                                         | マウント          |

|        |                                              |                                         | <b>\</b>      |

|        |                                              |                                         | ボンディング        |

|        |                                              |                                         | <b>↓</b>      |

|        |                                              |                                         | 封入            |

|        |                                              |                                         | <b>1</b>      |

|        | 仕上げ工程                                        |                                         | メッキ           |

|        |                                              |                                         | <b>↓</b>      |

|        |                                              |                                         | リード成型         |

|        |                                              |                                         | <b>1</b>      |

|        | 選別·BT工程                                      | (試験工程)                                  | 特性チェック        |

|        |                                              |                                         | <b>↓</b>      |

|        |                                              |                                         | バーン・イン        |

|        |                                              |                                         | ↓             |

|        |                                              |                                         | 特性チェック        |

|        |                                              |                                         | <b>↓</b>      |

|        | 検査工程(信頼性試験工程)                                |                                         | 入庫検査          |

|        |                                              |                                         | <b>↓</b>      |

|        |                                              |                                         | 信頼性試験         |

|        |                                              |                                         | <b>↓</b>      |

|        |                                              |                                         | 出荷検査          |

|        |                                              |                                         | <u> </u>      |

| Note ( | G/W:Good Wafer                               | ,BT:バーンインテスト                            | 出荷            |

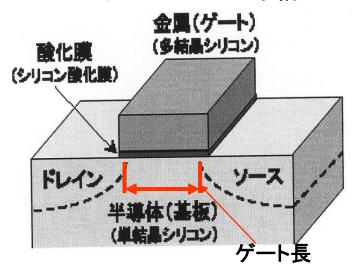

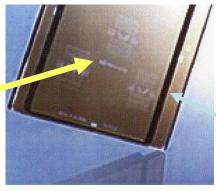

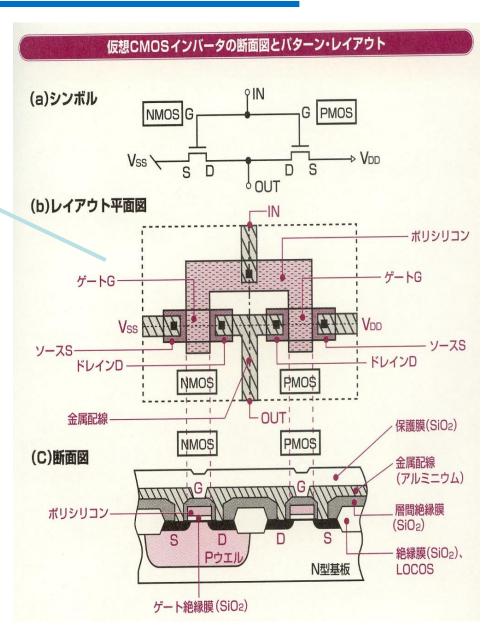

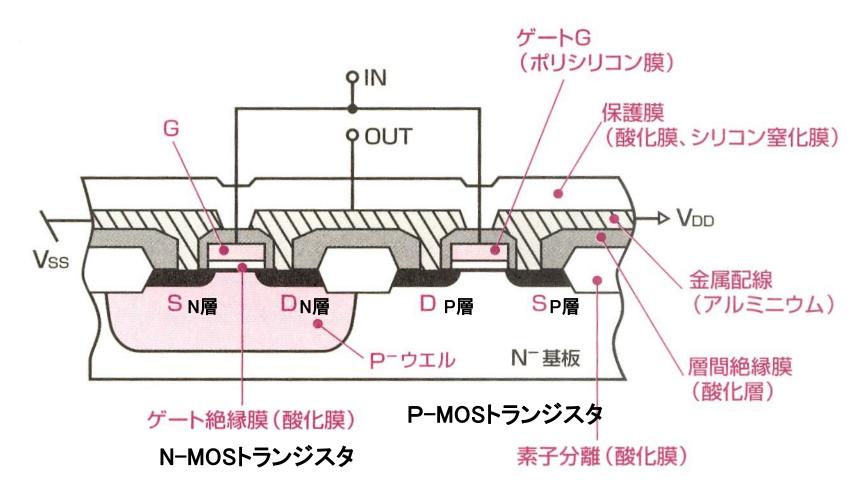

# トランジスタエ程: FEOL front-end of line

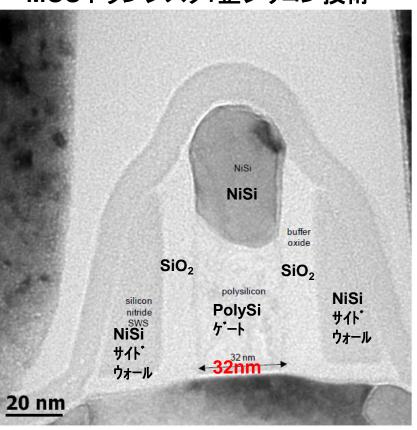

#### MOSトランジスタの基本構造

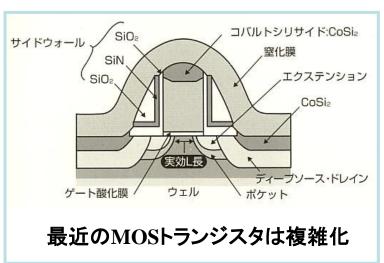

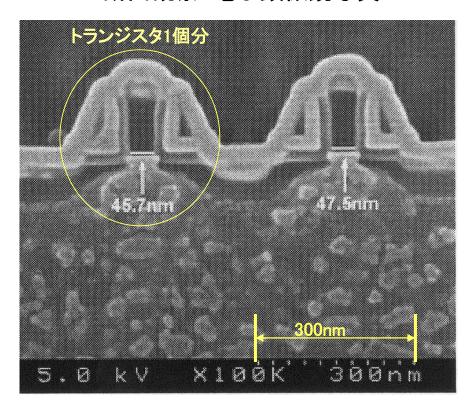

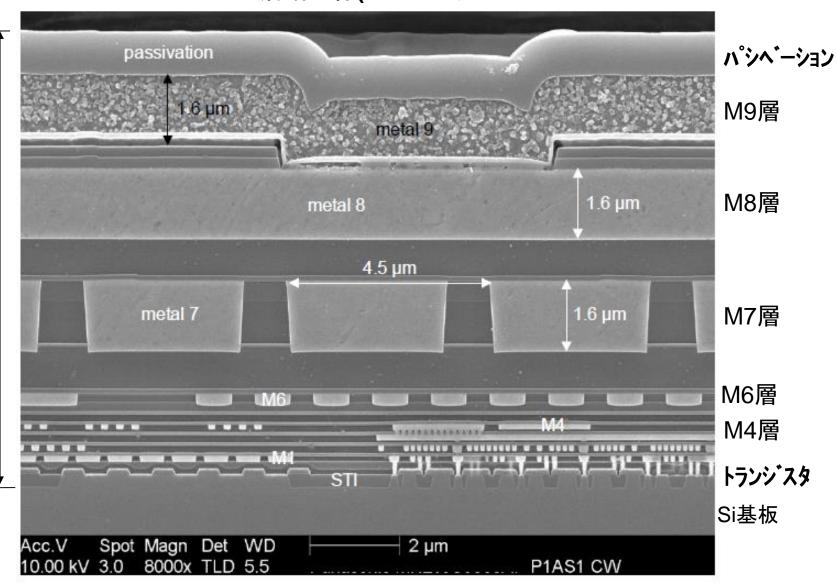

#### LSIの断面観察:電子顕微鏡写真

SONY PSX用チップ: 90nmプロセス(ケート長45nm)

Chipworks社データ 2004.1

Chipworks社元 与 2004.1

約10μm

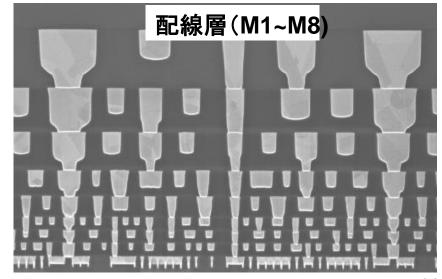

# 配線工程:BEOL back-end of line

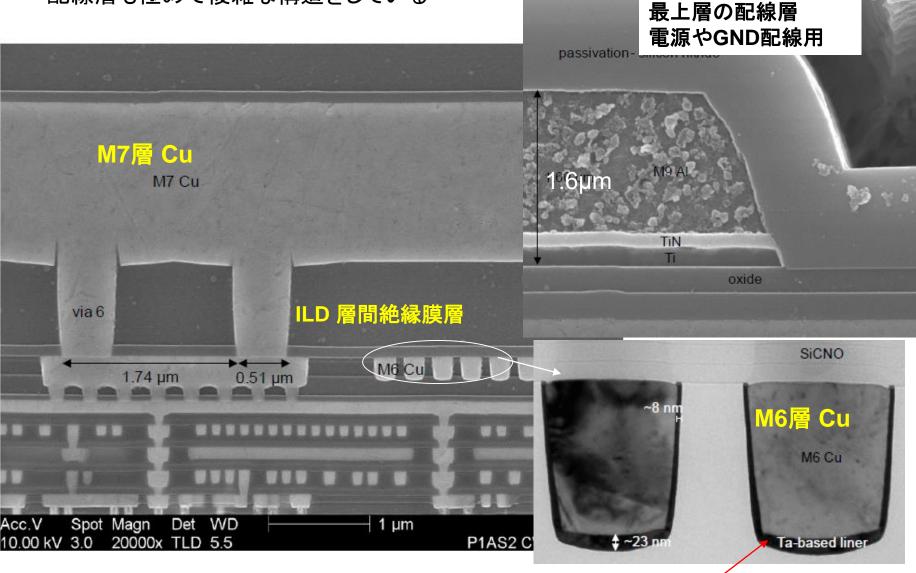

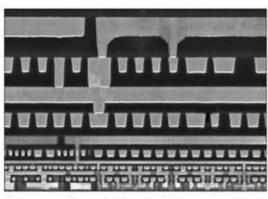

45nm SOC M1~M9層銅配線(Cuメタル)

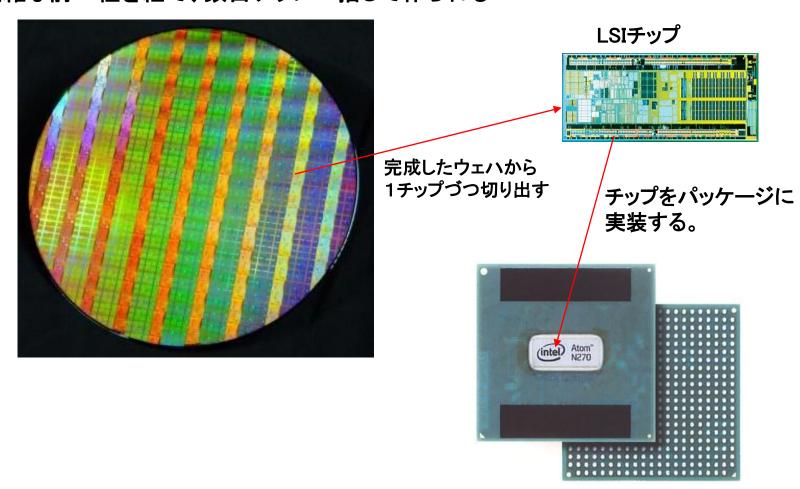

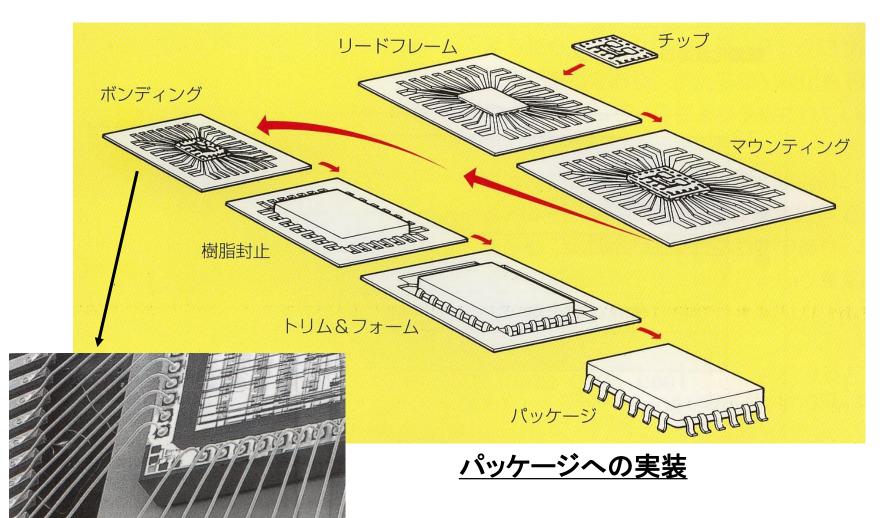

#### 後工程プロセス

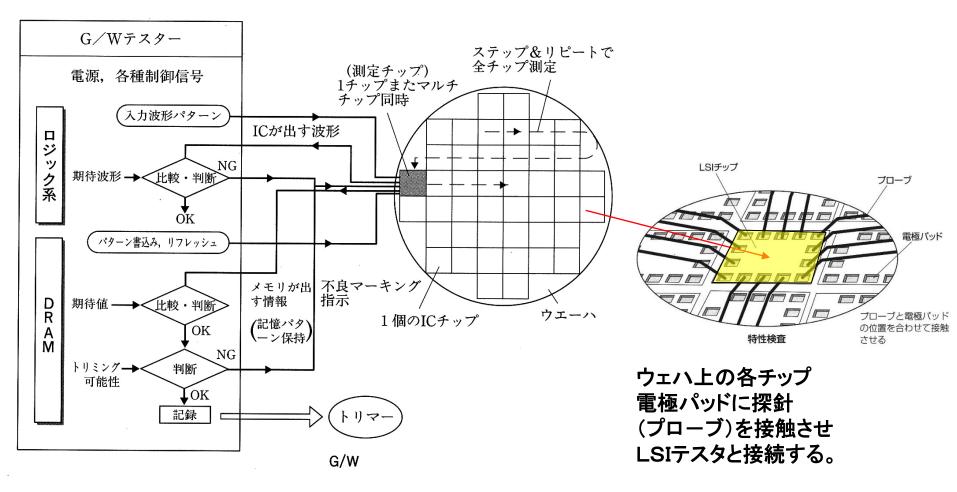

## ウェハ上に一括して作られたチップを切り出し実装しテスト

半導体はシリコンウェハ(直径300mm)上に 複雑な前工程を経て、数百チップ一括して作られる

半導体テストシステムで全数試験して良品のみ出荷

6

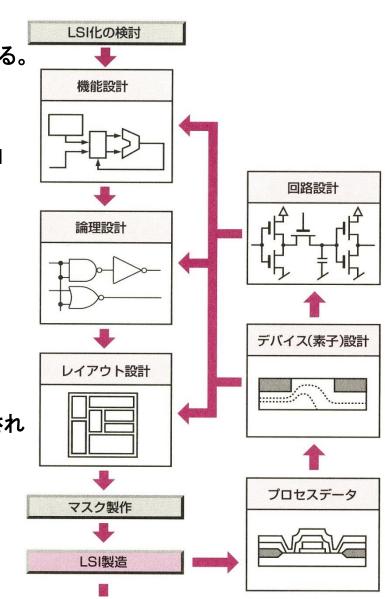

## LSI設計フロー概要

LSI設計はほとんどCAD (EDA)ツールにより行われる。

HDL言語設計 (ハート・ウェア記述言語) 最近はC言語設計も増加 シミュレーションで検証

論理合成ソフトにて、 言語記述されたものが 論理回路に変換される。 シミュレーションで検証

トランジスタレベルから デバイスレベルに変換され レイアウトに落とされる。 シミュレーションで検証。

最終的に20-30枚の マスク(原版)作成

論理機能の電気的仕様 を満足させる回路構成 (使用半導体プロセスに よるトランジスタ構成など) を詳細に決定。

試作(TEGなど)して データ所得し 設計データへフィート・ハ・ック TEG:Test Element Group

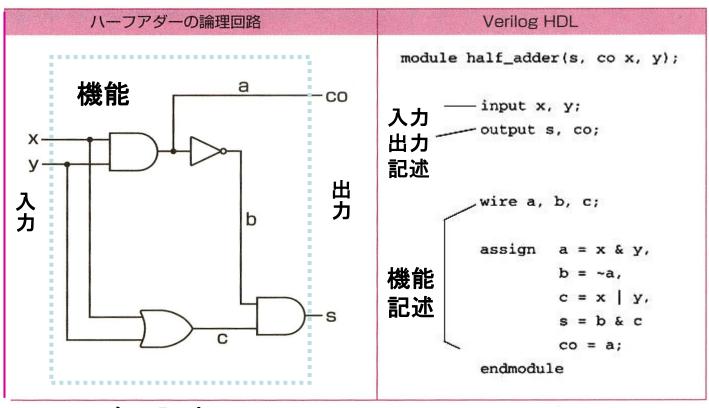

## LSIの設計:言語設計

LSIの大規模化や機能(IP)再利用化により、言語設計が必須となった。 一般的に使用されるHDLには Verilog HDL と VHDL がある。

#### システムを記述するハードウェア記述言語(VerilogHDLの例)

回路図記述

言語(HDL)記述

# LSIの設計:マスク製作

フォトマスク(マスクまたはレチクルとも言う)は、パターン露光用の原版。

描画前フォトマスク 描画済フォトマスク (マスクブランクス:約150x150x6.4厚mm)

パターンレイアウトにより20-30層の フォトマスクを作成。

フォトマスクは、石英ガラスに金属クロムが 80nmの厚みで塗布されたものを、マスク描画 EB露光装置にて露光。

マスクはx4サイズの原版となる。

最近の先端LSIでは、マスクセット1式が数億円に達する。

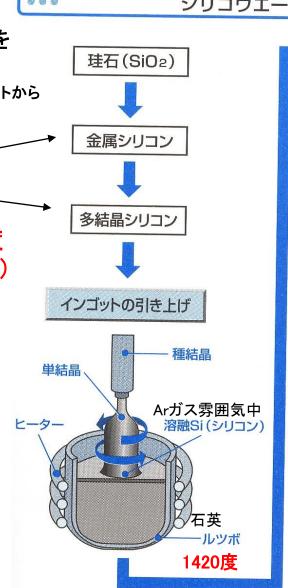

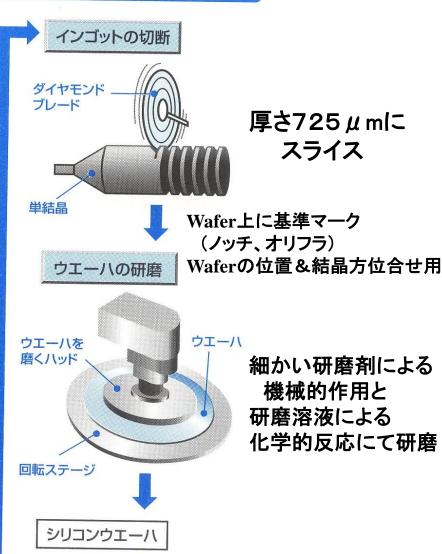

## シリコンウェハ製造工程

シリコウエーハ製造工程・・・・

1トンの金属シリコンを作るのに、1,500万Wの電力必要(ボーキサイトからAlを作るのとほぼ同じ電力)

98~99%純度

99.9・・9% イレブンナイン純度 (9が11個並ぶ純度)

多結晶シリコンから、 結晶引き上げにて 単結晶シリコンの インゴットを製造。

多結晶シリコン: 結晶方位がバラバラ

単結晶シリコン: 結晶方位が揃っている

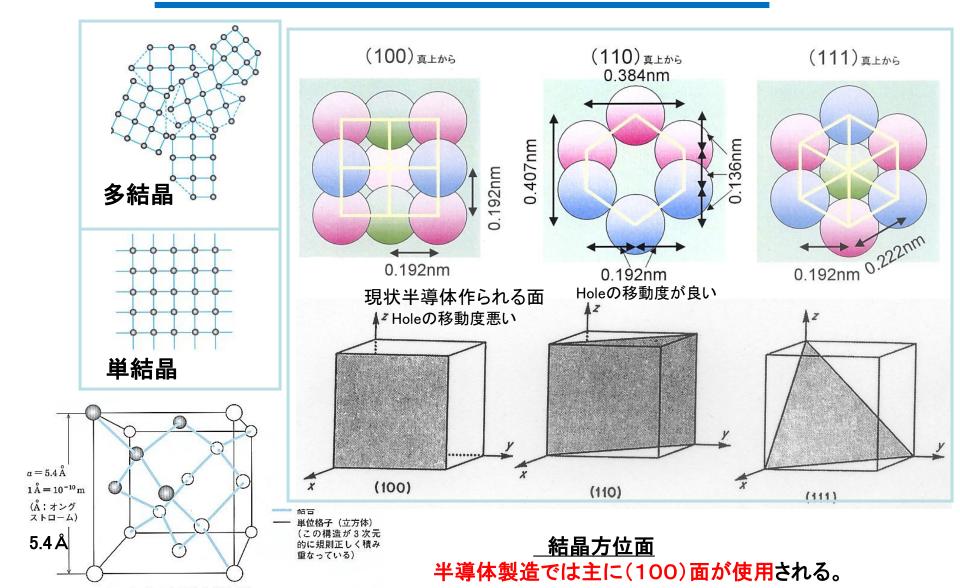

# 半導体で使われるSi結晶面

灰色の球は結晶の規則性を表す最も基本的な構造で, 基本格子と呼ばれる.

Si単結晶構造:ダイヤモンド構造

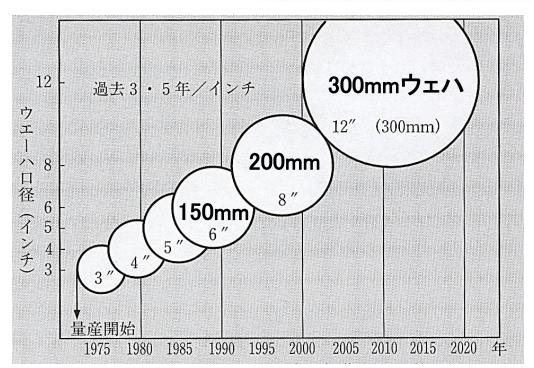

## シリコンウェハの大口径化

#### シリコン・インゴットとウェハ

生産性向上(コスト低減)のため、 ウェハを大口径化してチップ取れ数を 増大してLSI製造コストの低減が 図られてきている。

300mmウェハでのチップ取れ数例

•NANDフラッシュ:約 500個

•DRAM : 約 1000-1200個

300mmの次は450mmウエハ。 量産開始は当初予定より大幅に遅れ 現状、2020年代前半との予測

| 00 | シリコウエーハロ | ]径とチップ取れ数 |

|----|----------|-----------|

|----|----------|-----------|

|             |         | 取れ数       |             |  |

|-------------|---------|-----------|-------------|--|

|             |         | 200mmウエーバ | 300mmウエーバ   |  |

|             | 13×13mm | 160個      | 380個(2.4倍)  |  |

| チップサイズ      | 10×10mm | 280個      | 650個(2.3倍)  |  |

| 7 7 7 5 1 7 | 7×7mm   | 580個      | 1360個(2.3倍) |  |

|             | 4×4mm   | 1860個     | 4260個(2.3倍) |  |

ウェハの大口径化

# これを前工程プロセスで作る

トランジスタや配線層はシリコン基板表面上の数 μ mに作られる。

## LSIの断面模式図

# 前工程:トランジスタエ程

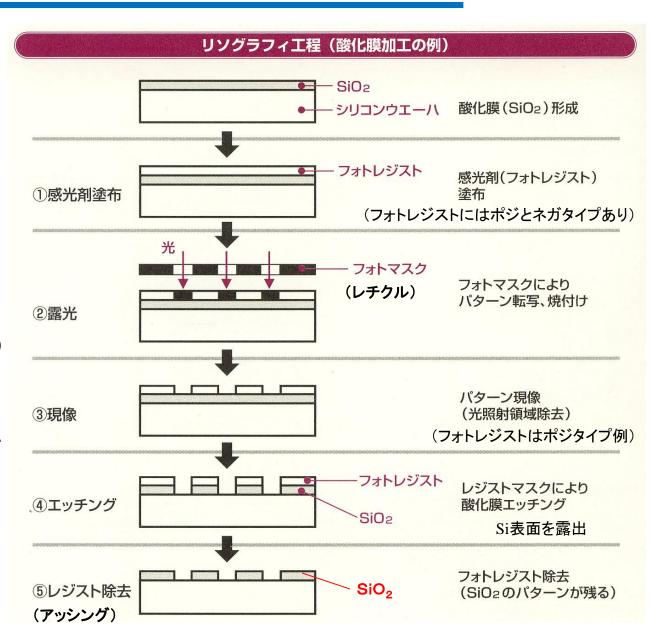

#### 写真の焼付/現像と同じ

#### 露光工程 vs 写真

・マスク:撮影済フィルム

・ウェハ: 印画紙

•レジスト: 感光剤

・露光:暗室での焼付け

▪現像:現像

に相当。

x4サイズの原版(フォトマスク)を用い、トランジスタのN層(またはP層)や配線層を作り込む部分のシリコン表面を露出させる。それ以外の部分は酸化膜(SiO2)により覆われている。

# 前工程:トランジスタエ程

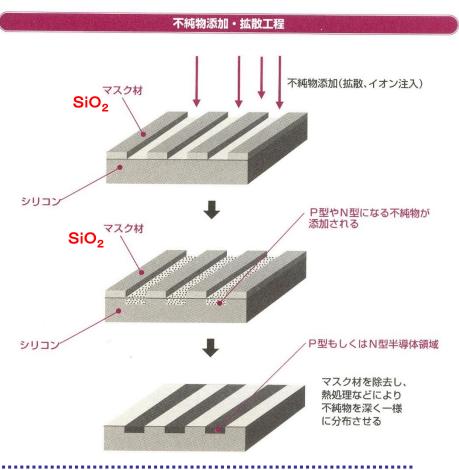

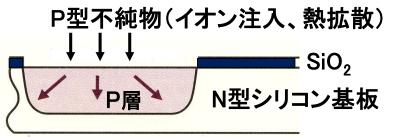

シリコン表面が露出した所に、 N層(またはP層)を作る不純物を 熱拡散やイオン注入にて 不純物添加する。

不純物は、シリコン露出した窓から内部に拡散浸透している。

拡散終わったら、マスク材(SiO<sub>2</sub>膜)を除去し洗浄する。

新たに膜付(酸化膜や金属膜)を 生成し、新たなフォトマスクにより露光 し、この不純物添加工程を繰り返す。

#### 不純物ソース例

N型: V属 リン(P), ヒ素(As)、

アンチモン(Sb)

P型: Ⅲ属 ボロン(B)

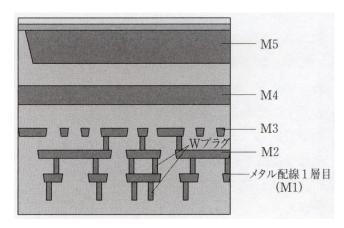

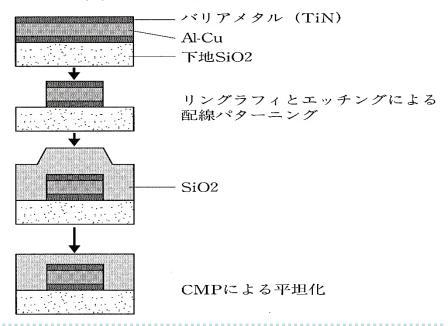

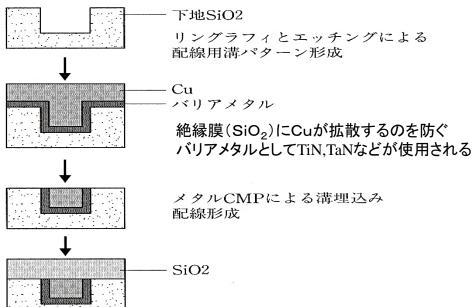

## 配線プロセス

メタル配線構造(メタル配線 5層例)

#### エッチング法(従来方法)

金属薄膜を形成してフォトリソグラフィとエッチングにて配線パターンを形成 ダマシン法

下地の絶縁膜中に"配線溝パターン"を 形成した後、全面に金属薄膜を付け、 CMP装置で表面を平坦に研磨する。 ダマシン法では、表面の平坦性確保と 高信頼性が得られる。

またCu(銅配線)加工に必須な技術。 Cuはエッチング加工が難しい材料の為。

#### (a)エッチング法

#### (b)ダマシン法

16

# ウェハ・プローブ試験

LSIテスタとプーバ装置を用い、チップに切り出す前のウェハ段階で 各LSIチップを試験し良否判定を行う。良品チップのみを次工程に流す。

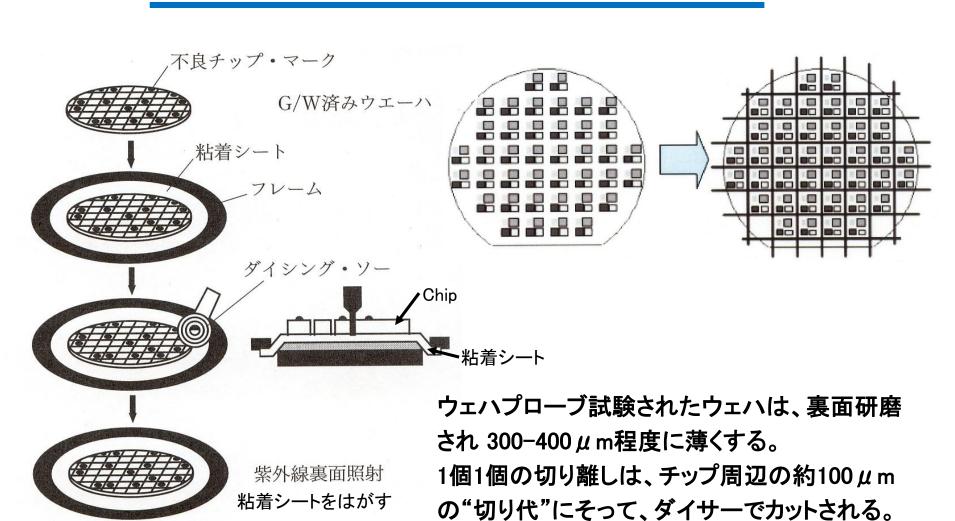

# ダイシング

そして良品チップのみをパッケージ化する。

ダイシング工程

18

紫外線

# 実装とボンディング

LSI上のパッドとパッケージ・リードフレーム間を AuまたはCu 細線でワイヤボンディング接続

図解半導体ガイド: 東芝 19

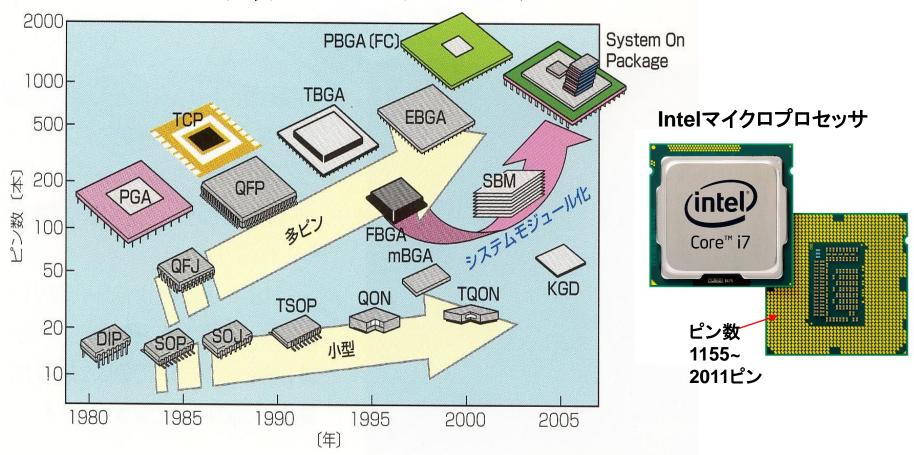

# パッケージ

#### パッケージ(実装)は小型化と多ピン化進展

#### ピン挿入型(DIP) から 表面実装型(QFP他)へ

図解半導体ガイド: 東芝

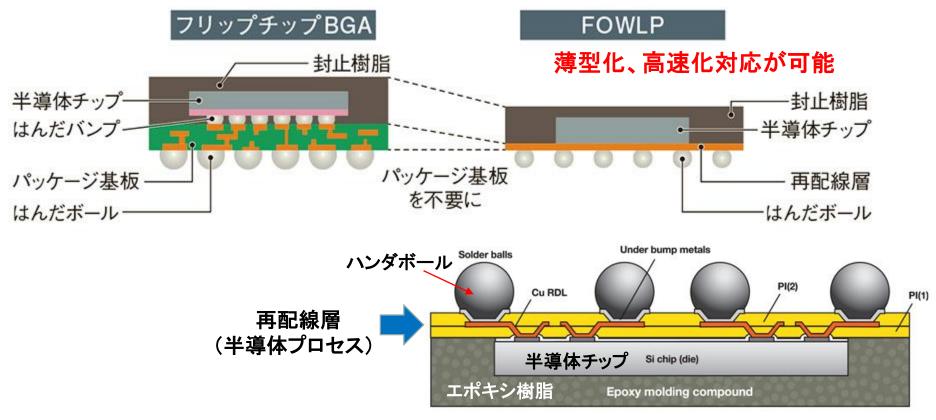

## **FOWLP** (Fan-out Wafer Level Package)

#### AppleがA10プロセッサで採用(iPhone7)

従来のフリップチップBGAに置き換わる実装方式として、「FOWLP」が注目を集めている。大きな違いはパッケージ基板がないこと。代わりにチップの端子から配線を引き出す再配線層を半導体工程で作り、外部端子につなげる。パッケージ基板がないため、「パッケージが薄い」、「配線長が短く伝送が速い」、「パッケージ基板の分、コストが安い」といった特性を実現できる

http://electronicdesign.com/boards/package-interconnects-can-make-or-break-performance

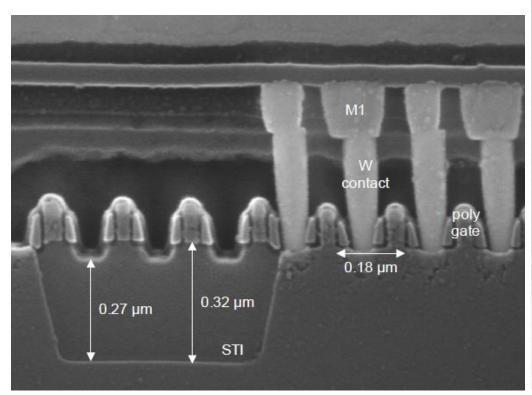

### 電子顕微鏡SEM断面写真に見る

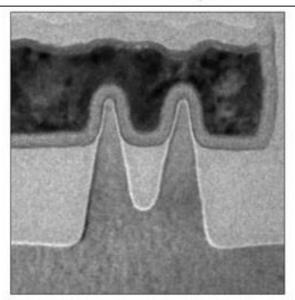

### 45nmSoC MOSトランジスタ: 歪シリコン技術

微細化したLSI断面は 非常に複雑な構造を示している。

32 nm minimum gate length MOSトランジスタ: 歪シリコン技術

トランジスタを囲うNiSi膜がチャネルに 歪を加え、移動度を向上

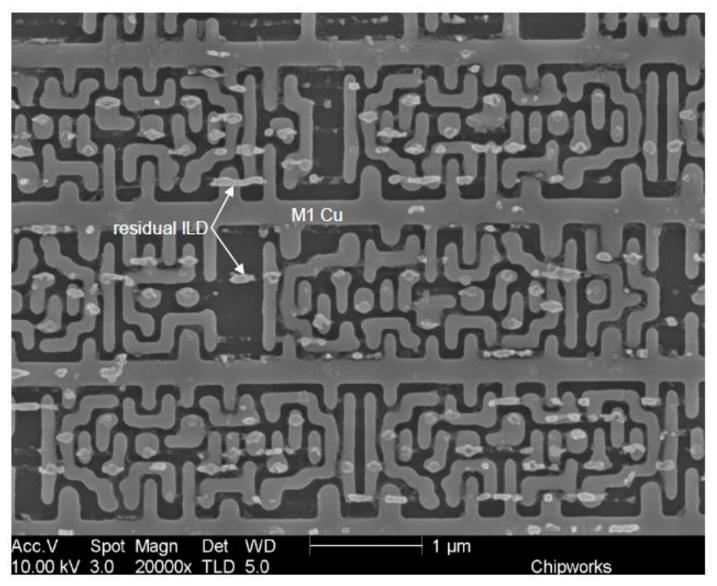

# 45nmSoC M1最下層配線層

Detail of Standard Logic Cells at Metal 1

M1層は密集が最も高い

## 45nmSoC 配線層

配線層も極めて複雑な構造をしている

## Intel 22nm/14nm FinFET

22nmプロセス

80 nm minimum pitch

14nmプロセス

52 nm (0.65x) minimum pitch

# FinFET transistor

配線層

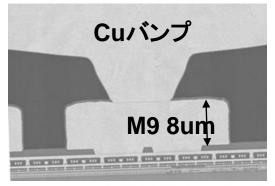

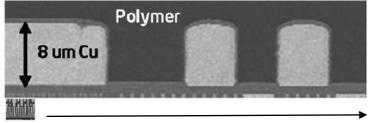

## Intel MPUの配線層構造

#### 32nm デザインルール

- ・メタル9層(M1~M9)銅配線

- ・メタル1~3層は、トランジスタピッチと同じ

- ・上層配線ピッチは密度と性能を最適化

- ・層間絶縁膜はlow-k ILD(低誘電率材料) low-k誘電材料はSiCN

- ・最上層のM9メタルは厚み<mark>8um</mark>の銅配線 電源およびI/Oルーティング用

| 321111 / J 1 3 / D |            |            |              |  |

|--------------------|------------|------------|--------------|--|

| Layer              | Pitch (nm) | Thick (nm) | Aspect Ratio |  |

| Isolation          | 140        | 200        |              |  |

| Contacted Gate     | 112.5      | 35         |              |  |

| Metal 1            | 112.5      | 95         | 1.7          |  |

| Metal 2            | 112.5      | 95         | 1.7          |  |

| Metal 3            | 112.5      | 95         | 1.7          |  |

| Metal 4            | 168.8      | 151        | 1.8          |  |

| Metal 5            | 225.0      | 204        | 1.8          |  |

| Metal 6            | 337.6      | 303        | 1.8          |  |

| Metal 7            | 450.1      | 388        | 1.7          |  |

| Metal 8            | 566.5      | 504        | 1.8          |  |

| Metal 9            | 19.4um     | 8um        | 1.5          |  |

厚いM9メタル層 (厚み8um)

Thick Top Metal - MT9

MT1-8

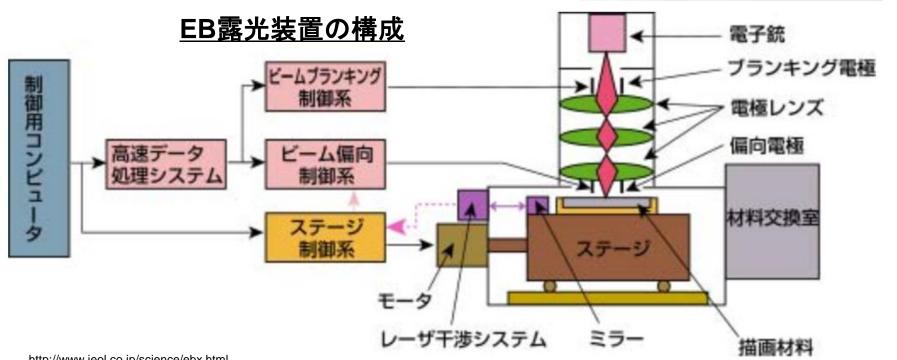

# マスク描画装置:EB露光装置

- ・EB(電子ビーム)露光装置は、電子銃で発生した 電子を高電圧(50K~100kV)で加速

- 精密な電子レンズ系とビーム偏向系 (電磁または電界偏向)で電子をX.Y軸に振り、ステージ 上のガラス基板塗布レジスト材にパターンを描画

- •nmオーダの極めて微細なパターン描画が可能。 ただし、スループットは極めて遅い

マスク描画装置(EB露光装置)

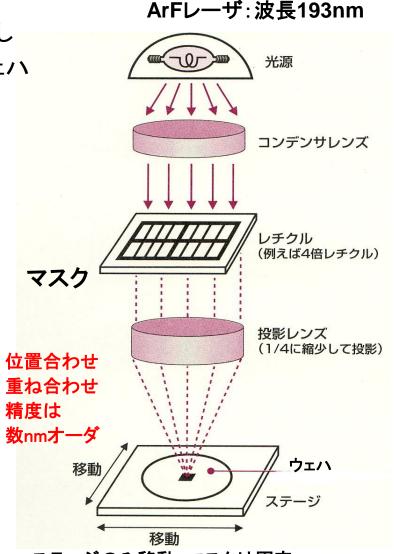

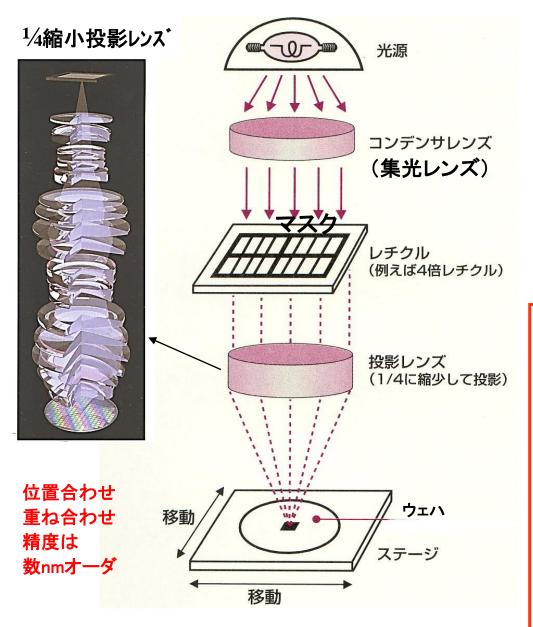

# 光露光(リソグラフィ)装置

4倍寸で描画されたマスク(原版)に、レーザ光を照射し 1//4の縮小投影レンズ系を介して、ステージ上のウェハ 上のレジスト材を露光。光学系やステージ系などの 位置あわせ精度はnmオーダと極めて精緻。 光学、機械およびエレクトロニクス、制御技術が 高度に融合した芸術品

ArF液浸露光装置(スキャナ) ASML TWINSCAN NXE:1950i

1台定価 50億円、平均実売価格 約40億円

・ステッパ:ウェハステージのみ移動、マスクは固定

•スキャナ:ウェハステージとマスクステージが同期して移動

処理速度:100ウェハ/時間以上と高速

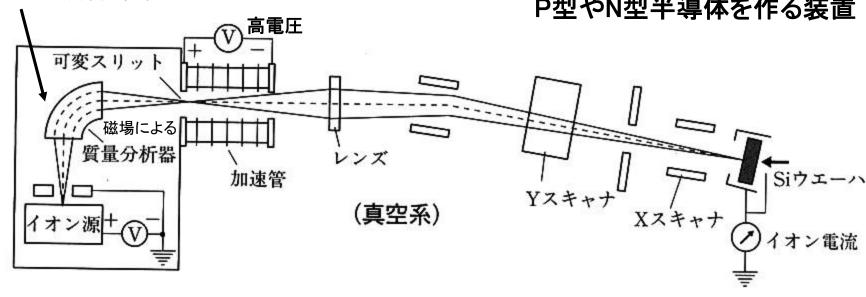

## イオン注入装置

荷電粒子(何価か)の質量に より曲がる角度が変わる

不純物を正確にシリコン基板に打ち込み、

P型やN型半導体を作る装置

導電型不純物と拡散用ソース (例)

| 導電型 | 導電型不純物    | 不純物ソース(常温での状態)                                                                           |  |

|-----|-----------|------------------------------------------------------------------------------------------|--|

| 3   | リン (P)    | POCl <sub>3</sub> (液体), PH <sub>3</sub> (気体)                                             |  |

| N型  | ヒ素 (As)   | As <sub>2</sub> O <sub>3</sub> (固体), AsH <sub>3</sub> (気体)                               |  |

|     | アンチモン(Sb) | Sb <sub>2</sub> O <sub>3</sub> (固体)                                                      |  |

| P型  | ポロン (B)   | BCl <sub>3</sub> (気体), B <sub>2</sub> H <sub>6</sub> (気体), BBr <sub>3</sub> (気体), BN(固体) |  |

\*固体や液体のソースでは、蒸発器や気化器を通し、ガス状態にして炉心管へ導入。

不純物用ソースガスをイオン化し 高電界(数KeV~MeV)で加速して ウェハ表面から打ち込む。 加速電圧とイオン電流を 制御する事ににより、 不純物濃度を正確に制御可能。

イオン注入装置での埋め込み深さ例:

50KeV 100keV

B(ボロン) 202nm 400nm

P(リン) 123nm 61nm

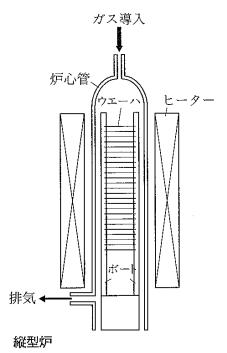

# 成膜装置

#### ウェハ上に各種金属薄膜や酸化膜(SiO<sub>2</sub>)などを成膜する装置

酸化炉

#### <u>熱酸化装置</u>

酸素ガスなどを供給し 800~1000度に加熱し シリコン表面を酸化させ 酸化膜(SiO2)を生成 (体積膨張伴う)

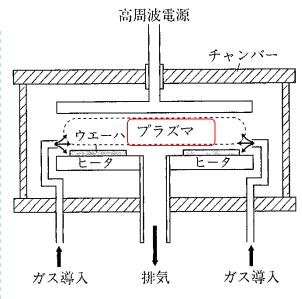

平行平板型プラズマ CVD 装置

#### CVD(化学的気相成長)装置

CVD:Chemical Vapor Deposition チャンバ内に膜材料となるガス を供給し、ガスにエネルギを 与え励起し、化学触媒(分離、 酸化、還元)反応を利用して ウェハ上に薄膜を堆積させる。

熱CVD:400~800℃

プラズマCVD:400℃以下

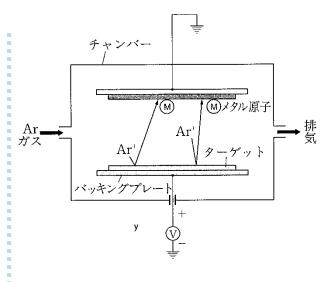

スパッタリング装置

#### スパッタリング装置(PVD装置)

ターゲット(材料金属)にアルゴン ガスを高速でぶつけ、叩き 出された金属がウェハ上に 付着して薄膜が生成される。 イオンエネルギーは1KeV程度。 金属: AI,W,Ti,Coなど

# エッチング装置

#### ウェハ上に生成した各種薄膜(酸化膜や金属膜)を一定形状に加工する装置

#### 代表的薬液

フッ酸 (HF)

希フッ酸 (DHF: HF+H<sub>2</sub>O)

バッファードフッ酸 (BHF:HF+NH4F)

熱リン酸 (H<sub>3</sub>PO<sub>4</sub>)

フッ酸+ヨード入り氷酢酸(CH<sub>3</sub>COOH(I<sub>2</sub>))

ウェットエッチング装置 薬液にてウェハ上の各種薄膜を 化学的にエッチングする。

<u>ドライエッチング装置</u>

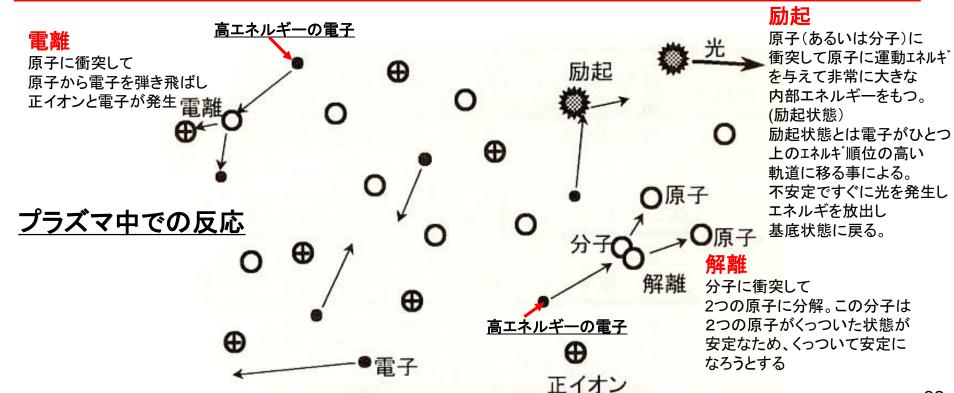

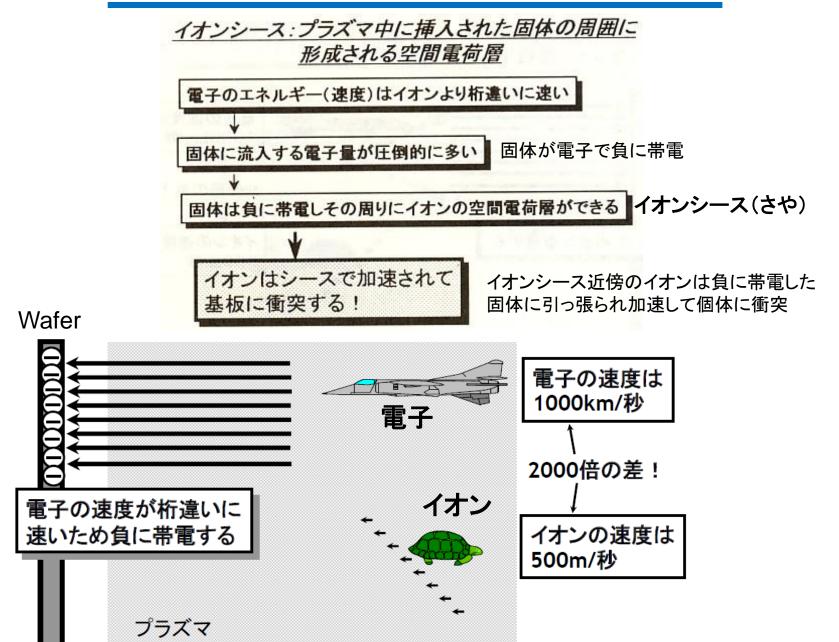

励起されたエッチングガスによりウェハ上の 薄膜を、物理的および化学的に反応させ 揮発性生成物化して排気ガスとして除去する。

#### RIE(反応性イオンエッチング)

エッチングガスがプラズマで分解活性化しウェハ表面に 反応。プラズマ中の電子がWafer電極にまづは飛び込む。 この負に帯電したWaferに(+)イオンが引き付けられ 加速され、この衝撃でエッチング反応が促進される

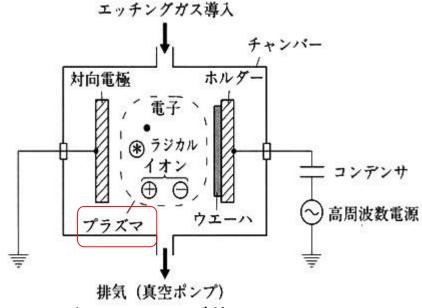

# プラズマとは

<u>自由に運動</u>する<u>プラスとマイナスの荷電粒子</u>が共存して 電気的中性になっている物質の状態

固体・液体・気体に次ぐ物質の第4の状態といわれることもある

正負の荷電粒子とは正イオンと電子が主。

電気的中性とはほぼ同数の正イオンと電子が存在すること。

# ドライエッチングのメカニズム

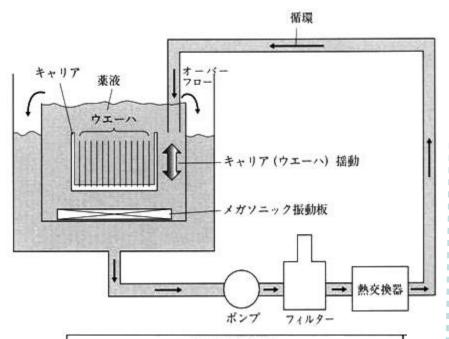

# 洗浄装置

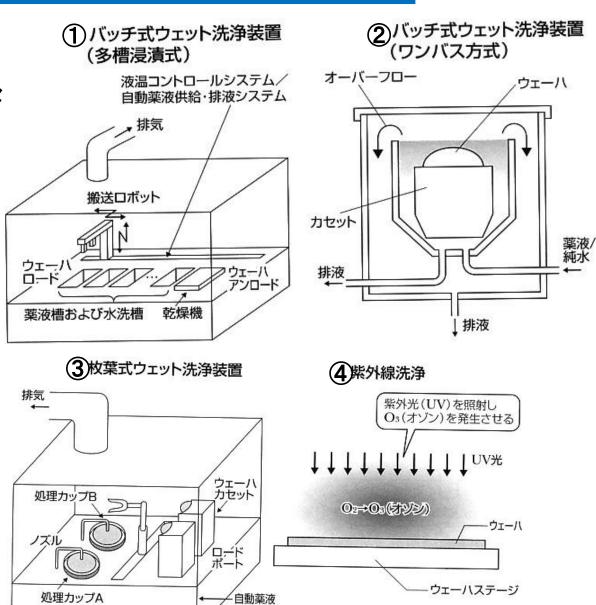

LSI製造では微小なパーティクル (ゴミ)や微量残留不純物が問題。このため汚染の可能性のあるプロセスから次のプロセスの間に必ず "洗浄"が必要となる。 洗浄にはウエット洗浄とドライ洗浄がある。

- ①洗浄効果の異なる複数の薬液槽に ウェハを順番に浸漬させて洗浄する。 (バッチ式ウェット洗浄)

- ②一つの薬液槽に複数の薬液を順次供給(ワンバス方式)

- ③一枚づつ洗浄する枚様式洗浄。 1~2つのカップで複数の薬液を処理 (枚葉式ウェット洗浄)

- ④ドライ洗浄として紫外線を照射して オゾンを発生させて有機物を 分解して揮発させる(紫外線洗浄)

供給回収システム

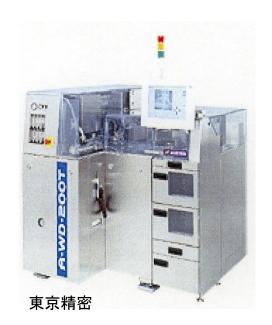

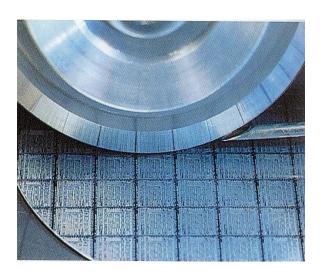

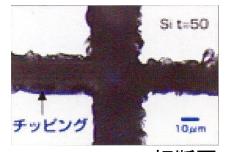

# ダイシング装置

切断面 **回転ブレードダイサ**

切断面 **レーザダイサ**

ダイシングは紫外線を照射すると変質する透明な高分子粘着 シートにウェハを貼り付け、シートをフレームに固定し、回転する ダイシングソーで格子状にフルカットする。

東京精密、ディスコHPより 35

# 試験装置

半導体メーカが製造する半導体は、全て半導体テストシステムで試験を行い、 良品のみが出荷される。

半導体テストシステムでは、測定対象のLSIが有する全ての機能および性能の試験が必要となる。

#### メモリテストシステム

- DRAM

- フラッシュメモリ などを試験

#### SOCテストシステム

- マイクロプロセッサ

- デジタル家電用SOC などを試験

#### アナログテストシステム

- AV用アナログLSI

- 車用アナログLSI

- CCD/CMOSイメージ・センサ などを試験

36

# 次世代半導体微細化で最もkeyとなる製造装置、 EUV露光技術動向

現在の光露光装置(ArF光源を使用した液浸露光装置)ではこれ以上に微細化対応は出来なくなっている。

波長13.5nmの**EUV**(Extreme ultraviolet極端紫外線)を用いる露光装置の完成が待たれている。

しかし、技術課題が大きく完成が大幅に遅れている。

### 光露光装置:透過光学系

光露光装置は 微細化(高解像度化)のため、 光源の波長を短くして来た。 波長436nmのg線>波長365nmのi線> 波長248nmのKrF>波長193nmのArF

さらに、投影レンズとウェハの間に 純水を入れ、屈折率を1.4倍高めて 解像度を高める「液浸」技術も搭載

#### 解像度決めるレイリーの式

NA= $n \sin \theta$

k:プロセス係数

n:媒質の屈折率

空気n = 1

水 n = 1.44

$\theta$ :ウェハへの光入射角

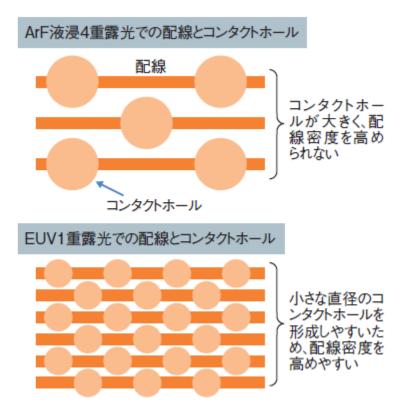

### EUVを使用すると露光工程が簡素化

#### 波長13.5nmEUV(Extreme ultraviolet極端紫外線)

- ・光露光でさらに微細化対応するには、多重露光(微細なマスクを分割して作成し、何度も露光し前工程プロセスをマスク数繰り返す)回数を増やす必要がある。しかしプロセス工数が増大する

- ・波長の短い13.5nmEUV露光装置使用できれば、プロセス工数は大幅削減可能

#### (a) EUV はプロセス工程数が大幅に少なく、TATが短い

#### 後 化学的機械研磨(CMP) ドライエッチング 用にの製造プロセスの工程 検査 露光 コーティングなど 成.膜 ウェットエッチング ハードマスク LE: Lithography-Etching SAQP : Self-Aligned Quadruple Patterning ArF液浸 ArF液浸 ArF液浸 **EUV** SAQP+2カット 3重露光(LE<sup>3</sup>) 4重露光(LE4) 1重露光

#### (b)EUVでは小さなコンタクトホールも作りやすい

日経エレクトロニクス2017.9 39

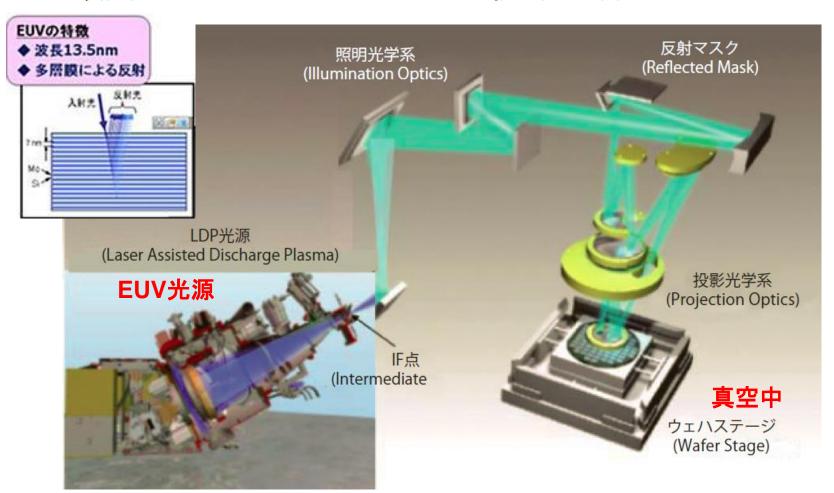

# EUV露光装置は反射光学系

- ・光源に波長13.5nmのEUV光を用いる露光装置

- ・光学系は反射光学系が必要(従来の露光装置は透過投影光学系)

- ・技術課題は極めて多い。特に大出力EUV光源技術開発が大幅遅れ

- •EUV装置開発はASMLのみ。NikonやCanonは技術開発凍結

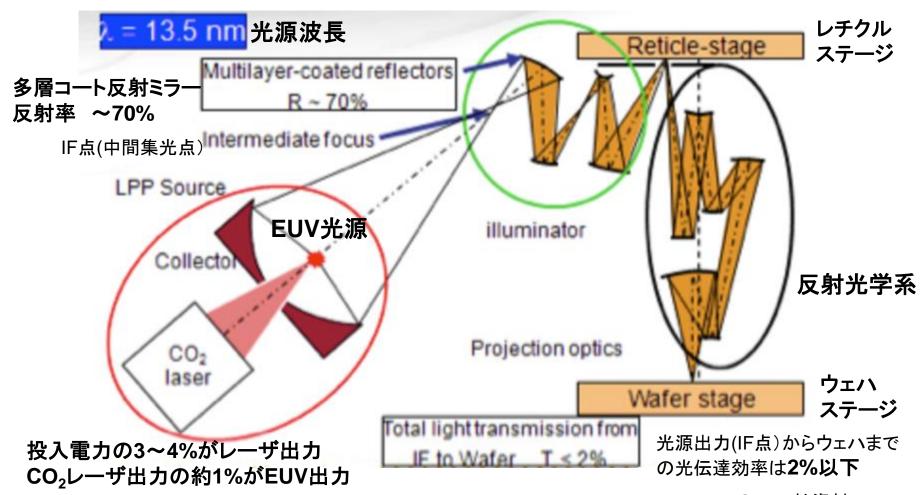

### EUV反射光学系

EUV用多層膜反射光学系では、1枚の反射率が70%以下。2枚で50%に低下。

このため6~8枚が限界。6枚でも光強度は1/10以下となってしまう。

中間集光点(IF)から、ウェハに至る光強度は2%以下まで低下。

投入電力からEUV出力までの多大なロス含めると、EUV露光装置は膨大な電力が必要。

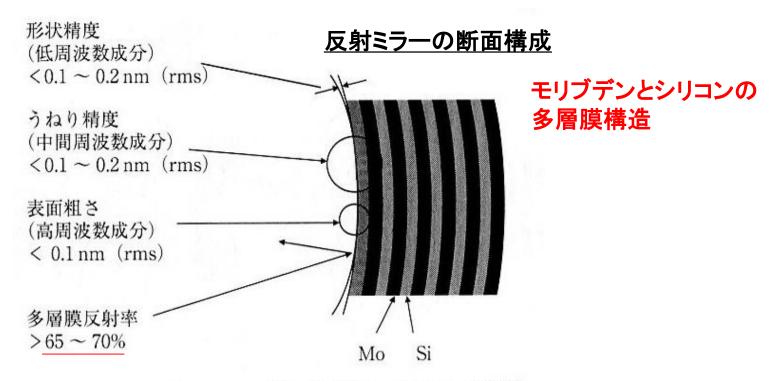

### EUV反射光学系:多層膜反射ミラー

非球面多層膜反射光学系の課題は、非球面反射光学系の精度

- ・光学系収差を支配する形状精度、フレアといったバックグランドの光強度うねり精度 (中間周波領域の精度)、反射率に関係する表面粗さ(高周波領域の精度) それぞれ0.05~0.15nm (rms)精度が必要

- ・可視光PDI(Point Diffraction Interferometer点回折干渉計)技術で 球面ミラー表面粗さ計測した時、測定再現性0.03nm(rms)、絶対測定精度0.08nm(rms)

- ・ミラーの研磨技術進化で0.05nm(rms)レベルのミラー加工も可能へ

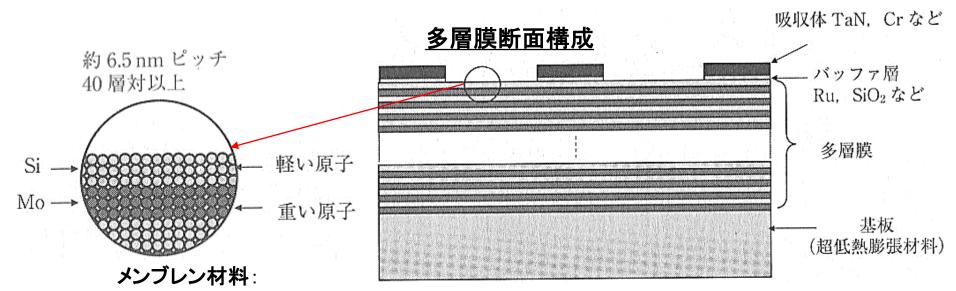

ピッチ:6.5 ~ 7 nm > 40 層対

# EUV多層膜マスク

- ・超低熱膨張基板上に、MoとSiを交互(各40層の計80層)に重ねた多層膜形成し、 その上にEUV光の吸収体

- ・吸収体(パターン)は、EUV光を強く吸収する材料が適している。Cr,W,Taが候補

- ・吸収体加工時、下地の多層膜にダメージ与えないようにバッファ層を挿入

- ・バッファ層として、SiO。やRuが提案。ASETでは吸収体にTaN、バッファ層にRu

- ・EUVマスクの最大の問題は、欠陥密度の低減。欠陥は多層膜、吸収体どちらも問題。 マスク面にある一定以上のおおきさの欠陥はウェハ面での欠陥となる。

- 多層膜マスクでは、僅かな段差が多層膜に生じても位相欠陥となる

X線照射耐性が重要。SiCやSiNを使用

#### レジスト材料:

EBやDUV光で使われている化学増幅型レジスト

マスク倍率x4 (将来的にはx8の見込み)

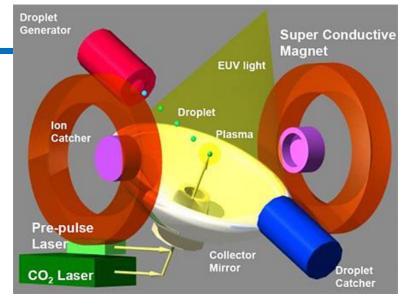

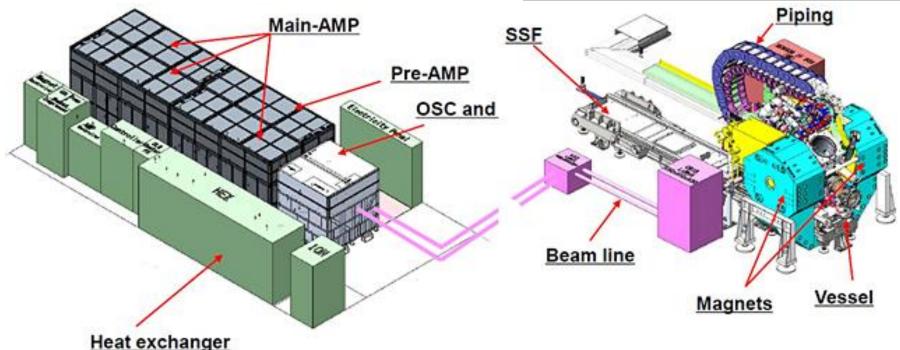

### EUV光源:LPP方式

#### **Laser Produced Plasma**

錫Snを滴下しそこに炭酸ガスレーザ光を照射すると、 Snがプラズマ化して電子が励起される。

電子が励起状態から定常状態に戻るときに

13.5nmのEUVが発生する。ただし効率は極めてひくい。

光源消費電力は1台で実に150KW!! 工場に10台装置おくと1.5MWの電力が必要

CO2レーザシステム部

EUV発光部

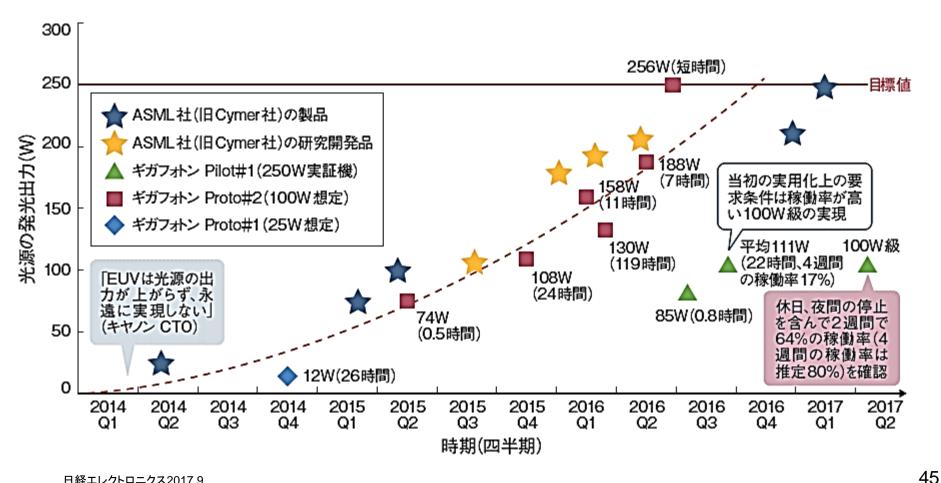

### 念願の光源出力が量産対応実用レベルに

最大の課題「光源の出力」がついに向上してきた。

100枚/h以上の量産に必須の100W光源出力の安定稼働が見えてきた。

短時間では200W~500W出力も得られるようになった。

ただし200W以上となると、光源の寿命問題のほか、反射光学系やマスクなどへのダメージが新たな 問題となってくるが、これらは未解決

## ASMLのEUV装置

#### NXE:3400B

#### 7-5nm node量産対応EUVシステム

-2017年から出荷開始

• 光源波長: 13.5nmEUV

· 光学系: NA=0.33 (Carl Zeiss SMT製)

•露光フィールド: 26 x 33mm

•解像度:13nm

• CDU:1.1nm

重ね合わせ:1.4nm(同一装置)

2nm (装置間)

・スループット:125枚以上

ASMLは2017年7月に、

1基当たり1億5000万ドルの EUVシステム(NXE3400B) 21基を受注と発表

ASMLはこれまでに累計1兆円を 超えるEUV開発投資を行ってきた。

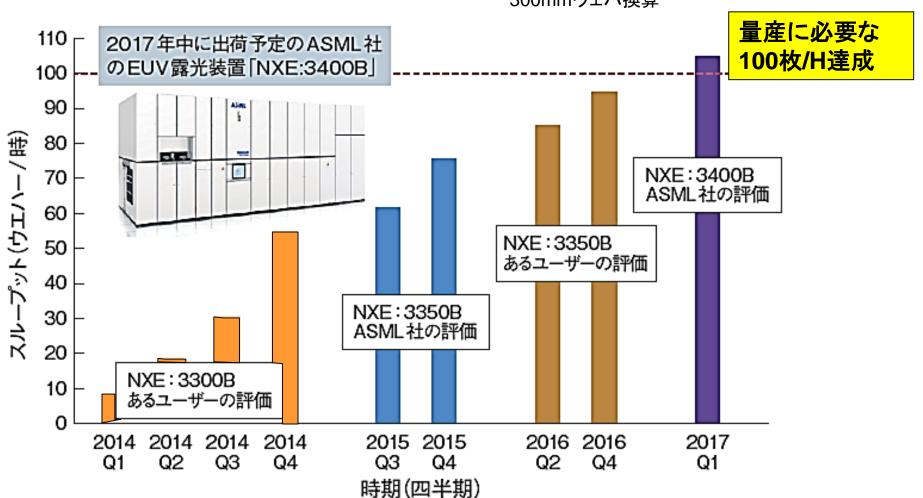

### EUVの生産性は3年で10倍超に向上

- ・ASMLは、量産用第1世代のEUV装置「NXE:3400B」を2017年に出荷 スループット125枚H、NA=0.33,最小加工寸法13nm,オーバーレイ精度3nm以下を実現

- •2024年ごろの量産を目指す次世代開発、0.5N.A.,スループット185枚/H、オーバーレイ精度2nm以下 300mmウェハ換算

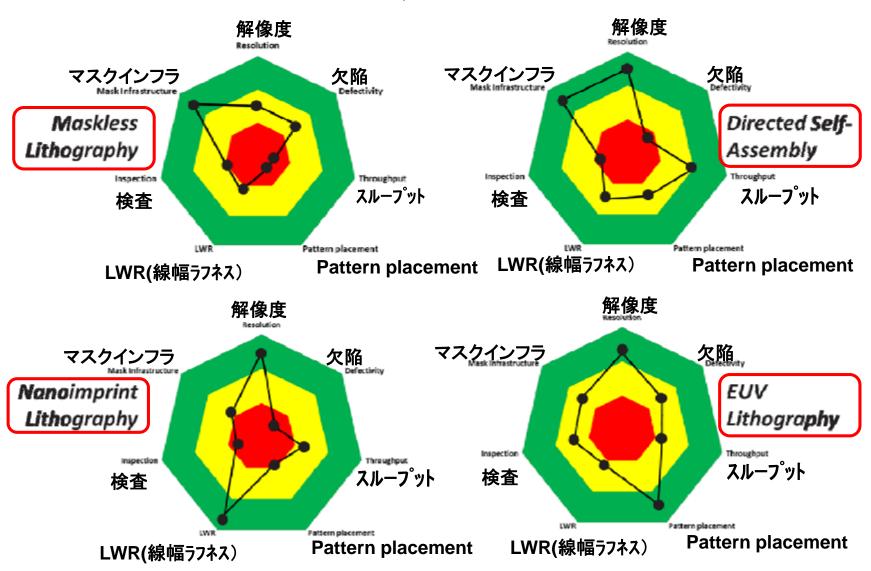

### ITRS2.0 2015 リソグラフィ候補技術の比較

各方式、メリットとデメリットがある。各装置の技術開発は難しい。

# 微細化コストは急上昇

- ・先端ファブ投資額: 45/40nm世代で約35億ドル、16/14nm世代では約50億ドルまで増加

- ・プロセス開発費も45/40nm世代で5億5000万ドルが、16/14nmでは18億ドルまで上昇

- ・先端ファブを有する半導体企業数は大幅減少。16/14nmは4社のみに減少 Intel,TSMC,Samsung,GF

SEMICON WEST 2016 Samsung 50

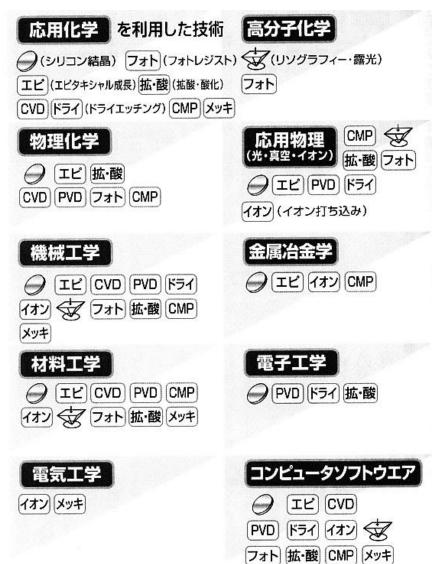

# 半導体は様々な先端技術の融合

1)半導体は多くの先端技術が結集した芸術産業

- 2)日本の半導体製造装置産業や、 素材材料産業は、 世界で優位性を確保している産業。

- 3)世界で勝つには技術だけでは駄目。 世界で勝てるビジネス戦略が重要

- •製品戦略

- •技術戦略

- マーケティング戦略

- •営業戦略

- •知的財産戦略

- •製造&流通(サプライチェーン)戦略など。

半導体なしては全産業が成り立たない。 半導体産業はグローバルな視点において 今後も重要な産業。

これが半導体の全貌だ: 泉谷著かんき出版

# Report: 受講学生皆さんへ

私の5回分それぞれの講義にたいして、下記内容でReportとして提出。 このReportが評点となります。手書きではなく、パソコン使用とします。

- 1)各回講義の目次毎の**項目で内容と結論**を簡潔にまとめる 講義スライド内容に追加情報を各自調査して加えれば更に良い。 結論は、各自考えや意見で記載すること。

- 2)各回ごとに**全体通しての意見と感想**、を必ず加える事。

5回分を纏めて下記へメール添付にて提出とします。提出締め切りは11月7日。

送付先メールアドレス: takayuki.nakatani1017@gmail.com