### 第325回群馬大学アナログ集積回路研究会

## MOSトランジスタの信頼性モデリング (集積回路設計における 信頼性シミュレーションの重要性)

群馬大学 客員教授 青木 均 2017年2月16日

## アウトライン

- 信頼性欠陥解析についての基礎的な原理

- バイアス温度不安定性(Bias Temperature Instability)のモデリング

- ホットキャリア注入(Hot Carrier Injection)効果のモデリング

- 信頼性回路シミュレーション

- 研究成果報告

半導体の信頼性解析

## 信頼性欠陥解析についての基礎的な 原理

## 概要

- 紹介

- 故障時間と加速要因

- 分布関数

- 信頼性評価項目

- 故障解析テクニック

## 紹介 信頼性と故障の解析(1)

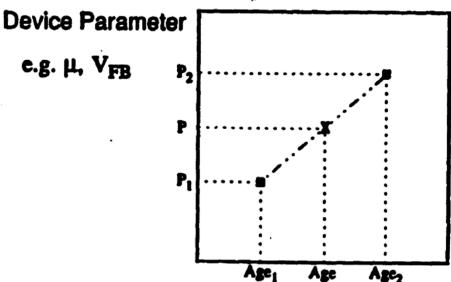

デバイスパラメータの劣化 (Device Parameters Degradation)

故障 (Failure)

例1) MOSFET

| デバイスパラメータ<br>仕様          | デバイス電流仕様                  | 回路動作     |

|--------------------------|---------------------------|----------|

| $V_{TH}$                 | I <sub>DS</sub>           | スペックアウト! |

| 温度、電圧ストレス                | $\Delta I_D$              |          |

| $V_{TH} + \Delta V_{TH}$ | $I_{DS}$ - $\Delta I_{D}$ |          |

## 紹介 信頼性と故障の解析(2)

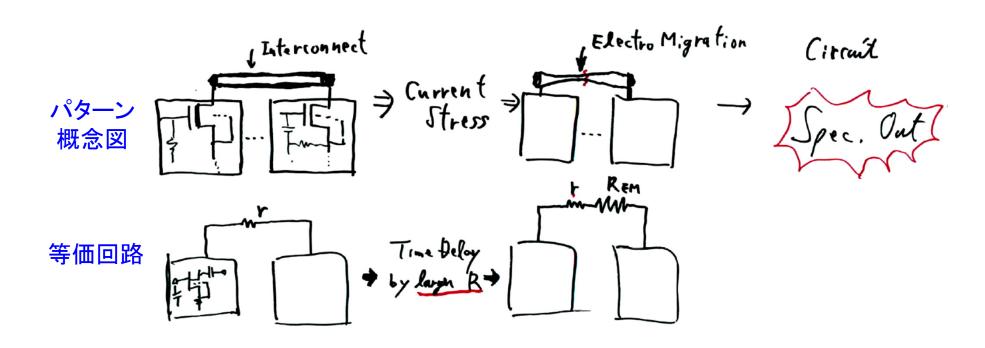

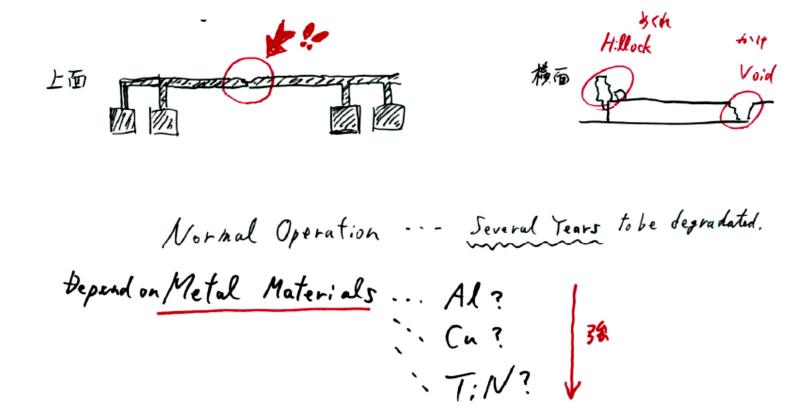

例2) 集積回路の内部配線(Interconnect)

## 故障時間と加速要因

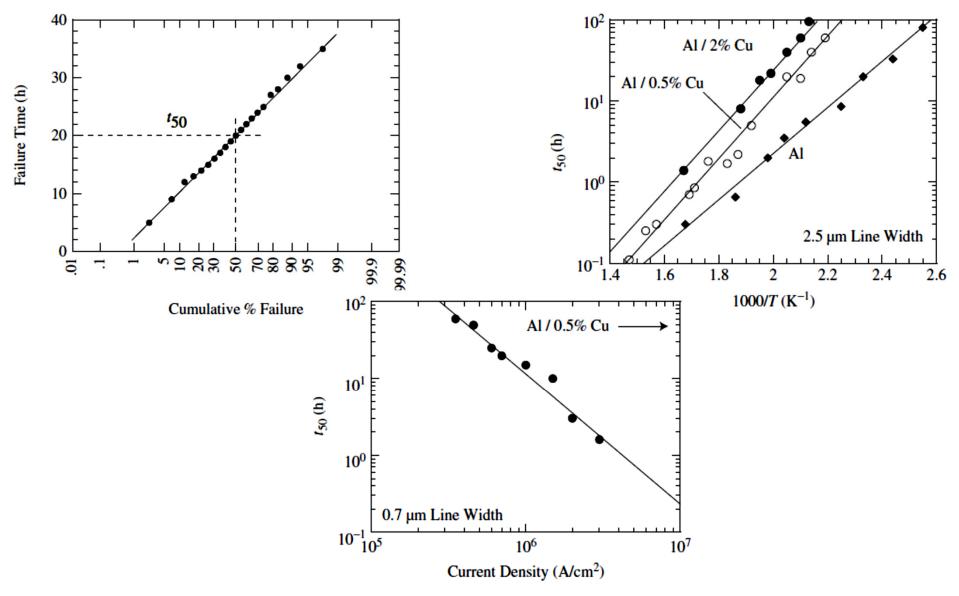

• 動作  $t_1$ ,  $t_2$ ,  $t_3$ ,...,  $t_n$  時間後に故障したとすると, 平均故障時間(Mean time to failure)は,

$$MTTF = \frac{t_1 + t_2 + t_3 + \dots t_n}{n}$$

- 中心故障時間(Median time to failure)は, t<sub>50</sub>で50%の製品が故障する時間.

- 故障から次の故障までの時間の平均を,

故障間平均時間(Mean time between failure)と呼び,

$$MTBF = \frac{(t_2 - t_1) + (t_3 - t_2) + \dots + (t_n - t_{n-1})}{n}$$

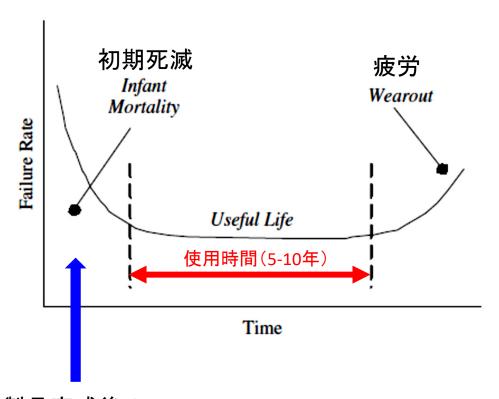

## バスタブ(風呂桶)カーブ

製品完成後の Burn-inテストで ある程度回避可能

## 加速要因

- 長時間信頼性試験 t = 104~106 sec

- 開発時間短縮には、WLR(Wafer Level Reliability) Stress Testが使用される

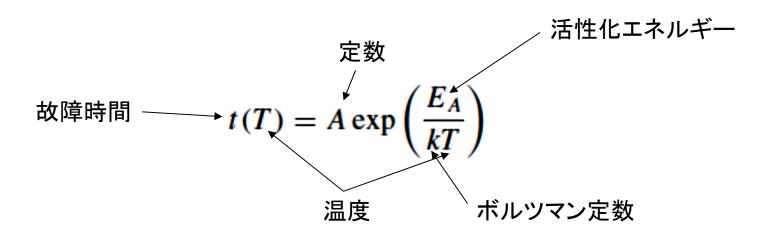

- ・ 熱活性化による原子の移動を考慮した、 Arrhenius方程式で特性表現される

## 加速要因方程式

#### 温度による加速要因

基準温度

$$AF_T = \frac{t(T_0)}{t(T_1)} = \frac{\exp(E_A/kT_0)}{\exp(E_A/kT_1)} = \exp\left(\frac{E_A}{k}\left(\frac{1}{T_0} - \frac{1}{T_1}\right)\right)$$

上昇温度

#### 電圧による加速要因

定数 電圧要因

$$t(V) = B \exp(-\gamma V)$$

基準電圧  $AF_V = \frac{t(V_0)}{t(V_1)} = \exp(\gamma(V_1 - V_0))$  上昇電圧

## 分布関数

故障比率 λ

$$\lambda = \frac{f(t)}{1 - F(t)}$$

確率密度関数 (Probability density function)

積算分布関数

(Cumulative distribution function)

- 信頼性関数 R(t)

- ightharpoonup 製品が時間tで故障しない確率 R(t) = 1 F(t)

$$R(t) = 1 - F(t)$$

$$F(t) \to 1$$

as  $t \to \infty$

確率密度関数 f(t)

$$f(t) = \frac{d}{dt}F(t)$$

積算分布関数 F(t)

$$F(t) = \int_0^t f(t) dt$$

## MTTF(平均故障時間)

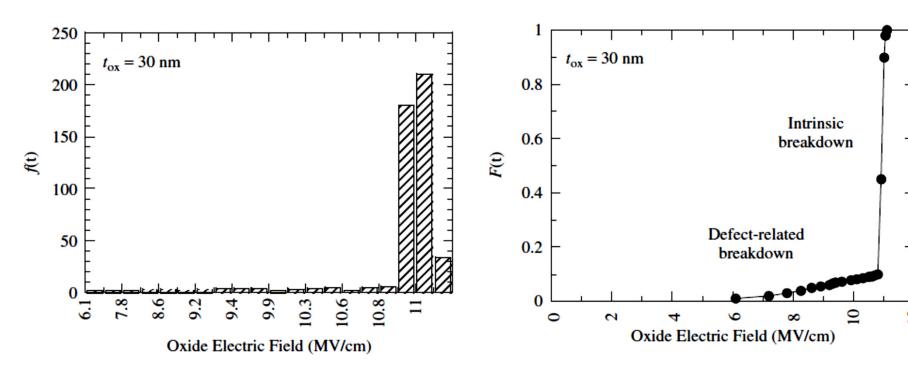

例) MOSの酸化膜破壊が起こるデバイス数

$$MTTF = \int_0^\infty t f(t) \, dt$$

## 信賴性評価項目

- 1. Electromigration (EM)

- 2. Hot Carriers

- 3. Gate Oxide Integrity (GOI)

- 4. Negative Bias Temperature Instability (NBTI)

- 5. その他の解析

## 1. Electromigration (EM)

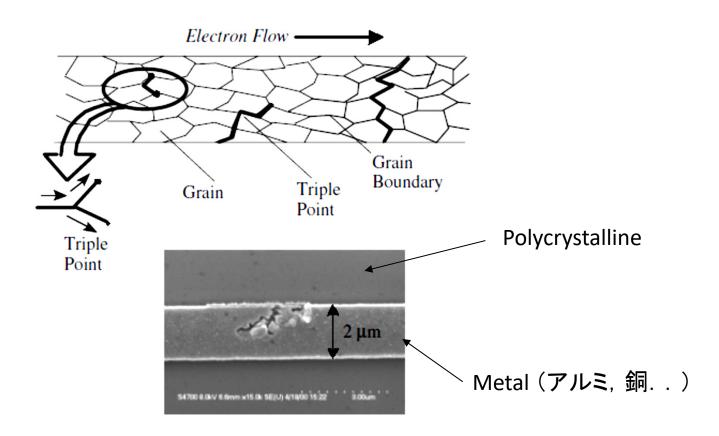

## EMの原因

Polycrystalline(多結晶): 故障=30時間 Single Crystalline(単結晶): 故障=26,000時間以上 (175°C, 2 × 10<sup>6</sup> A/cm<sup>2</sup>)

## EMの加速度試験条件

```

集積回路動作 - Normal (DC)

Temperature ... ~ 100°C

Line 電流電度 ··· < 5×10 A/cm2

Accelerated Test (DC)

Temperature ... 200°C

line 重流密度···/x/06A/22/

```

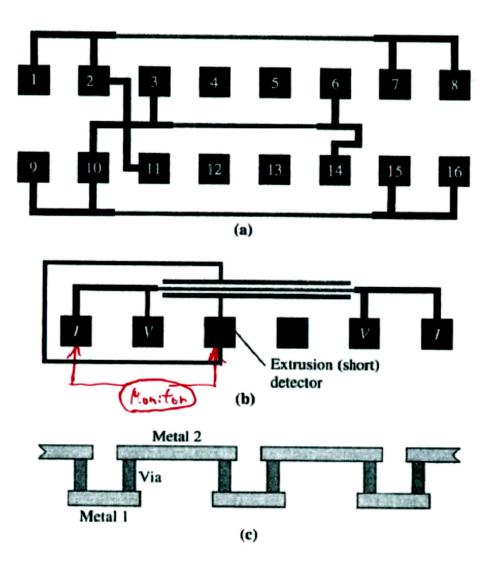

## EMの測定TEG

- · Constant DC-V PM.

- ・非常に多くろTEGも服して統計的以解析は3.

- \*一つの電圧役をりして\* 切りが入り測定

## Blackの理論

$$t_{50} = \frac{Ae^{E_a/kT}}{J^n}$$

$$\frac{t_{50}(T_1)}{t_{50}(T_2)} = \exp\left[\frac{E_A}{k} \left(\frac{1}{T_1} - \frac{1}{T_2}\right)\right]; \frac{t_{50}(J_1)}{t_{50}(J_2)} = \left(\frac{J_2}{J_1}\right)^n$$

# テスト結果

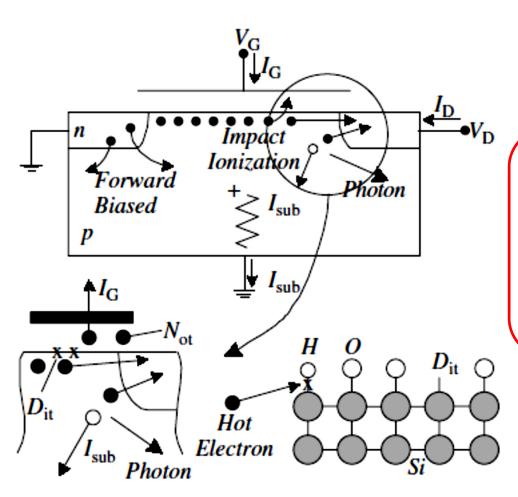

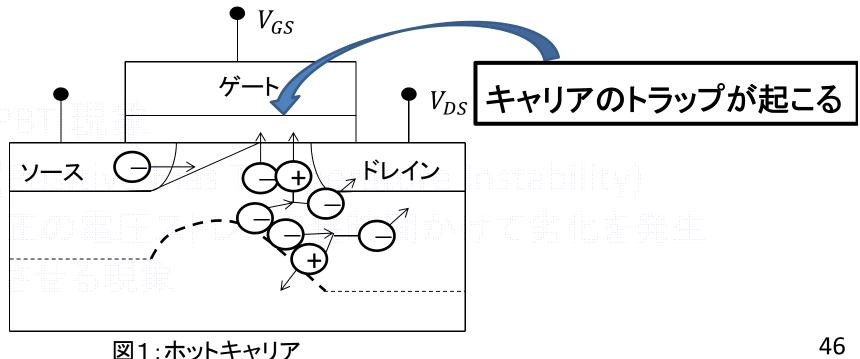

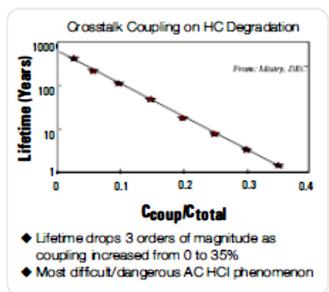

### 2. Hot Carriers

高電界下において電子・ホールはエネルギーを得て、何割かは酸化膜に注入される

これが酸化膜トラップ電荷とな

一部ドリフトによりゲート電流と

一部インターフェース・トラップ を生成する

または光子を発生する

なる

\* 例えば室温300Kでは, *E=kT*によって, エネルギーは約25mV. *T*=12,000Kでは, *E*=1eVになる

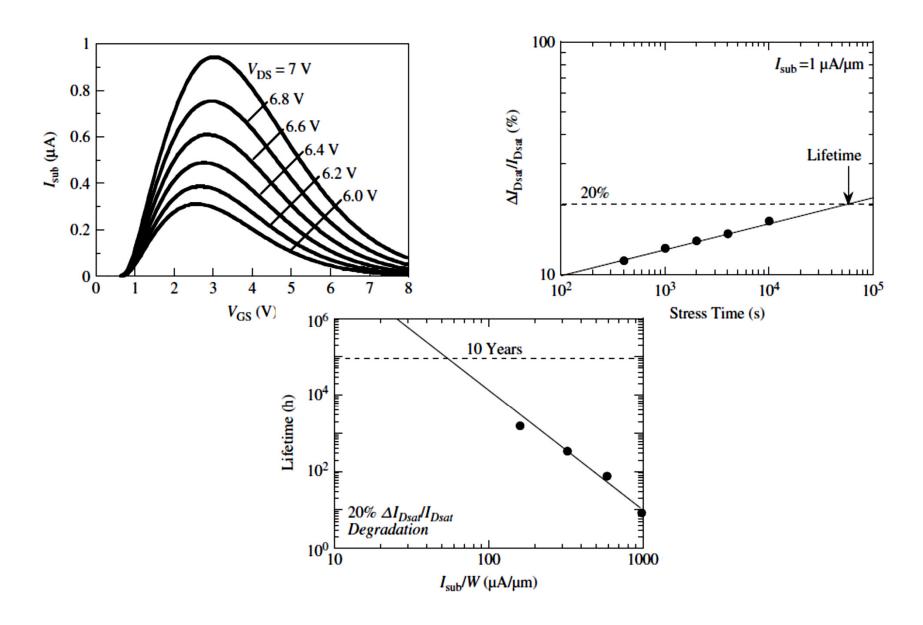

## N-channel MOSFETの Hot carrier測定法

- ・ サブストレート電流I<sub>sub</sub>が最大になるようにV<sub>GB</sub>を かける

- 」」はチャネル横方向の電界の大きさに依存す

- 低V<sub>GS</sub>, V<sub>DS</sub>が飽和領域においては、横方向電界が、V<sub>GS</sub> ≈ V<sub>D</sub>/3-V<sub>D</sub>/2まで増加する

- ・高V<sub>GS</sub>においては、デバイスは線形領域になり、 横方向電界は減少し、I<sub>sub</sub>も低下する

- Isubを一定時間かけ続け、ドレイン電流、しきい値電圧、移動度、トランスコンダクタンス、インターフェース・トラップ密度を測定する

# 測定例

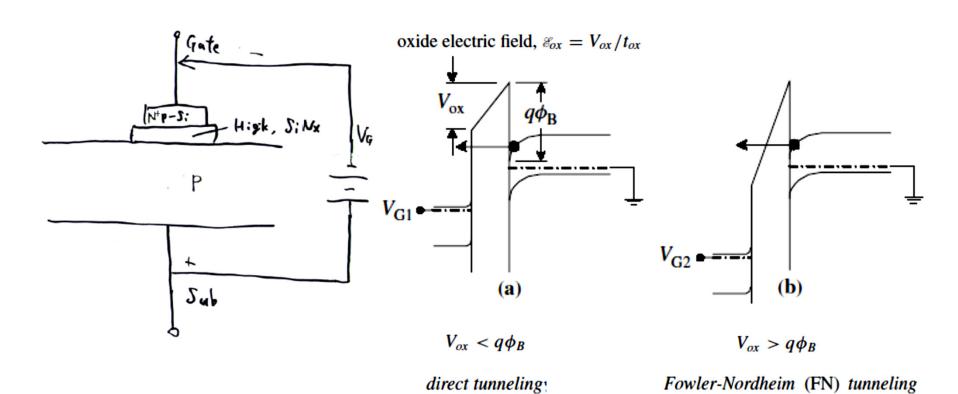

## 3. Gate Oxide Integrity (GOI)

- MOSのゲート絶縁酸化膜は、MOSFETで最も 重要な要素パラメータ

- SiO<sub>2</sub>の抵抗率は10<sup>15</sup> Ω•cm

- ゲート酸化膜電界が3×10<sup>6</sup> V/cmまでは,

ゲートリーク電流は微少で無視できる

- さらに高電界になると、ゲートリーク電流が急 激に増加する

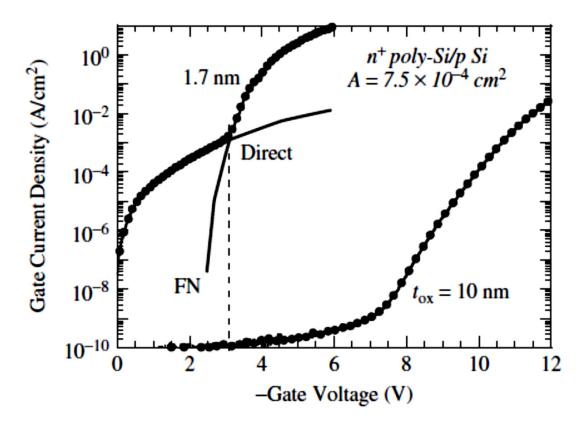

## トンネル電流

- 酸化膜圧が4-5nm以上では、FNトンネル電流が支配的

- 酸化膜圧が3.5nm以下では、ダイレクト・トンネル電流が支配的

## トンネル電流式と測定結果

$$J_{dir} = \frac{AV_G}{t_{ox}^2} \frac{kT}{q} C \exp\left(-\frac{B(1 - (1 - qV_{ox}/\Phi_B)^{1.5})}{\mathscr{E}_{ox}}\right)$$

$$J_{FN} = A \mathcal{E}_{ox}^2 \exp\left(-\frac{B}{\varepsilon_{ox}}\right)$$

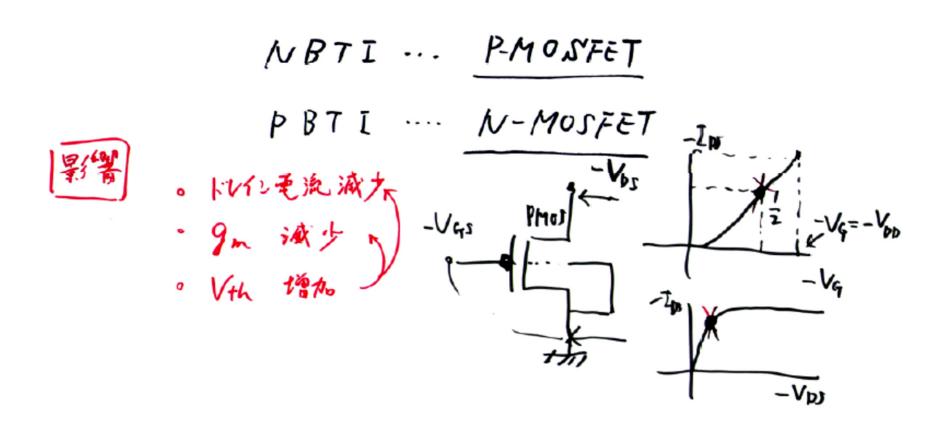

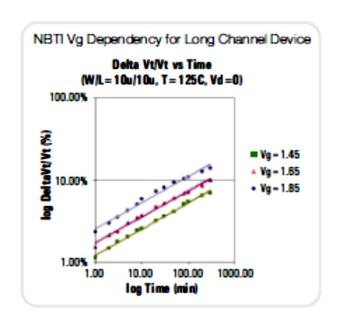

# 4. Negative Bias Temperature Instability (NBTI)

- 高温状態で、MOSFETのゲート電圧が負にバイアスされて起きるので、Pch-MOSFETで発生

- しきい値電圧増加→ドレイン電流, 伝達コンダクタンス低下

- 加速条件:温度=100~250℃,酸化膜電界=6 MV/cm以下

- ゲートに正電圧の場合: P(Positive) BTIであり、 Nch-MOSFETで発生

## 測定条件(アクティブバイアス状態)

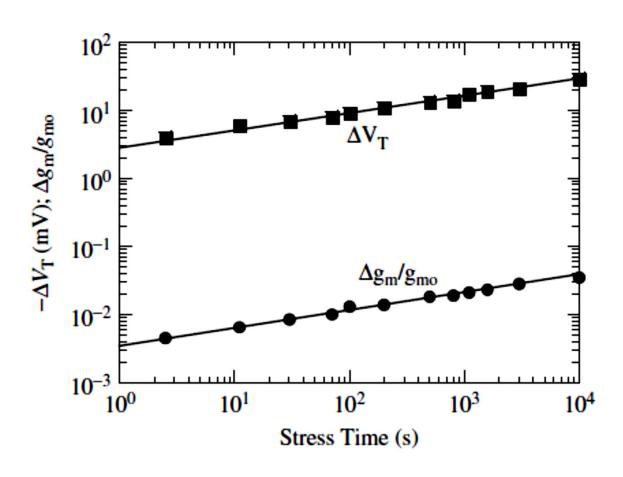

## 測定結果例

## 5. その他の解析

- Stress Induced Leakage Current (SILC)

- 低い逆バイアス時に起きる酸化膜のリーク電流で、膜厚5nm以下では減少

- Electrostatic Discharge (ESD)-静電気放電

- 人体および機器の充放電による故障解析

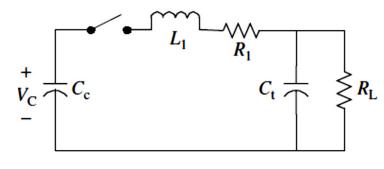

人体の等価回路モデル

半導体の信頼性モデリング

# バイアス温度不安定性(BIAS TEMPERATURE INSTABILITY)のモデリング

### BTI

#### NBTI

- PチャネルMOSFETにおける、最も重要な信頼性要因

- ゲートにかかるバイアス電圧が負

#### PBTI

- NチャネルMOSFETにおいて、近年のナノメータ 技術によって重要となってきた信頼性要因

- ゲートにかかるバイアス電圧が正

## NBTIの代表的モデル

- 反応・拡散 (Reaction-Diffusion) モデル

- 最も一般的な理論・モデル

- ・ホール・トラッピング・モデル

- 時間に依存した復活(Recovery)モデル

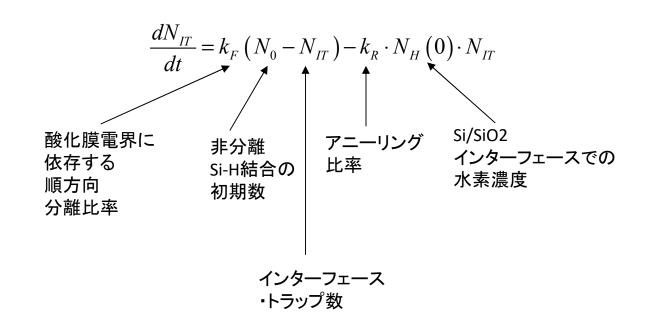

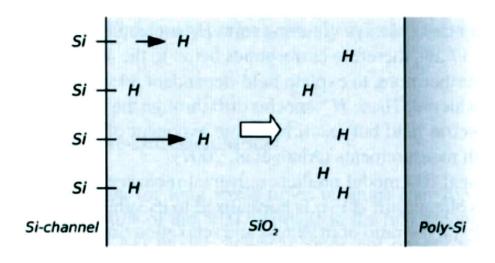

## 反応・拡散 (Reaction-Diffusion) モデル

- Si/SiO2におけるSi-HとSi-Oの結合が、ホールにより壊れることで、NBTIがおこる

- ・この電気化学的な反応は電界、温度に依存しており、 トラップの発生(Reaction)比率は以下の式で表せる

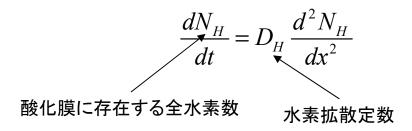

## 拡散プロセス

$$N_{IT} \ll N_0 \sim 5 \times 10^{12} \, cm^{-2}$$

$$\frac{dN_{IT}}{dt} = k_F \left( N_0 - N_{IT} \right) - k_R \cdot N_H \left( 0 \right) \cdot N_{IT}$$

初期のインターフェース・トラップ発生率は、非常に遅いので

$$\frac{dN_{IT}}{dt} \approx 0$$

とおける。すると上式は、  $N_H(0) \cdot N_{IT} \approx \frac{k_F}{k_R} N_0$

拡散が起こる点での水素原子の数は、

$$x_{DF}(t) = \sqrt{D_H \cdot t}$$

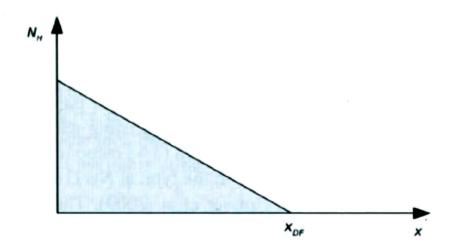

# 発生したインターフェース・トラップと拡散水素原子

## しきい値電圧劣化

発生するインターフェース・トラップの数は、水素原子の拡散数と等しいので、

$$N_{IT} = \int_{0}^{\sqrt{D_H \cdot t}} N_H(x, t) dx = \frac{1}{2} N_H(0) \sqrt{D_H \cdot t} \qquad \stackrel{N_H(0) I = \text{代入}}{\longrightarrow} \qquad N_H(0) \cdot N_{IT} \approx \frac{k_F}{k_R} N_0$$

$$N_{IT} = \left(\frac{k_F}{k_R} \cdot \frac{N_0}{2}\right)^{\frac{1}{2}} \left(D_H \cdot t\right)^{\frac{1}{4}}$$

と求まる.

しきい値電圧の劣化△V<sub>TH</sub>は,

$$\Delta V_{TH} = \frac{q \cdot N_{IT}}{C_{or}}$$

なので、上記を代入して求まる.

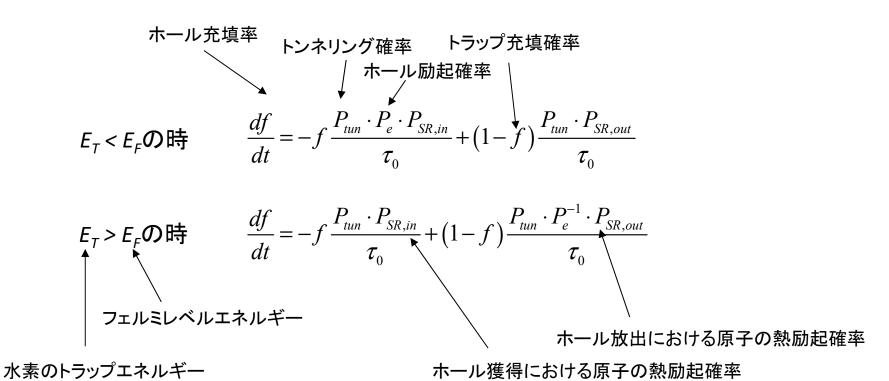

### ホール・トラッピング・モデル

- RDモデルや、それを発展させたモデルでは、 時間に依存した復活効果が説明できない

- ホール・トラッピングは、非常に長い時間における温度依存効果や、ストレスと復活を考慮していない

- そこでインターフェース・ステートと熱による活性化を合わせた解析を行った

## lelminiのホール・トラップ・モデル

- 問題は、このモデルは実測結果と結びついていない。

- コンパクトモデルは、現時点で開発途上にある。

#### PBTIの代表的モデル

- ナノメータMOSFET(45 nm以下)で顕著になってきたため,近年研究され始めた

- IBM T. J. Watson Research Centerの研究がシンプルで、ゲート絶縁膜内、電子のトラップ・デトラップによる、しきい値電圧の増加を表現

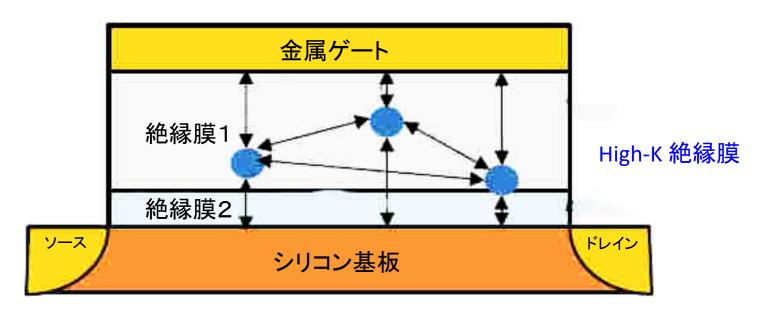

## トラップ・デトラップ

電荷のトラップ・デトラップ

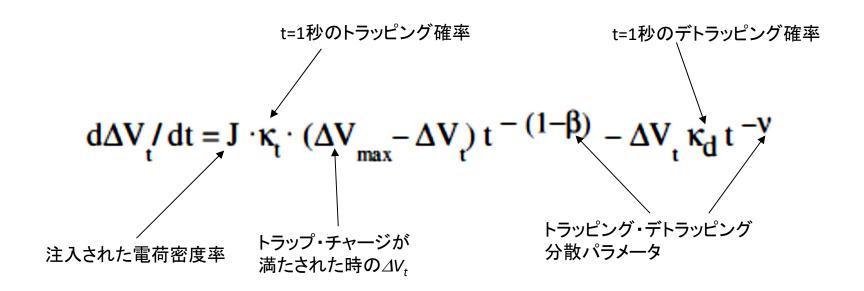

## PBTI トラップ・デトラップモデル

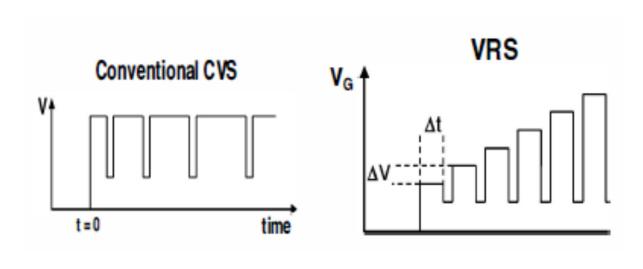

## 測定方法

**Constant Voltage Stress**

**Voltage Ramp Stress**

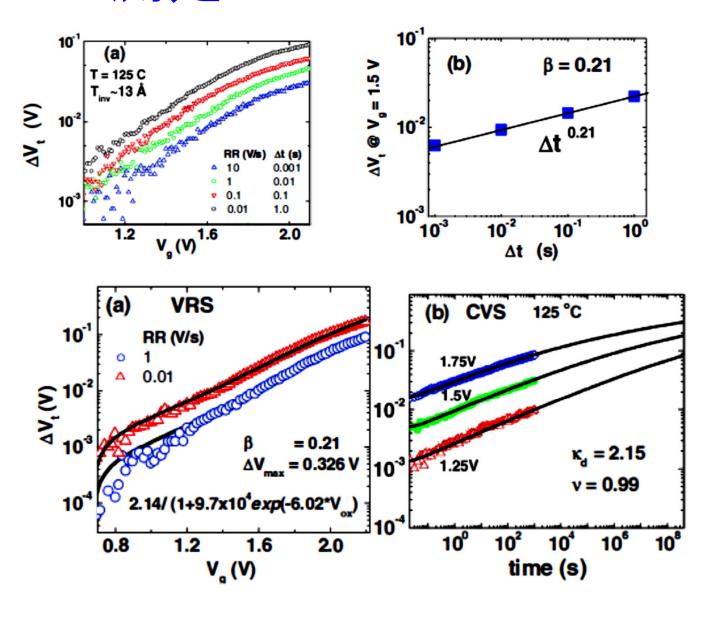

## 測定とシミュレーション

半導体の信頼性モデリング

## ホットキャリア注入(HOT CARRIER INJECTION)効果のモデリング

#### N-MOSFETの劣化現象

HCI現象

(Hot Carrier Injection)

高電界領域で電界加速により チャネルが大きなエネルギーを得ることで 移動度劣化、しきい値電圧の上昇が起こる現象

> より支配的であるHCI現象に着目し 特性解析を行う.

• PBTI現象

(Positive Bias Temperature Instability)

正の電圧ストレスを長時間かけて しきい値電圧が上昇する現象

#### N-MOSFETの劣化現象

HCI現象

(Hot Carrier Injection)

高電界領域で電界加速により

チャネルが大きなエネルギーを得ることで

移動度劣化、しきい値電圧の上昇が起こる現象

#### HCI現象のモデル

カルフォルニア大学バークレー校の Hu教授により導入された BErkeley Reliability Tools (BERT)のモデル

> Interface Trap Number を 算出 キャリアの移動度についても導出している

SPICE上でシミュレートするのに適している

劣化前のDCパラメータを取り込み シミュレーション上で劣化DC特性を予想する

#### 基本とするモデル

BERTのモデルをBSIM4に使えるように 2004年にKufluogluとAlamによって開発された RDモデル(Reaction-Diffusion model)を基に開発する

> ドレイン近傍で発生する ホットキャリア効果のモデル化が可能

水素拡散粒子の生成を方程式で 表しているので劣化を単純化できる

#### RDモデルの復習(NBTIでも使用)

#### 界面トラップ数

$$N_{H(0)}N_{it} \approx \frac{k_F}{k_R}N_0 \qquad (1)$$

$$N_{H(0)}$$

界面における水素濃度の初期値

$N_{it}$  界面トラップ数

k<sub>F</sub> 酸化物電界依存フォワード解離速度定数

k。 アニーリング速度定数

No Si-H結合の初期値

#### チャネル/酸化膜界面での水素反応式

$$N_{H_x} = k_H N_H^{n_x} \tag{2}$$

N<sub>H</sub> 体積あたりの水素粒子の濃度

$k_H$  反応定数

n<sub>x</sub> 水素粒子あたりの水素原子数

#### Si-H結合の数より界面トラップ数を算出可能

$$N_{it} = \frac{\pi W}{2A_{tot}} n_{\chi} \int_{0}^{\sqrt{D_{H_{\chi}t}}} \left( N_{H_{\chi}(0)} \left[ r - \frac{r^2}{\sqrt{D_{H_{\chi}t}}} \right] \right) dr$$

$$=N_{H_{\chi}(0)}\frac{\pi n_{\chi}}{12L}D_{H_{\chi}t}$$

(3)

$$D_{H_xt}$$

$N_H$ の密度

A<sub>tot</sub> ゲート下の総面積 L MOSFETの長さ

W MOSFETの幅

#### RDモデル→DC HCIモデル

(1),(2),(3)式を組み合わせると(4)式になる

$$N_{it} = \left(\frac{k_F N_0}{k_R}\right)^{\frac{n_\chi}{1+n_\chi}} \left(\frac{n_\chi \pi k_H}{12L} D_H\right)^{\frac{1}{1+n_\chi}} * t^{\frac{1}{1+n_\chi}}$$

(4)

界面トラップによる電圧依存特性は しきい値特性カーブのずれで表す

$$\Delta V_{th_{DEGRADATION}} =$$

$$egin{aligned} C_{HCI} \left(rac{k_F N_0}{k_R}

ight)^{rac{n_\chi}{1+n_\chi}} \left(rac{n_\chi \pi k_H}{12L} D_H

ight)^{rac{1}{1+n_\chi}} * egin{aligned} rac{1}{1+n_\chi} & 1 \end{aligned} \end{aligned}$$

(5)  $D_H \quad \text{水素原子の密度} \ t \quad \text{時間} \ C_{HCI} \quad 技術依存なパラメータ \end{aligned}$

半導体の信頼性シミュレーション

### 信頼性回路シミュレーション

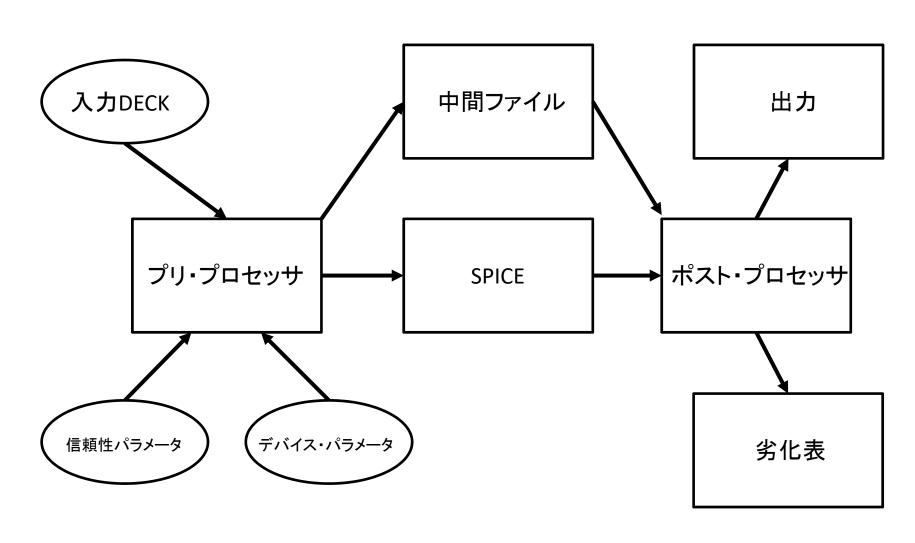

# 信頼性回路シミュレーションプログラム

- Berkeley Reliability Tools (BERT) --- 1991年

- Menta Graphics社ELDO --- 2012年

- RelXpert (ProPlus Inc.) --- 2012年

- その他は同様

#### BERTの機能

- 1. Circuit Aging Simulator (CAS)により、Hot Carrier Degradationをシミュレート

- 2. Circuit Oxide Reliability Simulator (CORS)により, 時間依存誘電破壊をシミュレート

- 3. Electromigration (EM) moduleで、EMをシミュレート

- 4. Bipolar Circuit Aging Simulator (BiCAS)により、 バイポーラ・トランジスタのHot Carrier Degradationをシミュレート

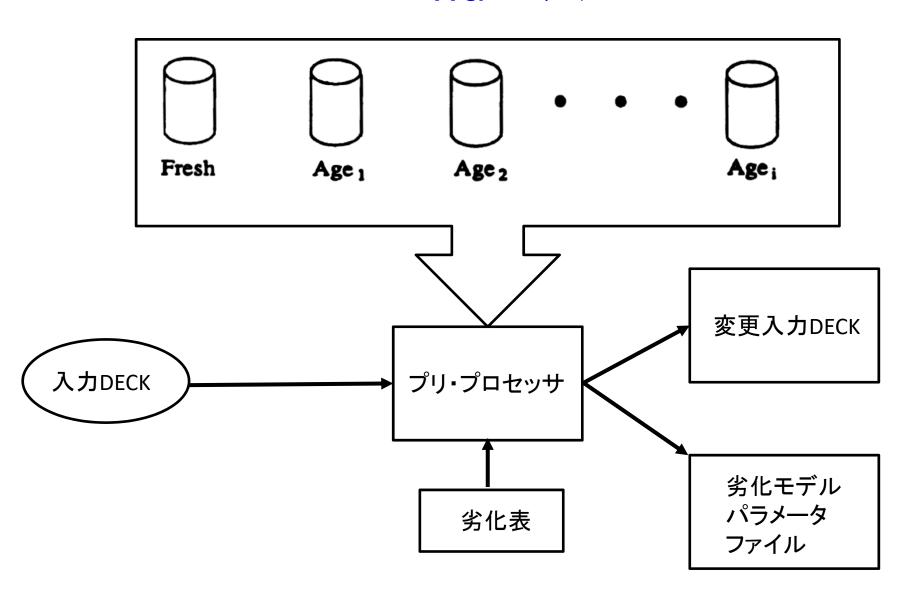

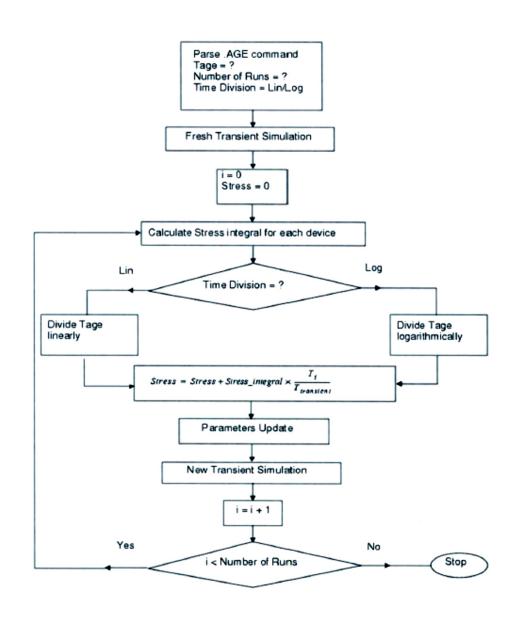

#### Berkeley Reliability Tools (BERT) 1stパス

# Berkeley Reliability Tools (BERT) 2ndパス

## CASによるNch MOSFETの 劣化モデリング

#### Stressed Parameter Sets

Lucky Electron Model使用

$$AGE = \int_{0}^{T_{stress}} \frac{I_{DS}}{W \cdot H_{HCI}} \left(\frac{I_{sub}}{I_{DS}}\right)^{m_{HCI}} dt$$

$$\Delta V_{TH} = f(AGE)$$

フィッティング パラメータ

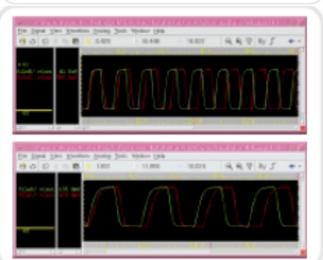

## ELDOの信頼性シミュレーション

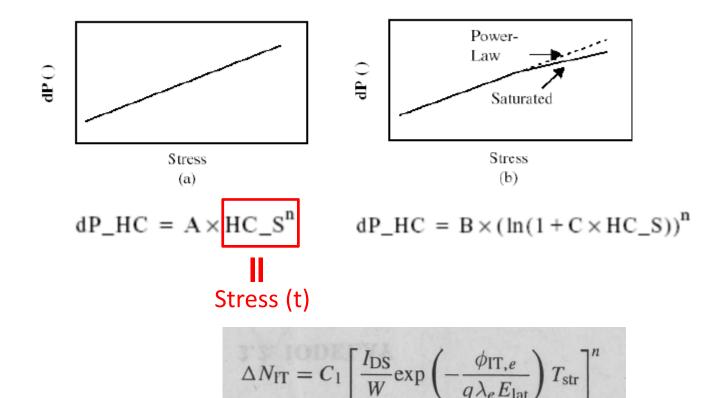

#### **HC update models**

- Different types of updating laws are commonly used :

- Linear

- Saturated

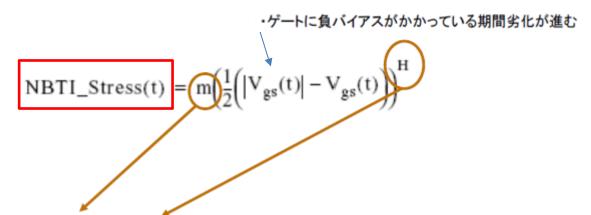

#### **NBTI** stress models

- Again, accurate models are proprietary

- Public models have simple form below :

In this equation, m and H are parameters of the stress model

#### **NBTI** update models

Typical update formula for VTH0 :

$$dP\_NBTI = A \times \underbrace{NBTI\_S^n} \times e^{\left(\frac{E_a}{KT}\right)}$$

$NBTI\_Stress(t)$

$A$  degradation constant.

$n$  degradation rate.

$Ea$  Thermal Activation energy.

$Ea$  Boltzman constant.

$Ea$  Temperature in degrees Kelvin.

Deep Submicron CMOS Integrated Circuit Reliability Simulation with SPICE

Xiaojun Li, B. Huang, J. Qin, X. Zhang, M. Talmor, Z.Gur, Joseph B. Bernstein 2110B Marie Mount Hall, Microelectronics Reliability Engineering University of Maryland, College Park, MD 20742 USA xjli@wam.umd.edu

$$\triangle V_{th} \propto V_{gs}^m t^n \exp(-\frac{E_a}{\kappa T})$$

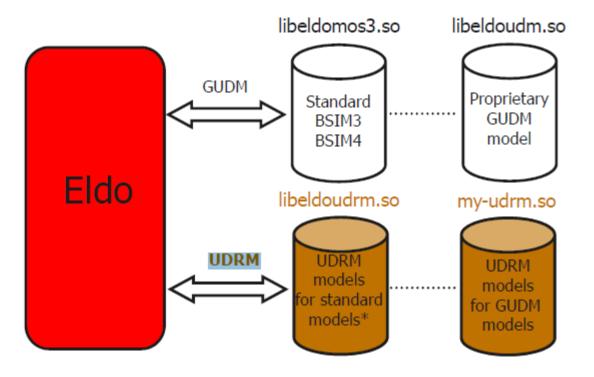

#### **Dedicated API: UDRM**

■ Models are coded in C, using the UDRM API

UDRM supports BSIM3, BSIM4, PSP and HiSIM

#### RelXpert

内部は一切明かさず、宣伝のみ、 同社のBSIMProPlusを導入しないと、 劣化モデルパラメータが抽出出来ない!

群馬大学大学院 電子情報部門 小林研究室 モデリンググループ

## 研究成果報告

## MOSFET信頼性モデリング関連の 研究関連実績

- 1. HCI 劣化モデルのBSIM4への適用研究

- 2. 分散,移動度変動,インターフェーストラップによる1/fノイズ劣化モデル研究・開発

- 3. VCO位相ノイズシミュレーションと回路最適 化研究

- 4. 90nm MOSFETのHCIゲートリーク電流による信頼性モデル研究

- 5. LDMOSのストレス電圧・温度によるドリフト抵抗劣化モデルの研究

### 論文·学会発表(1)

#### • 学術論文誌 3件

- 1. T. Totsuka, H. Aoki, F. Abe, K. Ramin, Y. Arai, S. Todoroki, M. Kazumi, M. Higashino, H. Kobayashi, "Bias and 1/f Noise Degradation Modeling of 90 nm n-Channel MOSFETs Induced by Hot Carrier Stress," Key Engineering Materials (2016)

- 2. Y. Arai, H. Aoki, F. Abe, S. Todoroki, R. Khatami, M. Kazumi, T. Totsuka, T. Wang, H. Kobayashi, "Gate Voltage Dependent 1/f Noise Variance Model Based on Physical Noise Generation Mechanisms in n-Channel Metal-Oxide-Semiconductor Field-Effect Transistors," Japanese Journal of Applied Physics, Mar. (2015)

- 3. H. Kobayashi, H. Aoki, K. Katoh, Congbing Li, "Analog/Mixed-Signal Circuit Design in Nano CMOS Era," IEICE Electronics Express, Vol.11, No.3, pp. 1-15, Feb. (2014).

## 論文·学会発表(2)

#### • 国際学会発表 8件

- 1. M. Higashino, H. Aoki, N. Tsukiji, M. Kazumi, T. Totsuka, S. Shibuya, K. Kurihara, R. Takahashi and H. Kobayashi, "Study on Hot Carrier Injection Model of LDMOS for Reliability Simulation," The 12th International Workshop on Radiation Effects on Semiconductor Devices for Space Applications & The 8th International Conference on Advanced Micro-Device Engineering, Dec. 9, 2016, Kiryu.

- 2. M. Higashino, H. Aoki, N. Tsukiji, M. Kazumi, T. Totsuka, S. Shibuya, K. Kurihara, H. Kobayashi, "Study on ON-Resistance Degradation Modeling Used for HCI Induced Degradation Characteristic of LDMOS Transistors," International Conference on Solid State Devices and Materials, Tsukuba, Sept. 2016.

- 3. T. Totsuka, H. Aoki, N. Tsukiji, M. Kazumi, M. Higashino, and H. Kobayashi, "Reliability Modeling on 90 nm n-channel MOSFETs with BSIM4 Dedicated to HCI Mechanisms," The 11th International Workshop on Radiation Effects on Semiconductor Devices for Space Applications & The 7th International Conference on Advanced Micro-Device Engineering, Nov. 11-13, 2015, Kiryu, P8-29.

- 4. N. Tsukiji, H. Aoki, M. Kazumi, T. Totsuka, M. Higashino, and H. Kobayashi, "A Study on HCI Induced Gate Leakage Current Model used for Reliability Simulations in 90nm n-MOSFETs," The 11th International Workshop on Radiation Effects on Semiconductor Devices for Space Applications & The 7th International Conference on Advanced Micro-Device Engineering, Nov. 11-13, 2015, Kiryu, P8-24. (AMDE Student Award受賞).

- 5. N. Tsukiji, H. Aoki, M. Kazumi, T. Totsuka, M. Higashino, and H. Kobayashi, "A Study on HCI Induced Gate Leakage Current Model Used for Reliability Simulations in 90nm n-MOSFETs," IEEE 11th International Conference on ASIC, Chengdu, China (Nov. 3-6, 2015). (Excellent Student Paper Award受賞).

- 6. M. Higashino, H. Aoki, N. Tsukiji, M. Kazumi, T. Totsuka, H. Kobayashi, "Study on Maximum Electric Field Modeling Used for HCI Induced Degradation Characteristic of LDMOS Transistors," IEEE 11th International Conference on ASIC, Chengdu, China (Nov. 3-6, 2015).

- 7. T. Totsuka, <u>H. Aoki</u>, F. Abe, K. Ramin, Y. Arai, S. Todoroki, M. Kazumi, W. Taifeng, H. Kobayashi, "BSIM4 Modeling of 90nm n-MOSFET Characteristics Degradation Due to Hot Electron," The 17th International Conference on Analog VLSI Circuits (AVIC2014), Ho Chi Minh City, Vietnam (Oct. 22-24, 2014).

- 8. Y. Arai, H. Aoki, F. Abe, S. Todoroki, R. Khatami, M. Kazumi, T. Totsuka, T. Wang, H. Kobayashi, "Gate Voltage Dependent 1/f Noise Variance Model in n-Channel MOSFETs," International Conference on Solid State Devices and Materials (SSDM2014), Tsukuba (Sept. 8-11, 2014).

#### • 国内学会 18件