#### **SEMICON JAPAN**

Intro

duction

# Successive Approximation Time-to-Digital Converter With Full Digital Self-Calibration

<sup>1)</sup>Yuki Ozawa, <sup>1)</sup>Congbing Li, <sup>1)</sup>Haruo Kobayashi, <sup>1)</sup>Nobukazu Tsukiji, <sup>2)</sup>Ryoji Shiota, <sup>1)</sup>Kazumi Hatayama

1) Gunma University 2) Socionext Inc.,

Time Input

#### **Our Target Application and Innovation Application:** High-speed I/O Interface Signal Timing Testing Start — Start→ Digital TDC Output Stop→ Stop-**Innovation:** Fine Time Resolution & High Linearity Timing Measurement Circuit with Full Digital Self-Calibration Method [CONVENTIONAL] [NEW] Nonlinear IDC Digital Out

#### **Research Objective**

- Delay T variation

- Relative variation

- TDC nonlinearity

- Absolute(average value) variation

- TDC input range & time resolution

- Focus on relative variation here.

### Our Approach

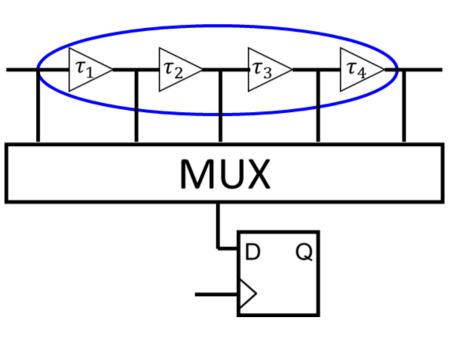

SAR-TDC with Histogram Method

- SAR TDC

- All Digital Circuit Small circuit Digital output **FPGA**

- Histogram Method

- High linearity

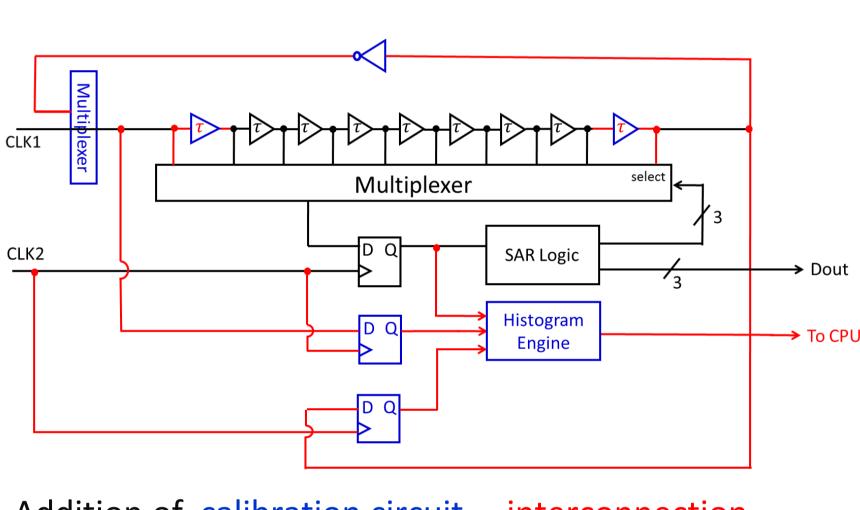

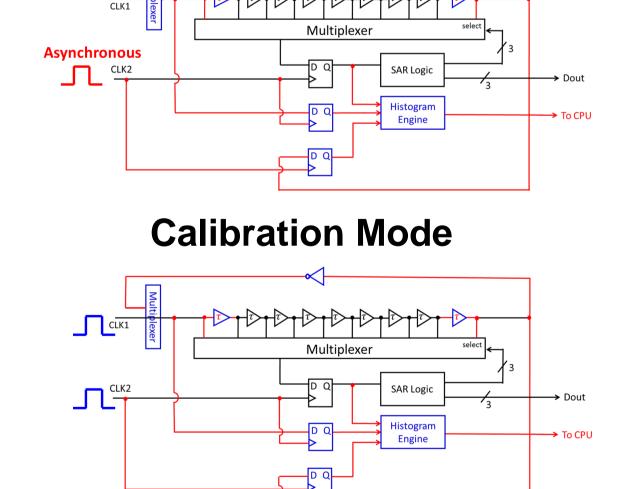

### **SAR-TDC Design with Calibration Circuit**

Time Input

SAR : Successive Approximation Register

Addition of calibration circuit, interconnection

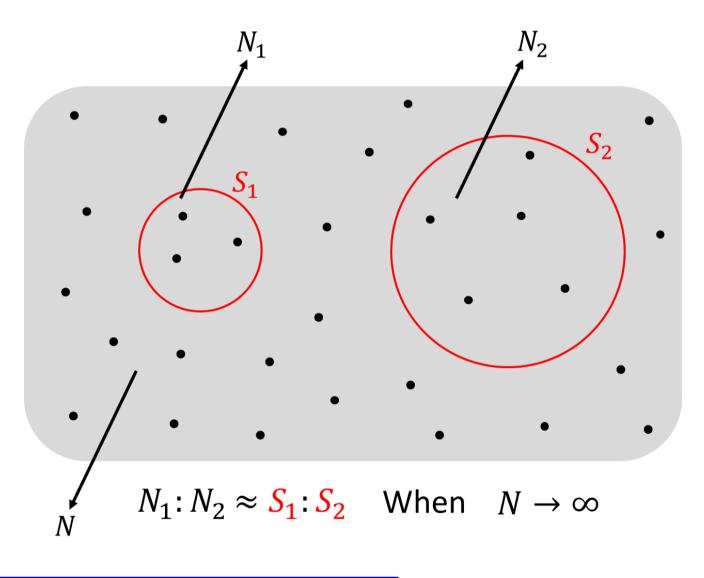

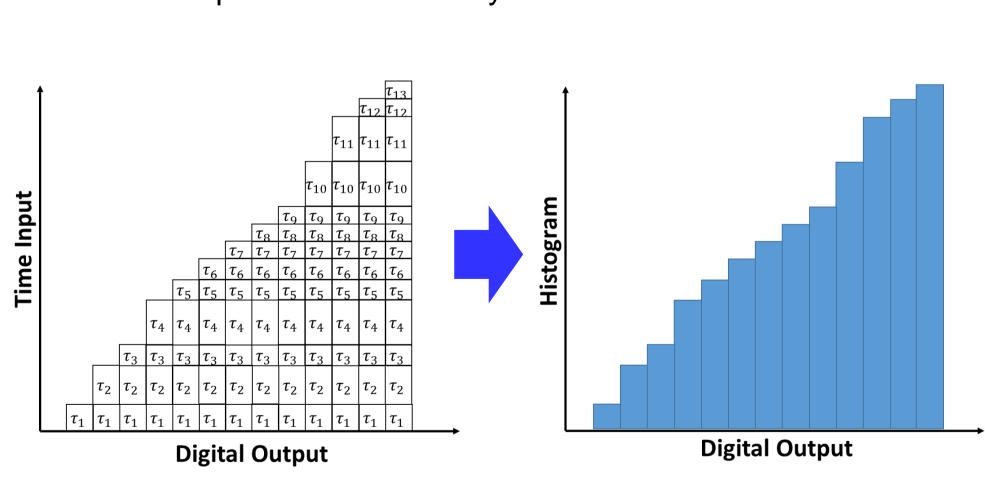

### Principle of Histogram Method

CLK1, CLK2 are NOT correlated. Random dots

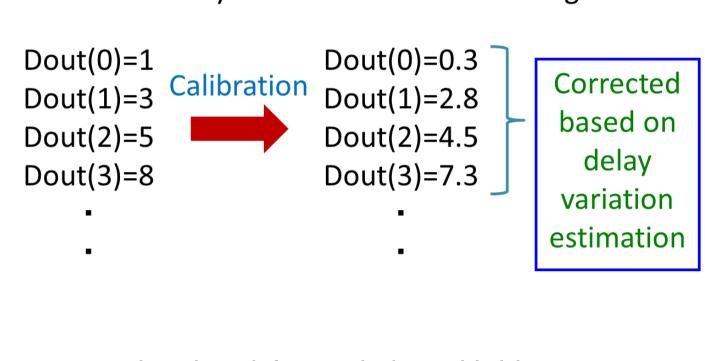

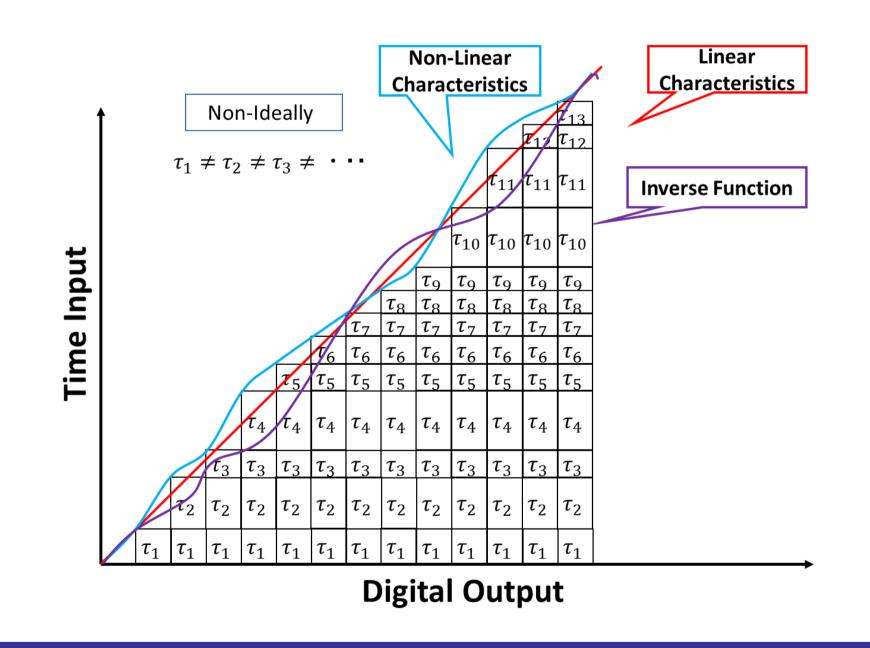

#### **Digital Error Correction**

TDC linearity self-calibration with histogram

estimating delay variation with histogram

correcting raw TDC digital output based on estimated data

### Consideration

### **Normal & Calibration Modes**

**Normal Operation Mode**

### **Measurement of Delay Values**

By statistical processing in Histogram Engine, it becomes possible to indirectly know TDC characteristics

### **Digital Correction of TDC Nonlinearity**

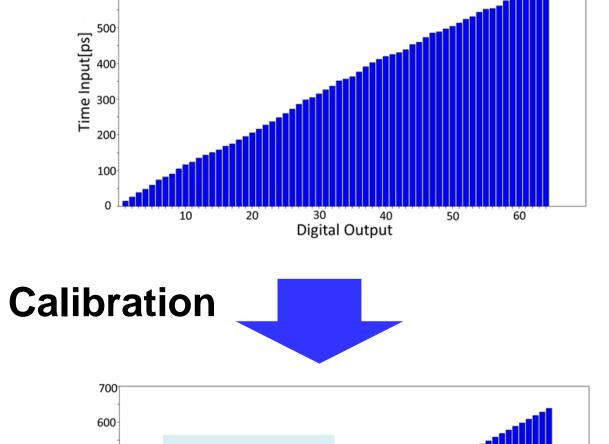

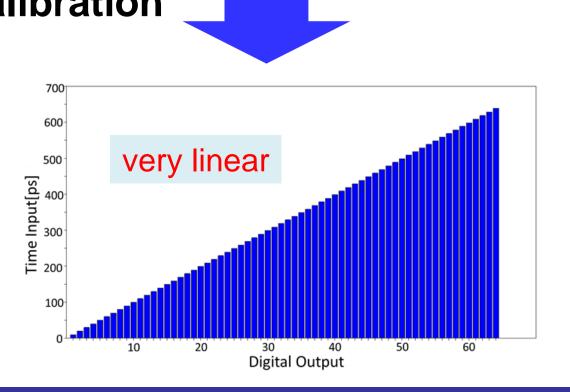

### **Simulation Results**

**Digital Output**

- After Calibration

- NO 0.2 Component Number

- **Before Calibration** INL=2.22LSB\*

- **After Calibration**

- INL=0.13LSB\*

**Before Calibration** DNL=0.76LSB\* **After Calibration**

DNL=0.02LSB\*

\*Worst Case

## Summary

- We have implemented SAR-TDC with self-calibration by simulation.

- We have confirmed its operation, and Histogram Method effectiveness.

- It can be timing testing BOST

- full digital

- suitable for FPGA implementation

- high linearity

- small circuit.

### References

- [1] T. Chujo, D. Hirabayashi, K. Kentaroh, et al.,

- "Experimental Verification of Timing Measurement Circuit With Self-Calibration",

- IEEE IMS3TW, Brazil (Sept. 2014).

- [2] R. Jiang, C. Li, M. Yang, H. Kobayashi, Y. Ozawa, R. Shiota, K. Hatayama, et al., "Successive Approximation Time-to-Digital Converter with Vernier-level Resolution",

- **IEEE IMSTW, Spain (July 2016).** [3] S. Ito, S. Nishimura, H. Kobayashi, et al.,

- "Stochastic TDC Architecture with Self-Calibration,"

- IEEE Asia Pacific Conf. Circuits and Systems, Kuala Lumpur, Malaysia (Dec. 2010).