# Self-Calibration and Trigger Circuit for Two-Step SAR TDC

Takashi Ida, Yuki Ozawa, Jiang Richen, Haruo Kobayashi, Ryoji Shiota School of Science and Technology, Gunma University

Socionext Inc., Kyoto, JAPAN

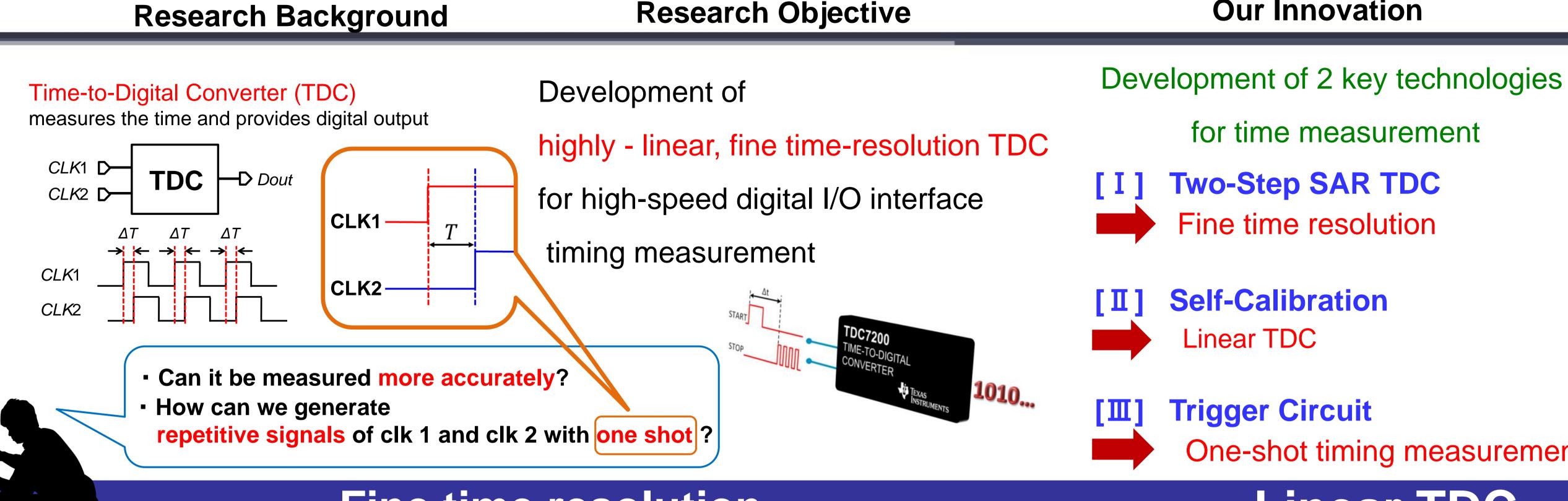

**Our Innovation**

for time measurement

Two-Step SAR TDC

Fine time resolution

**Self-Calibration**

Linear TDC

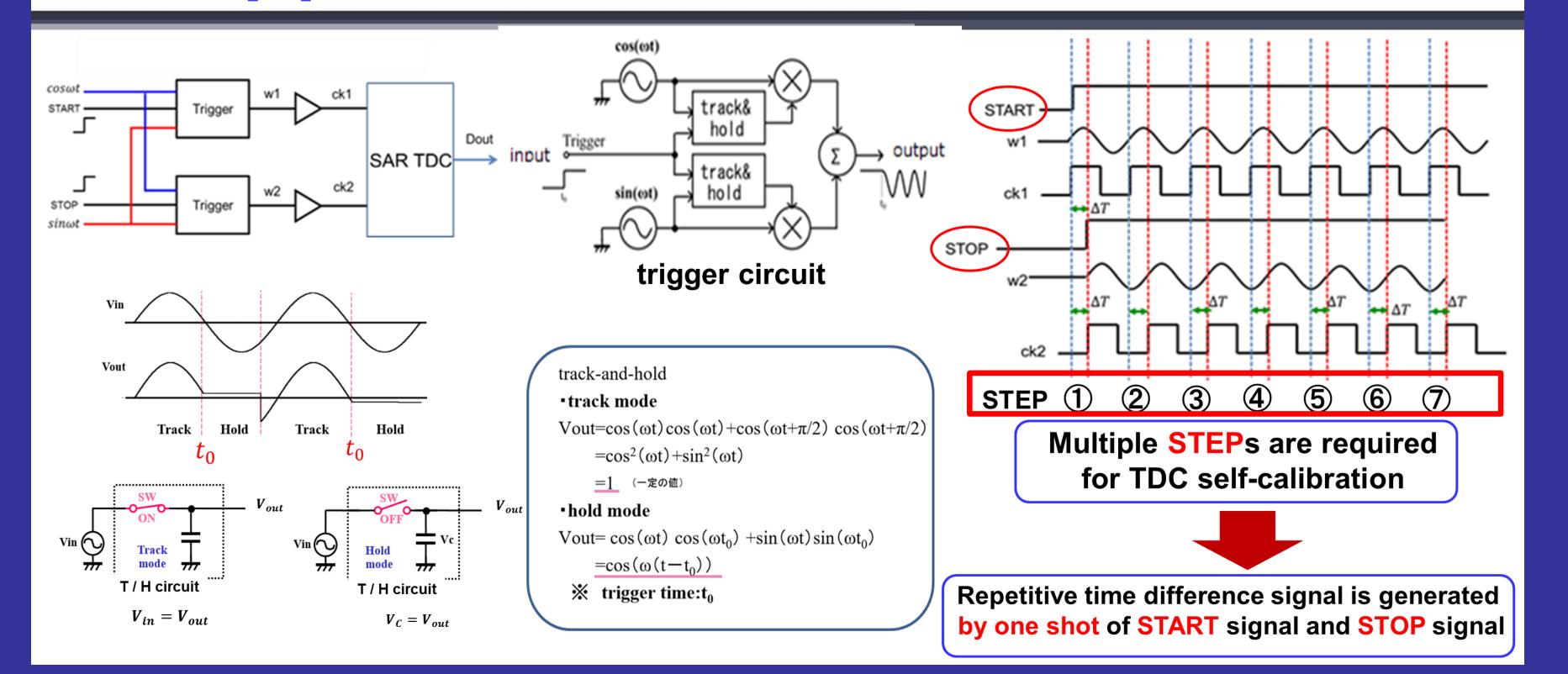

[III] Trigger Circuit

One-shot timing measurement

# Fine time resolution

$\Delta T = 4.3\tau$

based on binary search

Digital output

100

# Linear TDC

# [ I ] TDC operation

SAR Logic

by using buffer to delay the clock

Find the difference between clk 1 and clk 2

CLK1

STEP1

CLK2

AĮ AĮ AĮ CLK1 L L

Multiplexer

OP.1:Using 4 buffer  $\rightarrow$  1

OP.2:Using 6 buffer  $\rightarrow$  0

OP.3:Using 5 buffer  $\rightarrow$  0

$\Delta T = 4.3 \tau$

**Two-Step SAR TDC operation** (SAR TDC+Vernier type TDC)

3bit SAR+3bit SAR-Vernier TDC **Coarse TDC** SAR SAR TDC Time resolution: T1 **Fine TDC Buffer increase / decrease is** VernierTDC

> **OP.1:Using Coarse TDC(Time resolution T1) OP.2:Using 1/8 frequency divider** OP.3:Using Fine TDC(Time resolution τ1-τ2)

## [II] Calibration algorithm

**Explanation of the self-calibration algorithm** Average value  $[\tau]$  $n_{\blacksquare}$ ,  $m_{\blacksquare}$ :Output data  $T_{\blacksquare}$ : Known input data  $\tau' = n_A \tau_1 + m_A \tau_3 \cong T_1$  $\tau'' = n_B \tau_1 + m_B \tau_3 \cong T_2$  $\tau^{\prime\prime\prime} = n_C \tau_1 + m_C \tau_3 \cong T_3$ τ : The collected sample

Estimate the delay value of the actual delay element by increasing the number of samples

Error variation with respect to  $\tau_1$  (=1.0)

Input time difference

# Linear TDC

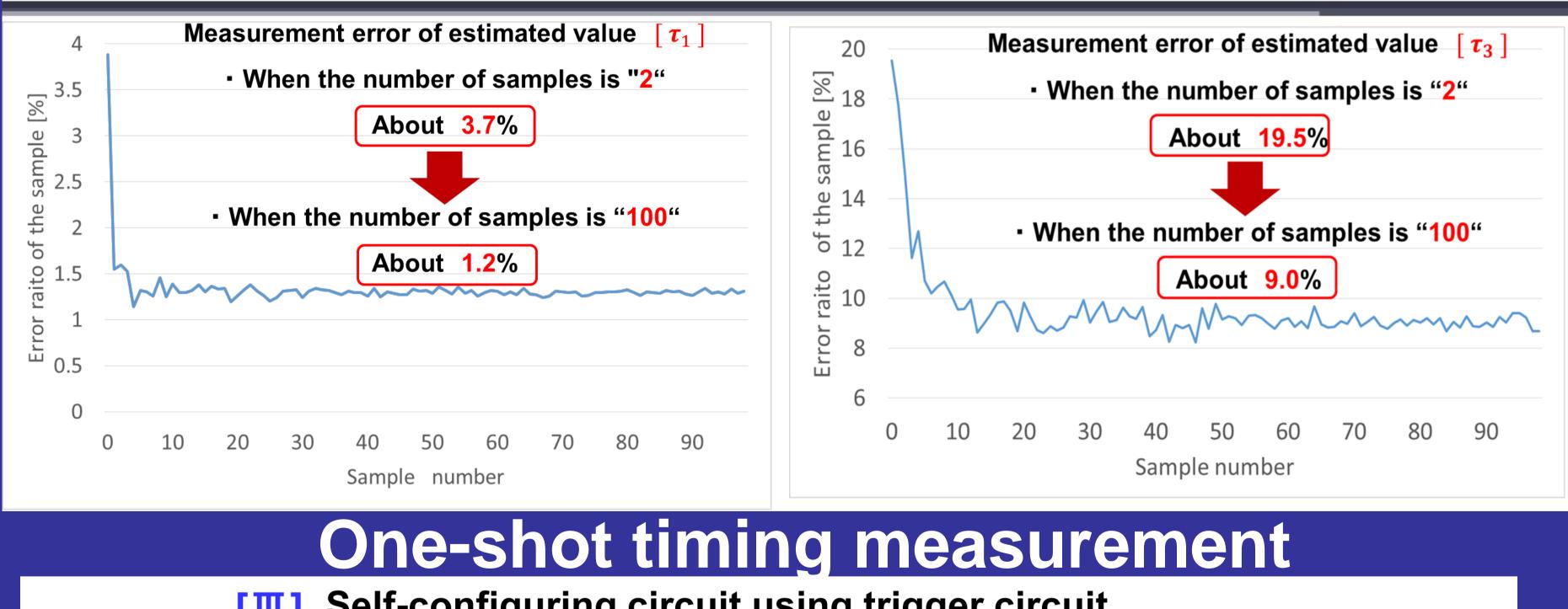

#### Simulation Result: Measurement error of estimated value

# Error variation with respect to $\tau_3$ (=0.1)

36%

Increased reliability by increasing the number of samples Sufficient reliability!

#### Self-configuring circuit using trigger circuit

# References

- [1] Y. Arai, T. Baba, "A CMOS Time to Digital Converter VLSI for High-Energy Physics", IEEE Symposium on VLSI **Circuits (1988).**

- [2] R. Jiang, C. Li, M. Yang, H. Kobayashi, et al., "Successive **Approximation Time-to-Digital Converter with Vernier-level** Resolution", IEEE IMSTW, Catalunyna, Spain (July 2016).

- [3] Tektronics, Automatic RF Techniques Group 56th **Measurement Conference - Metrology and Test for RF** Telecommunications, Boulder, Colorado (Dec. 2000).