Minimum or no chip area penalty for BIST

# SEMICON

# simultaneously.

SEMICON

ATE: Automatic Test Equipment Save or Earn BIST: Built-In Self-Test, BOST: Built-Out Self-Testy SEMICON

Extensive usage of BOST

SEMICON A penny saved is a penny earned.

# Test and Measurement are different

# Production Test : 100% Engineering

Decision of "Go" or "No Go" For example, it can be performance comparison between DUT and "Golden Device".

LSI testing is manufacturing engineering.

# Measurement : 50% Science, 50% Engineering

Accurate performance evaluation of circuit

Measurement can be costly, but testing should be at low cost.

DUT: Device Under Test

SEMICON

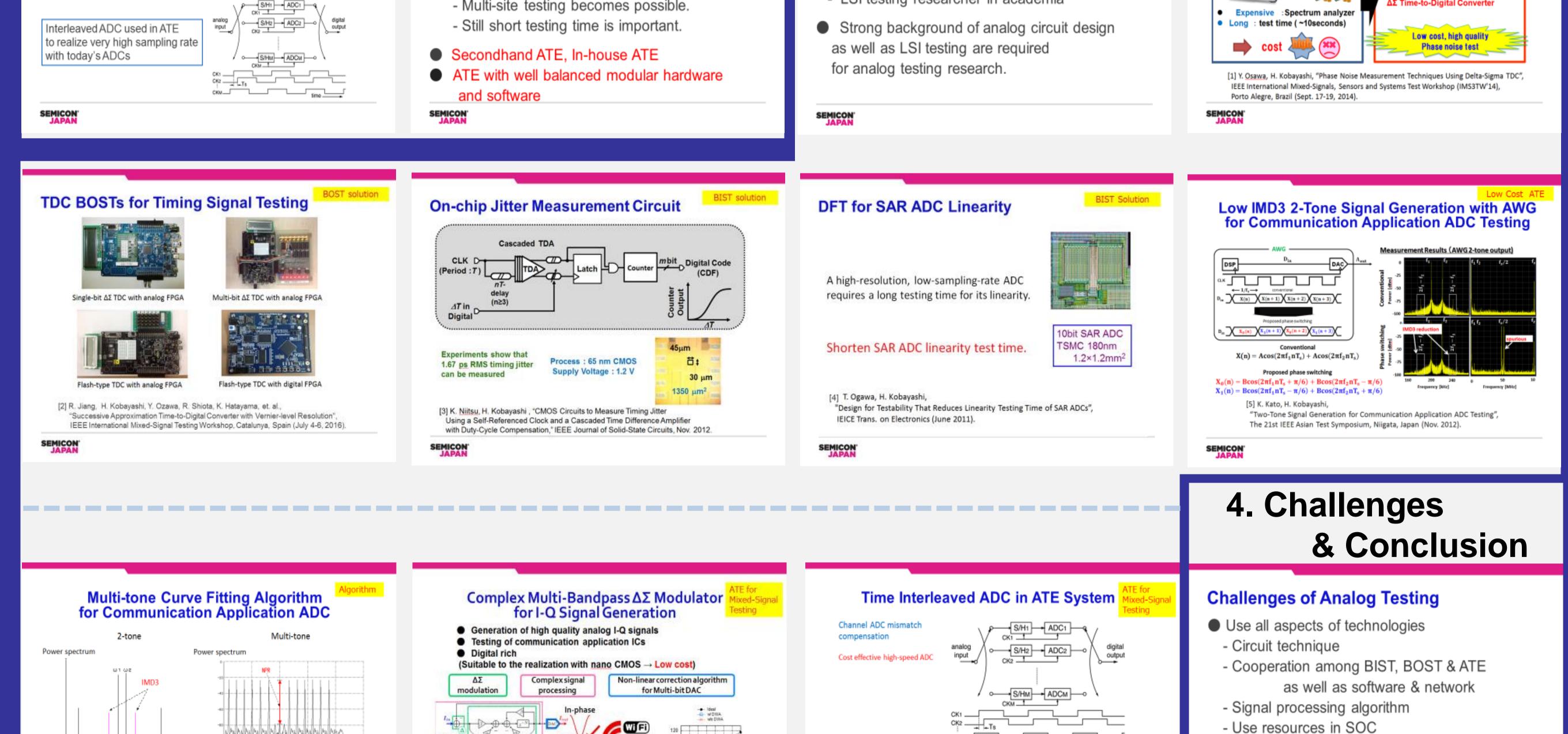

# Analog BIST

- BIST for digital : Successful BIST for analog : Not very successful Challenging research

- Digital test : Functionality Easy

Analog test : Functionality & Quality 🛁 Hard

Analog: parametric fault as well as fatal fault. Prof. A. Chatterjee Specification-based Test Alternative Test Defect-based Test

## In many cases

- Analog BIST depends on circuit.

- No general method like scan path in digital.

- One BIST, for one parameter testing

- SEMICON

- **RF / High-Speed IO / Power Device Testing**

- RF / HSIO / Power testing is different from analog testing technology.

- These testing technologies are other challenging areas.

- RF testing items examples:

- EVM test

- System level testing, GSM/EDGE

- AM/PM distortion

- Jitter, Phase noise

SEMICON

# **Robust Design and Testing**

# Robust design makes its testing difficult.

• Feedback suppresses parameter variation effects.

- Self-calibration and redundancy hide defects in DUT.

- Secure DUT is difficult to test.

Robust design (yield enhancement) and testing cost reduction are trade-off.

SEMICON

# **3. Research Topics**

for tomorrow's higher performance chip testing.

- Collaboration is important

- Circuit designer

- ATE manufacturer engineer

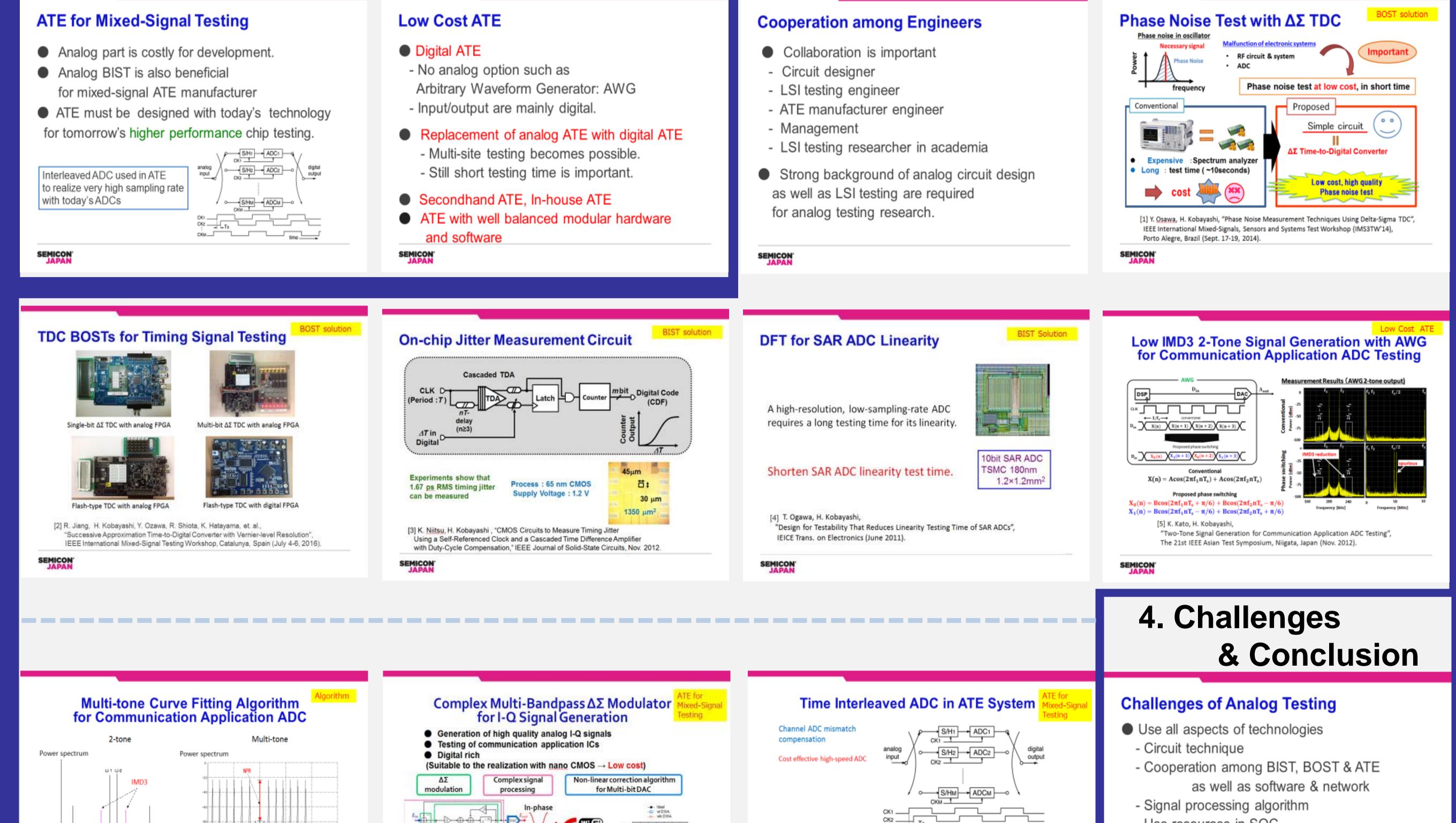

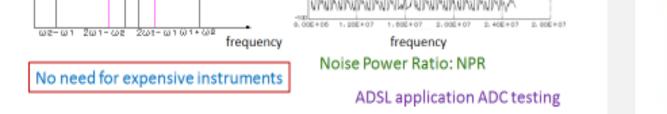

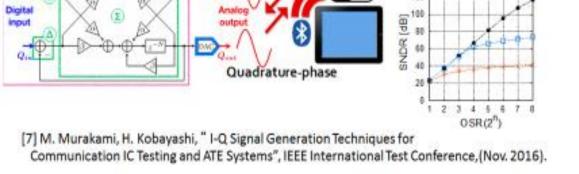

## [6] Y. Motoki, H. Kobayashi, "Multi-Tone Curve Fitting Algorithms for Communication Application ADC Testing", Electronics and Communication in Japan: Part 2, Wiley Periodicals Inc. (2003).

SEMICON

## [8] N. Kurosawa, H. Kobayashi "Explicit Analysis of Channel Mismatch Effects in Time-Interleaved ADC Systems", IEEE Trans. on Circuits and Systems I (March 2001).

## [9] R. Yi, H. Kobayashi,

Digital Compensation for Timing Mismatches in Interleaved ADCs", IEEE 22nd Asian Test Symposium, Yilan, Taiwan, (Nov. 2013) [10] K. Asami, H. Kobayashi, "Timing Skew Compensation Technique using Digital Filter with Novel Linear Phase Condition," IEEE International Test Conference, Austin (Nov. 2010).

such as µP core, memory, ADC/DAC

There is no science without measurement.

There is no production without test

No royal road to analog testing

SEMICON JAPAN